原文来自公众号:工程师看海

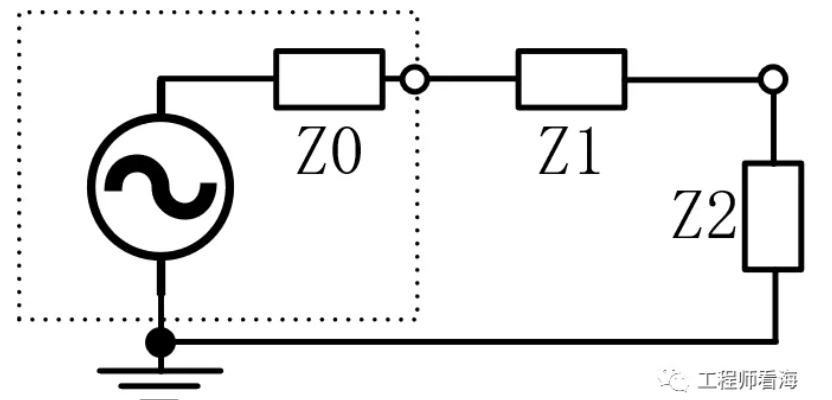

如下图所示,从信号源到传输线在到负载,一共有3个阻抗参数,一般而言信号源的阻抗是很小的,而负载的阻抗是非常大的,远大于Z1,那么信号就会在源端和接收端直接来回反射,详细的过程在以前《反射与反弹图》文章中有过更详细的介绍,当时提到过一个概念叫做“源端端接有效”,根据这个概念,不管是在源端还是在接受端,只要其中任意一端实现阻抗控制,那么就可以避免反射,由此引入今天的主题:端接电阻缓解阻抗突变,抑制反射。

有两种端接方法最常见:

源端串联电阻,即串联端接,使源端阻抗与传输线阻抗匹配。

接收端并联电阻,即并联端接,是接收端阻抗与传输线匹配。

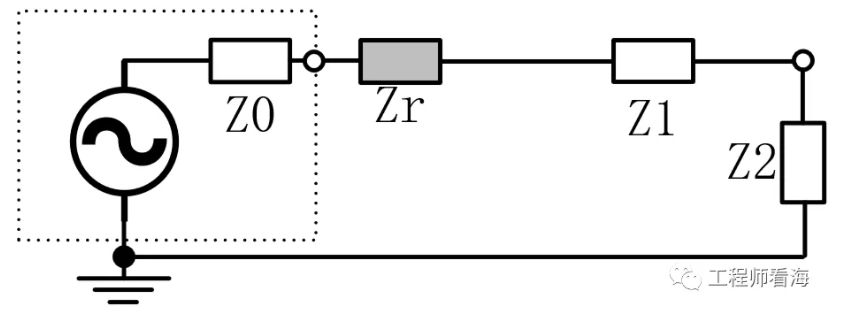

串联端接

下图是串联端接的示意图,在靠近源端串联一个小电阻,信号是以半幅度经过Zr和传输线Z1到达接收端Z2,接收端Z2的阻抗非常大,信号会发生一次全反射,只是这种反射回到源端后由于Zr的存在,反射程度会被降低。如果没有Zr的话,信号会在源端和接收端来回反射,Zr缓解了这个现象。

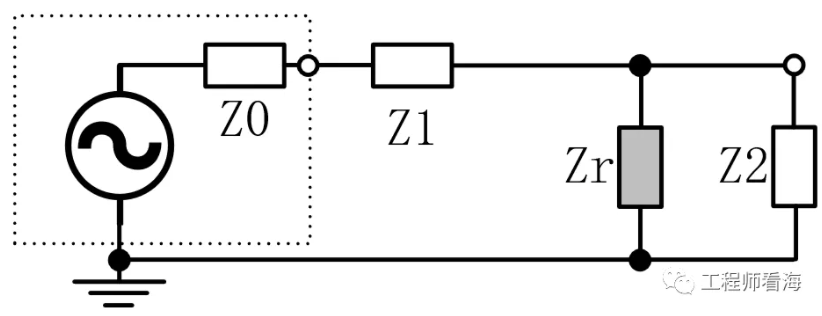

并联端接

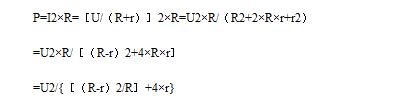

下图是并联端接的示意图,在靠近接收端并联一个电阻,信号到达接收端后,由于Zr=Z1,信号不发生反射,信号是以全幅度从源端出来经过传输线Z1到达接收端,反射程度会被降低。如果没有Zr的话,信号会在源端和接收端来回反射,Zr缓解了这个现象。

串联端接的特点是功耗低,不会给驱动端增加额外的直流负载,信号以半幅度传播。

并联端接的特点是会增加额外的功耗,信号以接近满幅度传播。

如果同学们理解了上面的介绍,那么就应该会有这样的疑问:

为什么有的信号端串联了一个小电阻,但是这个信号并不是高速信号?

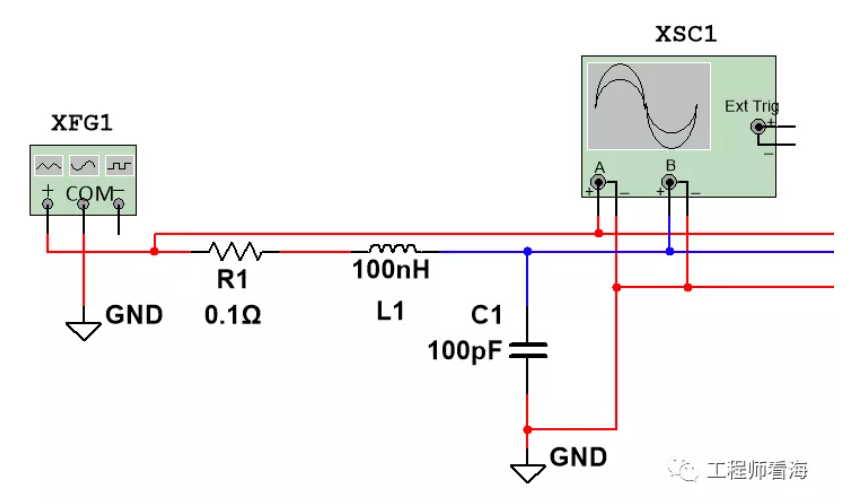

这是因为由于走线具有寄生电容和寄生电感,当走线比较糟糕时,寄生参数就大,容易引起RLC谐振,使得信号也有振铃现象。

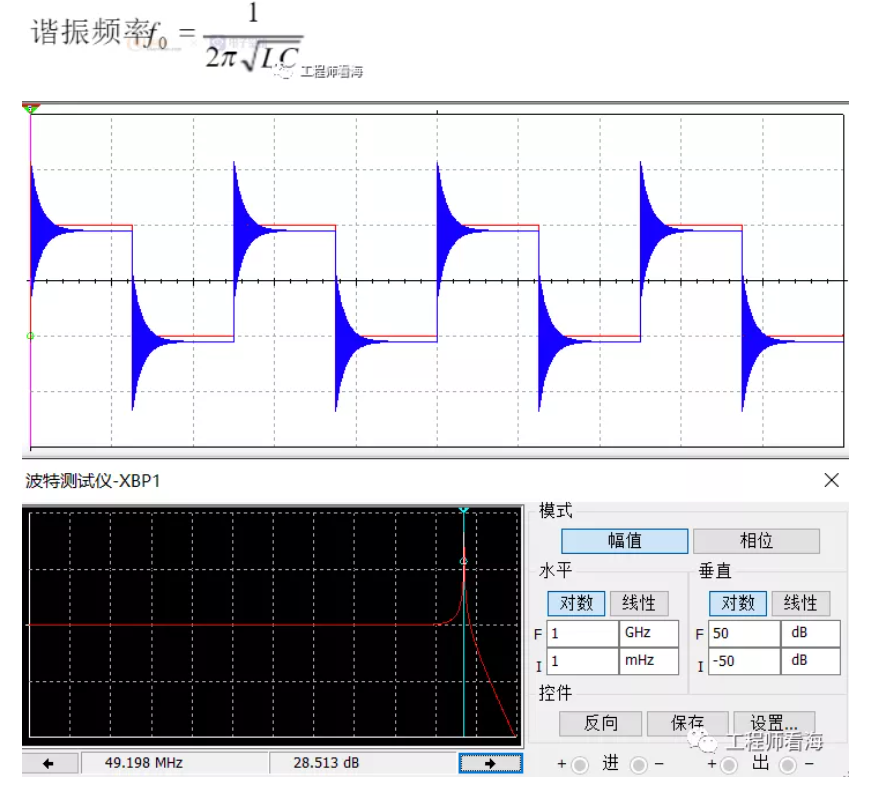

假如走线电容R=0.1Ω,走线寄生电感=100nH,寄生电容=100pF。谐振频率大约是50Mhz。

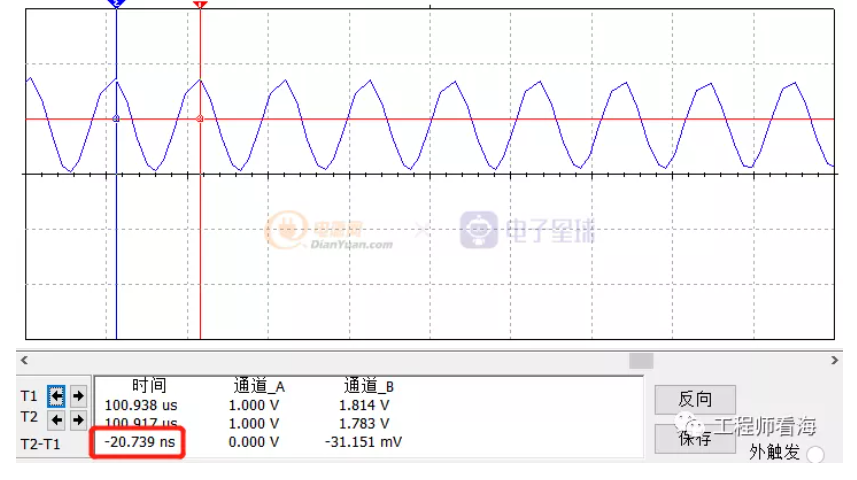

放大蓝色振铃,波形可以看到振铃的频率就是50Mhz,

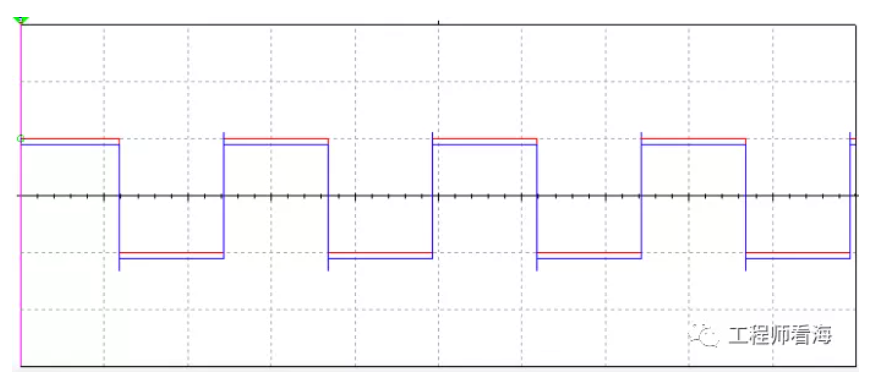

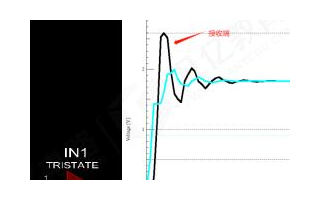

如果在线路上串联一个33Ω电阻吸收震荡,则震荡就会小很多。所以从形式上看,谐振和阻抗不匹配都会引起振铃现象,但原理还有一定差异,我们平时用示波器测纹波时,要减小探头的环路电感,来减小振铃就是这个道理。

感谢点赞、分享、在看,让知识变得更简单

限时免费扫码进群,交流更多行业技术

推荐阅读▼

电池、电源

硬件文章精选

华为海思软硬件开发资料

-

串联

+关注

关注

6文章

450浏览量

39831 -

电阻

+关注

关注

88文章

5814浏览量

179931 -

阻抗

+关注

关注

17文章

993浏览量

49497 -

信号处理

+关注

关注

49文章

1160浏览量

105246 -

信号完整性

+关注

关注

68文章

1497浏览量

98241

发布评论请先 登录

怎样理解阻抗匹配_pcb阻抗匹配如何计算

阻抗匹配的四种处理方式

阻抗匹配的原理及应用

传输线在阻抗匹配时串联端接电阻为什么要靠近发送端?

为什么要阻抗匹配?怎么进行阻抗匹配?

端接电阻与阻抗匹配那些事

端接电阻与阻抗匹配那些事

评论