以太网PHY是什么?

从硬件上来说,一般PHY芯片为模数混合电路,负责接收电、光这类模拟信号,经过解调和A/D转换后通过MII接口将信号交给MAC芯片进行处理。一般MAC芯片为纯数字电路。

物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。物理层的芯片称之为PHY。

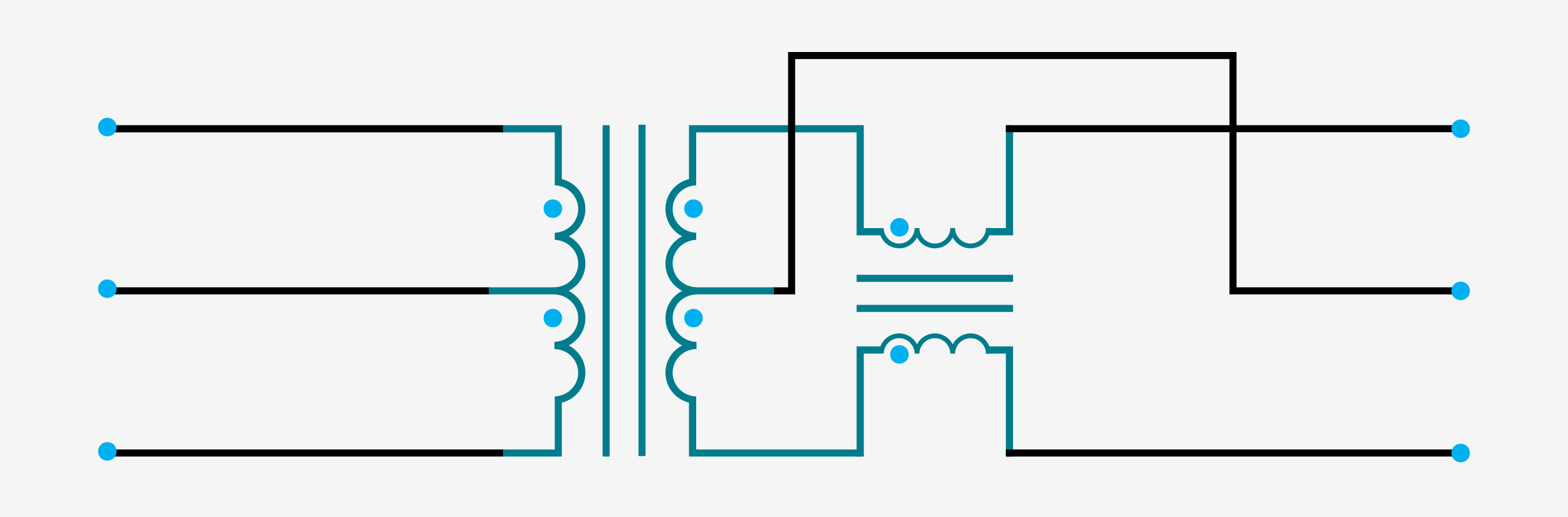

PHY是物理接口收发器,它实现物理层.IEEE-802.3标准定义了以太网PHY.包括MII/GMII(介质独立接口)子层,PCS(物理编码子层),PMA(物理介质附加)子层,PMD(物理介质相关)子层,MDI子层。它符合IEEE-802.3k中用于10BaseT(第14条)和100BaseTX(第24条和第25条)的规范。

PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据而不管什么地址,数据还是CRC.对于100BaseTX因为使用4B/5B编码,每4bit就增加1bit的检错码),然后把并行数据转化为串行流数据,再按照物理层的编码规则把数据编码,再变为模拟信号把数据送出去。

收数据时的流程反之.PHY还有个重要的功能就是实现CSMA/CD的部分功能。它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。

如果两个碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。

这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突。

关于phy芯片 以RTL8211E(G)为例

PHY是IEEE802.3中定义的一个标准模块,STA(station management entity,管理实体,一般为MAC或CPU)

通过SMI(Serial Manage Interface)对PHY的行为、状态进行管理和控制,而具体管理和控制动作是通过读写PHY内部的寄存器实现的。

PHY寄存器的地址空间为5位,从0到31最多可以定义32个寄存器

所讨论的RTL8211EG地址位是由001 - 111,由硬件配置,不同phy芯片配置有所不同,详细需要阅读芯片手册

CSDN,博客园,凡有等待就有启程综合整理

审核编辑 :李倩

-

芯片

+关注

关注

463文章

54443浏览量

469437 -

收发器

+关注

关注

10文章

3839浏览量

111463 -

PHY

+关注

关注

2文章

341浏览量

54328

发布评论请先 登录

网络变压器PHY匹配与共模抑制设计:从中心抽头到EMI优化

千兆网络变压器选型实战:从PoE等级到PHY匹配的完整技术手册

Voohu:以太网PHY芯片与磁性元件的阻抗匹配及接法规范

千兆网络变压器选型实战指南:PoE等级、封装温度与PHY芯片匹配要点2纪要

千兆网络变压器选型实战指南:PoE等级、封装温度与PHY芯片匹配要点

VOOHU沃虎电子:PHY与以太网交换芯片技术选型解析

秒懂!电流型VS电压型PHY芯片,电子人必知的网口核心芯片差异

电压驱动型PHY vs. 电流驱动型PHY:如何正确连接网络变压器?

NXP TJA1104:引领汽车以太网PHY新潮流

极细同轴线束在MIPI D-PHY与C-PHY中的选型要点解析

移植网络PHY芯片驱动,如何融入 rt-thread 的网络体系,并添加新的以太网类型的报文?

MIPI A-PHY量产上车!车载SerDes竞争格局进入新时代

一站式定制芯片及IP供应商灿芯半导体推出PCIe 4.0 PHY IP

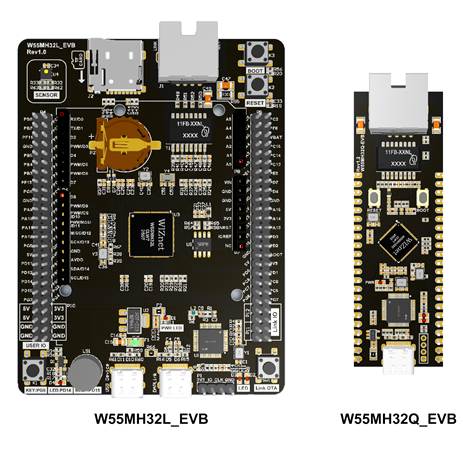

第二十一章 W55MH32 PHY配置示例

phy芯片的作用

phy芯片的作用

评论