异构计算已经成了半导体业界不得不思考的一个话题,传统通用计算的性能捉襟见肘,过去承诺的每隔一段时间芯片性能翻倍的豪言壮语已经没有人再提了。如今我们用到的手机中,各种除CPU以外的计算单元层出不穷,无论是神经网络处理器还是图像处理器。

异构计算的存在可以说创造了另一个维度,这个维度上我们又有了堆性能的空间,小至手机SoC、汽车芯片,大到服务器芯片和超算处理器,异构带来了更大的算力。但与此同时,异构计算也带来了一些潜在的问题。

异构计算的崛起

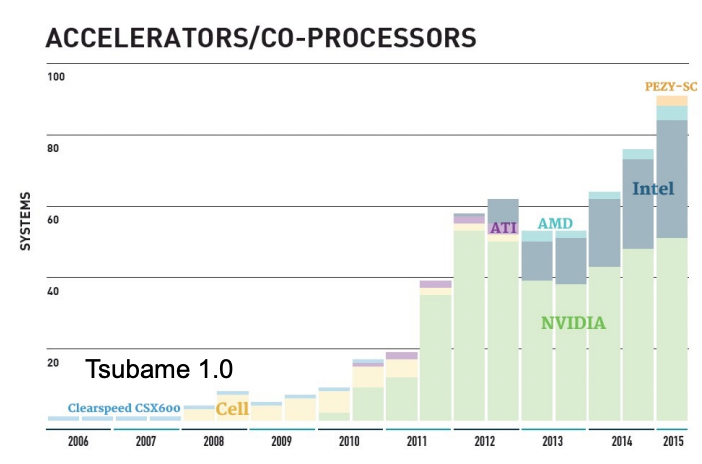

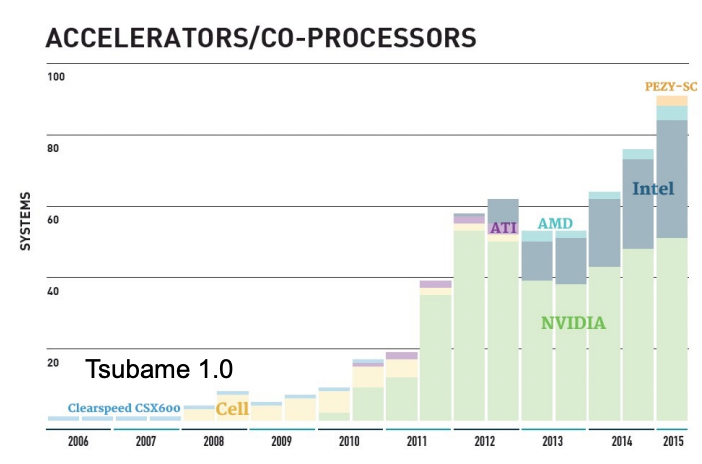

异构计算其实早在计算机时代的早期就开始零星出现了,比如英特尔在80年代推出的浮点协处理器(FPU)i487,Inmos./ST在1996年推出的多媒体加速器Chameleon等等。转眼进入了新世纪,异构出现的频率也越来越高,2010年苹果推出了首个自研的处理器A4,将CPU、GPU和其它加速器集成至一起。在超算领域,加速器和协处理器也数量也在逐步增加。

全球超算系统加速器/协处理器的应用趋势 / TOP500

2020年以后,各国的超级计算机计划都定位在了Exascale的百亿亿级别,要想实现目标,要么靠堆核心规模来堆性能,要么就是选择异构计算。如今前十的超算系统中,有一半以上都采用了CPU+GPU的异构设计。

明眼人都能看出,这种CPU+GPU的异构设计也开始变得愈发紧密,比如英伟达今年宣布的Arm CPU Grace,该处理器靠着英伟达专利互联技术NVLink的加持,成功将CPU与GPU之间的互联速度做到了夸张的900GB/s,是传统PCIe的10倍以上,CPU更是靠LPDDR5X实现了500GB/s的内存带宽。

非传统的架构更是层出不穷,Graphcore的IPU、谷歌的TPU、矢量引擎和FPGA等等,相信XPU的命名形式马上就要用完26个字母了。促使大家选择异构的动力究竟是什么?答案很简单,异构给到了一个更高效的方案,能够实现的算力更高。既然你CPU在计算上落后了,我GPU自然要上位,更何况我还有这么多成熟的I/O和互联技术为我撑腰。

异构计算真就完美无缺?

异构计算就真的如此完美吗?并非如此。异构计算的存在其实也引出了不少隐患,比如极度差异化的编程模型,从过去的单向编程转为了多向编程。因为异构系统中存在多个计算设备,又有着不同的系统架构、指令集和编程模型,因此异构系统的编程与传统的CPU编程相比有很大的差距。通常来说,异构混合计算系统需要多套不同的代码,这增大了应用开发的难度,纸面参数是好看了,却苦了软件开发者。

IPU / Graphcore

其次,GPU、FPGA和AI处理器厂商都推出了截然不同的加速器方案,这些方案不仅仅采用了自己专用的处理器架构,还有自己的执行指令和编译器。在这样不统一的架构下,将并行程序移植到异构处理器上需要的可不只是重新编译,还有代码重写。也正因如此,HPC的代码生态虽然不弱,但近半数以上可能永远都不会被移植到其他加速器上,甚至这一部分工作量还分摊到了加速器厂商的软件开发工作量上。

所以,必须得使用优秀的软件栈,这样才能让开发者充分利用异构处理器的计算资源,而不用在编程时考虑复杂的硬件细节。现在已经有了不少跨平台的编程标准,比如C++/Fortran、OpenMP、SYCL和Kokkos等。

最后是复杂的数据存取过程,异构带来的不仅是不同层级的计算架构,还有不同层级的存储架构,比如主存储、主缓存、设备主存、设备缓存和寄存器等等。数据要在多种存储类型之间移动,程序执行要在同时对多种存储进行存取,这些存储方式的带宽和延迟也不尽相同。

异构计算的未来

在近期举办的CIUK 2021大会上,HPC研究组的Simon McIntosh-Smith教授发表了他自己对异构计算未来的看法。他认为异构计算的趋势还将继续发展下去,差异化不会消失,但也不会出现极度差异化的情况。

其次CPU与GPU的关系将更加紧密,比如缓存一致和封装集成等,其他加速器在特定场景下声称的性能数据都很优秀,但要说通用计算性能,GPU还是要略胜一筹。而且依目前的趋势来看,CPU也在慢慢汲取GPU上的优点,比如HBM、宽矢量处理器的核心、核心内部的加速器等等。编程的困境固然已经有了改善的迹象,但还有一段长路要走。

异构计算的存在可以说创造了另一个维度,这个维度上我们又有了堆性能的空间,小至手机SoC、汽车芯片,大到服务器芯片和超算处理器,异构带来了更大的算力。但与此同时,异构计算也带来了一些潜在的问题。

异构计算的崛起

异构计算其实早在计算机时代的早期就开始零星出现了,比如英特尔在80年代推出的浮点协处理器(FPU)i487,Inmos./ST在1996年推出的多媒体加速器Chameleon等等。转眼进入了新世纪,异构出现的频率也越来越高,2010年苹果推出了首个自研的处理器A4,将CPU、GPU和其它加速器集成至一起。在超算领域,加速器和协处理器也数量也在逐步增加。

全球超算系统加速器/协处理器的应用趋势 / TOP500

2020年以后,各国的超级计算机计划都定位在了Exascale的百亿亿级别,要想实现目标,要么靠堆核心规模来堆性能,要么就是选择异构计算。如今前十的超算系统中,有一半以上都采用了CPU+GPU的异构设计。

明眼人都能看出,这种CPU+GPU的异构设计也开始变得愈发紧密,比如英伟达今年宣布的Arm CPU Grace,该处理器靠着英伟达专利互联技术NVLink的加持,成功将CPU与GPU之间的互联速度做到了夸张的900GB/s,是传统PCIe的10倍以上,CPU更是靠LPDDR5X实现了500GB/s的内存带宽。

非传统的架构更是层出不穷,Graphcore的IPU、谷歌的TPU、矢量引擎和FPGA等等,相信XPU的命名形式马上就要用完26个字母了。促使大家选择异构的动力究竟是什么?答案很简单,异构给到了一个更高效的方案,能够实现的算力更高。既然你CPU在计算上落后了,我GPU自然要上位,更何况我还有这么多成熟的I/O和互联技术为我撑腰。

异构计算真就完美无缺?

异构计算就真的如此完美吗?并非如此。异构计算的存在其实也引出了不少隐患,比如极度差异化的编程模型,从过去的单向编程转为了多向编程。因为异构系统中存在多个计算设备,又有着不同的系统架构、指令集和编程模型,因此异构系统的编程与传统的CPU编程相比有很大的差距。通常来说,异构混合计算系统需要多套不同的代码,这增大了应用开发的难度,纸面参数是好看了,却苦了软件开发者。

IPU / Graphcore

其次,GPU、FPGA和AI处理器厂商都推出了截然不同的加速器方案,这些方案不仅仅采用了自己专用的处理器架构,还有自己的执行指令和编译器。在这样不统一的架构下,将并行程序移植到异构处理器上需要的可不只是重新编译,还有代码重写。也正因如此,HPC的代码生态虽然不弱,但近半数以上可能永远都不会被移植到其他加速器上,甚至这一部分工作量还分摊到了加速器厂商的软件开发工作量上。

所以,必须得使用优秀的软件栈,这样才能让开发者充分利用异构处理器的计算资源,而不用在编程时考虑复杂的硬件细节。现在已经有了不少跨平台的编程标准,比如C++/Fortran、OpenMP、SYCL和Kokkos等。

最后是复杂的数据存取过程,异构带来的不仅是不同层级的计算架构,还有不同层级的存储架构,比如主存储、主缓存、设备主存、设备缓存和寄存器等等。数据要在多种存储类型之间移动,程序执行要在同时对多种存储进行存取,这些存储方式的带宽和延迟也不尽相同。

异构计算的未来

在近期举办的CIUK 2021大会上,HPC研究组的Simon McIntosh-Smith教授发表了他自己对异构计算未来的看法。他认为异构计算的趋势还将继续发展下去,差异化不会消失,但也不会出现极度差异化的情况。

其次CPU与GPU的关系将更加紧密,比如缓存一致和封装集成等,其他加速器在特定场景下声称的性能数据都很优秀,但要说通用计算性能,GPU还是要略胜一筹。而且依目前的趋势来看,CPU也在慢慢汲取GPU上的优点,比如HBM、宽矢量处理器的核心、核心内部的加速器等等。编程的困境固然已经有了改善的迹象,但还有一段长路要走。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

异构

+关注

关注

0文章

45浏览量

13491 -

异构计算

+关注

关注

2文章

110浏览量

17025

发布评论请先 登录

相关推荐

热点推荐

芯片装甲的前世今生

一前言众所周知,晶圆的特性如同玻璃一样容易破碎,但为什么做成成品的IC又能通过高震动与跌落可靠性测试,并且能在高温环境下非常稳定运行?这其实是一个关键的半导体技术——封装的功劳。它像一道“防护城墙”,既要屏蔽灰尘、水汽、冲击,也要兼顾散热、电性能和成本。在如今人人都知道先进半导体工艺已经先进到2nm的今天,对于不起眼的封装技术,却鲜有人熟知。接下来,让我们从

【TEC100TAI-KIT】青翼凌云科技基于JFMQL100TAI的全国产化智能异构计算平台

TEC100TAI-KIT是一款基于国产100TAI的全国产智能异构计算平台开发套件,该套件包含1个100TAI核心板和1个PCIE规格的扩展底板。

该套件的核心板集成了100TAI的最小

PCIe协议分析仪能测试哪些设备?

PCIe协议分析仪能测试多种依赖PCIe总线进行高速数据传输的设备,其测试范围覆盖计算、存储、网络及异构计算等多个领域,具体设备类型及测试场景如下:一、核心计算设备

GPU(图形处理器)

测试

发表于 07-25 14:09

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 异构架构下的智能边缘计算标杆

璞致电子推出PZ-ZU15EG-KFB异构计算开发板,搭载Xilinx ZYNQ UltraScale+ XCZU15EG芯片,整合四核ARM Cortex-A53、双核Cortex-R5F

智能安防边缘计算的技术解析

维度,剖析核心板如何推动安防从"被动记录"到"主动决策"的升级,并给出选型建议。 --- 一、核心板的硬件架构创新** 1. 异构计算架构:算力与能效的平衡 以SSD2351为例,其采用**"CPU+NPU+IVE"三级计算架构**: - **CPU**(双

异构计算构建更智能、更高效的AI未来

人工智能 (AI) 不再只是一个科研课题,它已然成为我们日常生活的一部分。从个性化医疗、智能可穿戴设备,到沉浸式数字娱乐以及自主机器人,AI 正在重塑我们生活、工作和创新的方式。然而,随着 AI 应用日益复杂,底层的基础设施也必须随之不断演进。

异构计算解决方案(兼容不同硬件架构)

异构计算解决方案通过整合不同类型处理器(如CPU、GPU、NPU、FPGA等),实现硬件资源的高效协同与兼容,满足多样化计算需求。其核心技术与实践方案如下: 一、硬件架构设计 异构处理器组合 主从

如何释放异构计算的潜能?Imagination与Baya Systems的系统架构实践启示

报告作者:PallaviSharma,Imaginaiton产品管理总监Dr.EricNorige,BayaSystems首席软件架构师关注Imagination公众号,消息框发送【异构计算】,即可

能效提升3倍!异构计算架构让AI跑得更快更省电

电子发烧友网报道(文/李弯弯)异构计算架构通过集成多种不同类型的处理单元(如CPU、GPU、NPU、FPGA、DSP等),针对不同计算任务的特点进行分工协作,从而在性能、能效和灵活性之间实现最优平衡

Imagination与澎峰科技携手推动GPU+AI解决方案,共拓计算生态

近日,ImaginationTechnologies与国内领先的异构计算软件与智算混合云服务提供商澎峰科技(PerfXLab)正式签署合作备忘录(MoU),围绕GPU与AI的深度融合展开合作。双方将

全志科技多核异构SoC助力行业智能化创新

近日, “第十二届开源操作系统年度技术会议”在北京举行,全志科技受邀参会。会上,全志进行了题为《多核异构SoC在行业应用中软件方案的思考与实践》的分享。分享从市场和技术洞察、方案设计创新、场景化应用落地三个维度展开系统性分享,全面展现了全志科技在异构计算领域的技术积累与行

RAKsmart智能算力架构:异构计算+低时延网络驱动企业AI训练范式升级

在AI大模型参数量突破万亿、多模态应用爆发的今天,企业AI训练正面临算力效率与成本的双重挑战。RAKsmart推出的智能算力架构,以异构计算资源池化与超低时延网络为核心,重构AI训练基础设施,助力企业实现训练速度提升、硬件成本下降与算法迭代加速的三重突破。

RK3399处理器:高性能多核异构计算平台

RK3399是一款高性能的多核异构计算平台,集成了强大的CPU、GPU以及丰富的多媒体和接口功能。其独特的双Cortex-A72+四Cortex-A53大小核CPU结构,使得RK3399在处理复杂

异构计算的概念、核心、优势、挑战及考虑因素

异构计算就像是一支由“多才多艺”处理器组成的团队,每个成员都有自己的强项和责任。 什么是异构计算 “异构计算”指的是在同一个计算平台中,部署多种不同类型的处理单元(比如

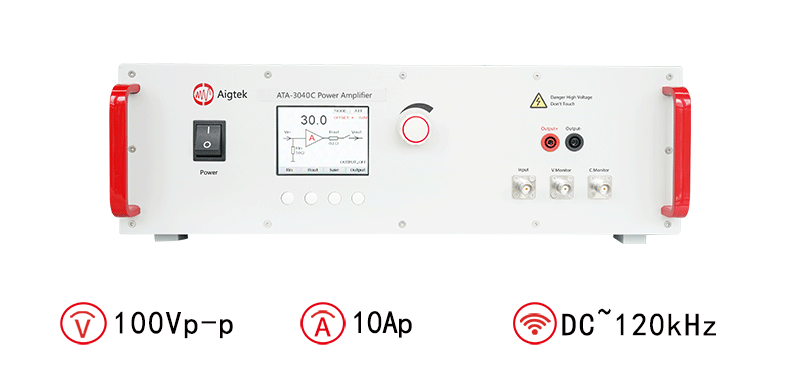

安泰功率放大器应用:纳米材料的前世今生

,因此在各个领域具有广泛的应用前景。那么你知道纳米材料是如何被发现,又是如何走入我们的生活,获得长足发展的吗?今天Aigtek安泰电子带大家详细了解一下。 纳米材料的前世今生 1861年,随着胶体化学的建立,科学家们开始了对直径为

异构计算的前世今生

异构计算的前世今生

评论