换流回路中的杂散电感会引起波形震荡,EMI或者电压过冲等问题。因此在电路设计的时候需要特别留意。本文给出了电路杂散电感的测量方法以及模块数据手册中杂散电感的定义方法。

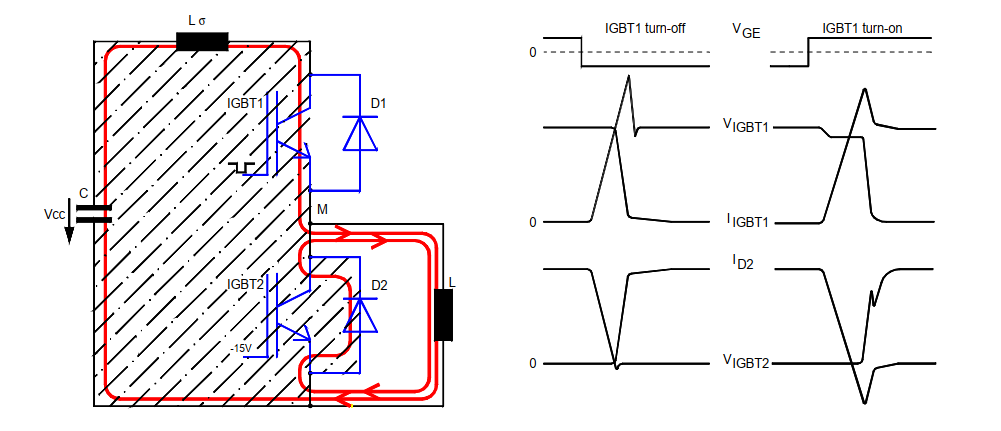

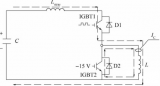

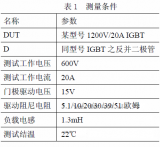

图1为半桥电路的原理电路以及开关上管IGBT1时产生的电压和电流波形。作为集中参数显示的电路杂散电感Lσ,代表了整个回路(阴影区域)中的所有的分布电感(电容器、母线和IGBT模块)。

半桥电路以及开关IGBT1时的电流和电压波形

由于电流的变化,在杂散电感Lσ上产生了Lσ*dioff/dt的电压降。它叠加在DC-link电压Vcc上,被看作是关断IGBT1时的电压尖峰。根据RBSOA图,该尖峰电压必须限制在IGBT模块的阻断电压VCES内(芯片上测量,在CE辅助端子上测量)。此外,考虑到模块主端子和辅助端子之间的杂散电感,在数据手册中给出了一条降额曲线,用于在功率端子上测量电压时使用。

通过IGBT导通时,集电极的电压降可以推导出整个回路的杂散电感:当IGBT处于阻断状态且电流已经上升时,可以测量di/dt和电压降ΔV,并根据公式Lσ=ΔV/di/dt计算得到电感。

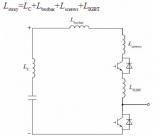

模块内部杂散电感计算值在数据手册中会给出。对于单管模块,这个值就是之前提到的主功率和辅助端子之间的杂散电感;对于半桥模块或者是有多个桥臂的模块,这个值表示跟应用相关的上管和下管换流回路。因为模块结构不同,这个值肯定会比单独测量上下管电感之和低。对于含有多个桥臂的模块,从电源到桥臂再回到负电源的情况最坏的换流回路需要被考虑。

根据模块类型的定义,数据手册上的杂散电感值应该做如下解释:

单管模块类型FZ

模块杂散电感通过CE主端子之间测量

半桥模块类型FF(带有三个主端子)

数据手册的杂散电感值包含从上管到下管整个回路,从上管C1到下管E2的电感值。

H桥模块类型F4

这类模块包含两个独立的桥臂。数据手册的杂散电感值包含一个桥臂从上管到下管整个回路,从正极到负极端子。

三相全桥模块或者PIM类型FS/FP

这类模块数据手册的杂散电感值是指最坏情况下从上管到下管整个回路的电感值,从P+到N-端子

设计杂散电感是变频器产品研发环节中非常重要的一个环。除了前期的计算和仿真之外,实际测量也是非常有必要的。特别是要模拟现场多种的恶劣工况,如低温,过压,大电流等;防止现场功率器件超过安全工作区导致失效。

责任编辑:haq

责任编辑:haq

-

电流

+关注

关注

40文章

7227浏览量

141605 -

电感

+关注

关注

54文章

6293浏览量

106650 -

IGBT

+关注

关注

1291文章

4452浏览量

264406

原文标题:IGBT换流回路中杂散电感的测量

文章出处:【微信号:yflgybdt,微信公众号:英飞凌工业半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

杰盈通讯JY-VLFG-2250+:2.25GHz低通滤波器——射频系统的“杂散劝退师”

800V总线杂散电感(Ls)提取:利用双脉冲测试波形反推回路参数的深度分析与计算公式

基本半导体1200V工业级碳化硅MOSFET半桥模块Pcore 2系列介绍

赛米控丹佛斯DCM1000X系列产品如何实现低杂散电感设计

无杂散、50 MHz 至 2.1 GHz 单通道小数 N 分频频率合成器 skyworksinc

模块数据手册中杂散电感的定义方法

模块数据手册中杂散电感的定义方法

评论