超越摩尔,三星的异构集成之路

在近期举办的2021年SamsungFoundry论坛上,三星透露了2/3nm制程工艺的新进展,并公开发布了全新的17nm工艺。三星市场战略副总裁MoonSoo Kang也面向产业合作伙伴,公布了三星在异构集成上的计划,如何为摩尔定律再度添加一个“维度”。

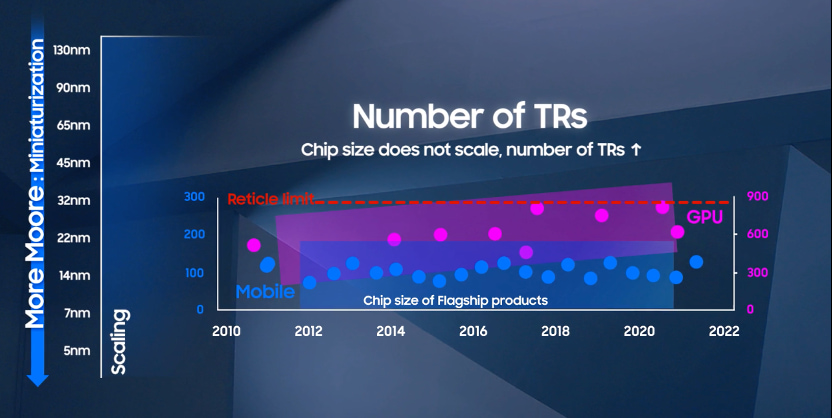

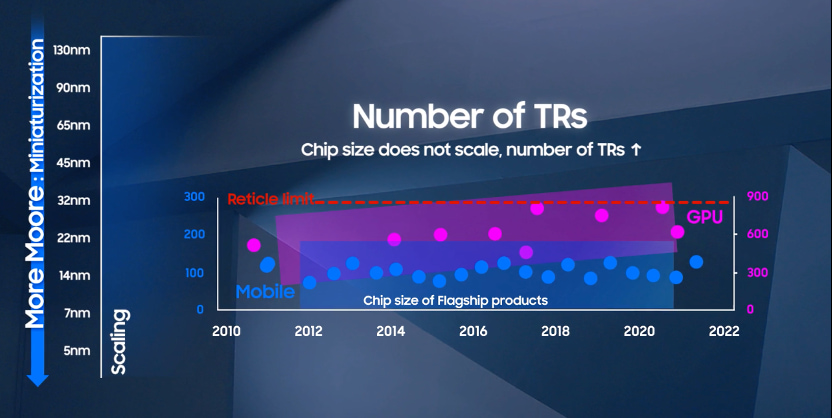

旗舰GPU与移动芯片的面积变化对比 / 三星

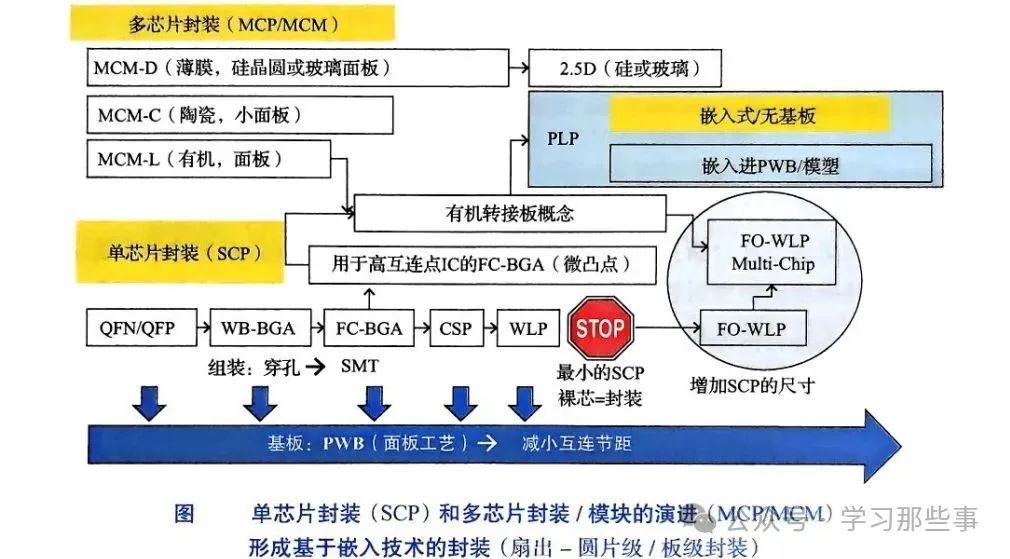

几十年间,半导体产业一直在不懈地推动摩尔定律,以更先进的制程做到更多的晶体管数目,这就是我们常说的“延续摩尔”方案,也是当前计算与电路领域持续创新最大的推动力。

尽管摩尔定律的延续,芯片面积仍在扩大,比如一直在追求算力的GPU,已经快要逼近光罩尺寸的限度了。再加上晶体管数目的增加,使得芯片设计成本和生产成本无休止地增加。在不少人看来,单靠“延续摩尔”不再是一个技术与成本上可持续的方案。

与此同时,更多的功能与特性集成在单个芯片上,却又没有单个制程可以满足所有不同功能的需求,比如模拟、射频、高压等,即便可以满足也无法达到优秀的性能与成本平衡。“延续摩尔”的方案在这类挑战面前束手无策,因此才出现了异构集成这种“扩展摩尔”的方案。通过两种方案的互补,共同做到“超越摩尔”。

Chiplet:降低成本提高良率的救星

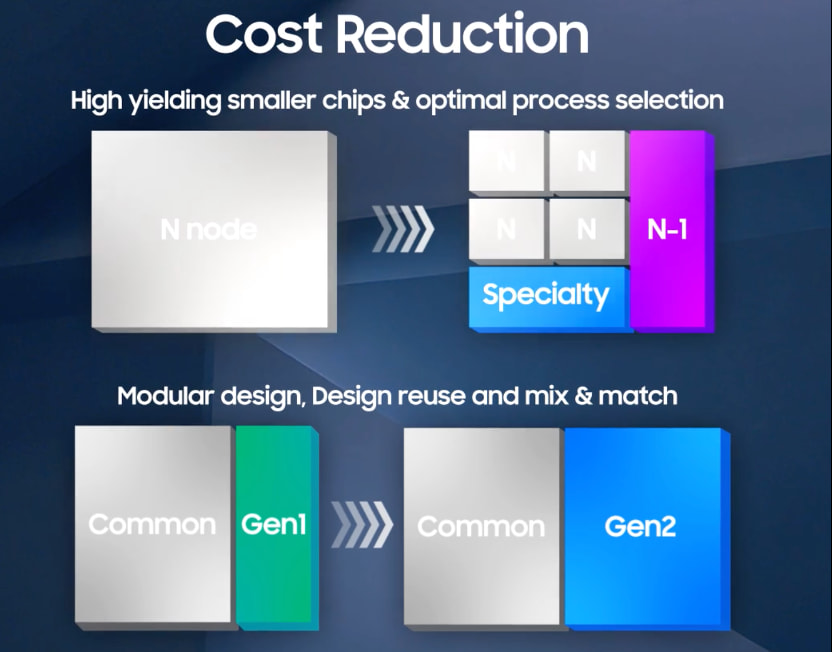

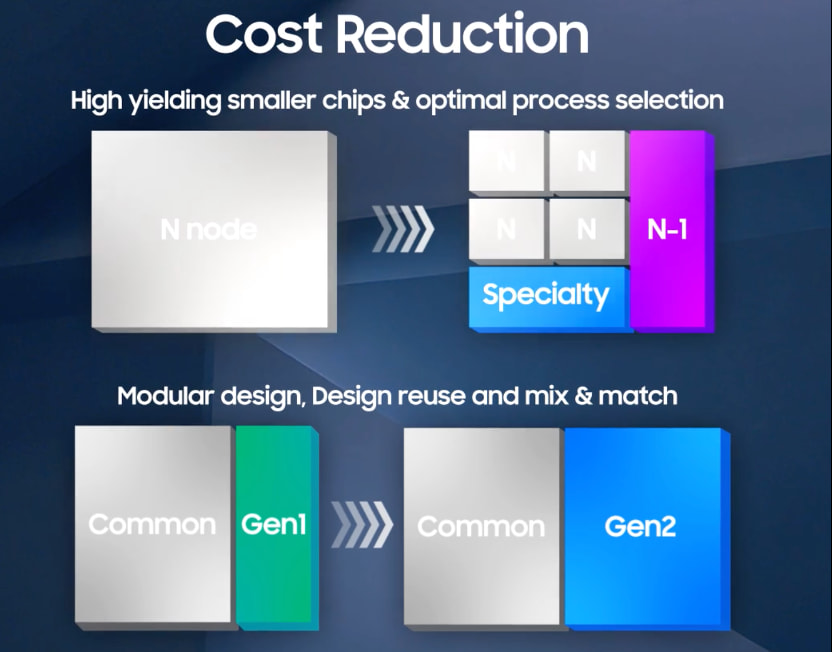

随着单个芯片加入更多特性,即便摩尔定律延续下去,其芯片面积仍在增加,为所有不同功能的设计区块使用同一个制程节点成了抵消的选择,好在如今有了Chiplet这一救星的出现。将一大块裸片分成较小的chiplet,并为每个chiplet使用最优的制程,可以显著提高整个芯片的良率,同时减少生产成本。例如某些特定的接口IP并不会因为采用先进制程而获得面积或性能上的优化,对这些IP使用成熟制程和专用定制制程,可以做到更低的成本以及更优的性能。

Chiplet方案 / 三星

另一个可行方案就是模组化的设计与制造,也就是重复使用相同的组件chiplet。不少IP模组都可以作为chiplet重复使用,只有芯片的其他部分需要重新设计和生产,此举显著减少了设计、开发与生产的成本,芯片厂商可以借此更快实现产品迭代。

X-Cube:垂直3D集成

异构集成不只是为了成本和良率考虑,也能进一步提升芯片性能。传统的2D设计中,信号路径有几毫米长。而在3D集成下,芯片的堆叠可以将信号路径减少至几微米,大大改进了芯片延迟。除此之外,3D集成中更出色的内联间距可以实现更高的带宽,进一步提高芯片性能。

早在2014年,三星就首次实现了将宽IO内存与移动应用处理器的3D堆叠,也就是三星的Widcon技术。随后,3D芯片堆叠技术继续发展,诞生了一系列HBM内存产品。HBM就是由DRAM与逻辑堆叠,并由微凸块和TSV相连而成的。也正是因为3D堆叠技术,三星得以开发出了3层的CMOS图像传感器,由图像传感器、逻辑与DRAM三种不同的裸片堆叠在一起而成。

2020年,三星推出了X-Cube技术,这项技术使得两个逻辑单元裸片可以垂直堆叠在一起,形成一个单独的3D芯片,由微凸块与TSV连接。X-Cube分为两种形式,两个裸片由微凸块连接或是直接铜键合。

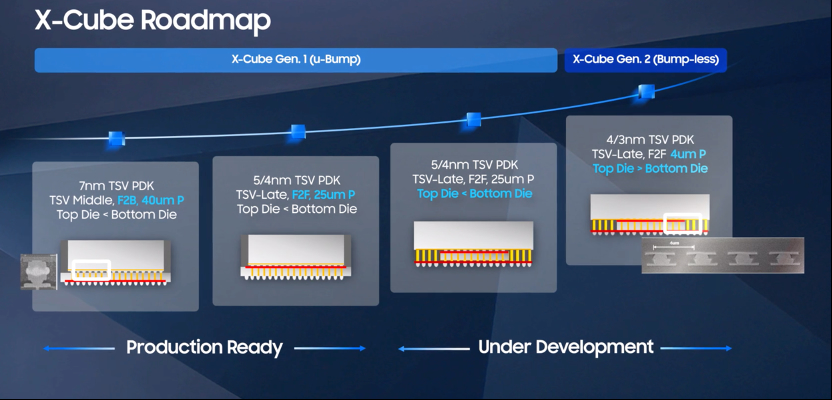

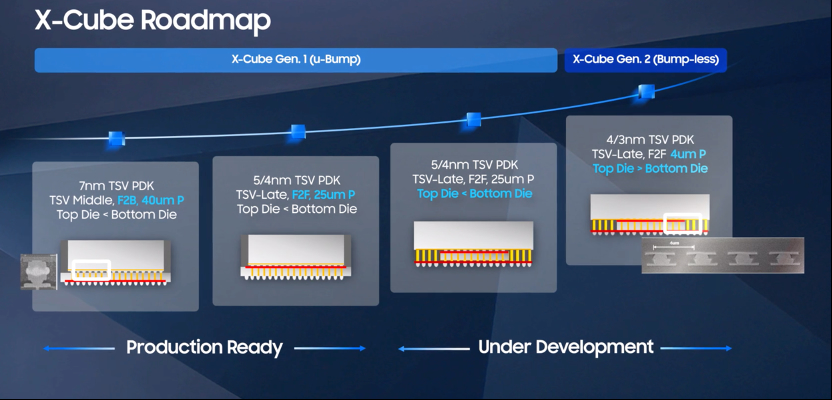

X-Cube路线图 / 三星

第一代X-Cube技术(u-Bump)主要依靠微凸块连接,三星已经发布了针对7nm逻辑制程的TSV PDK,采用F2B结构,凸块间距为40um。面向4/5nm的TSV PDK也已经发布,改用F2F的结构,凸块间距降低至25um。尚在开发中的第二代X-Cube技术(Bump-less)则采用了直接铜键合技术,间距降低至4um。

值得一提的是,英特尔的Foveros3D堆叠技术路线与三星X-Cube大致相同。第一代Foveros的凸块间距在36um至50um之间,而下一代FoverosOmni技术同样可以做到25um的凸块间距。尚在开发的Foveros Direct也采用了直接铜键合的方式,宣称凸块间距降低至10um以下。

过去的X-Cube架构中,底部裸片的面积要大于顶部裸片,然而为了更好了满足客户对芯片分区和散热等不同要求,三星也将在后续提供顶部裸片大于底部裸片的结构。目前三星已经完成了3D堆叠SRAM的验证,在7nm的制程下,可以做到48.6GB/s的带宽,以及7.2ns的读取延迟与2.6ns的写入延迟。

除此之外,三星还提供了一项差异化技术,ISC(集成堆叠电容)。这一电容应用了已经在三星DRAM产品中获得验证的硅电容结构、材料和工艺,具有1100nF/mm2的电容密度,可以有效提高电源完整性。三星的ISC还提供了多种不同的配置,比如分立型、硅中介层型和多晶圆堆叠型,以满足客户不同的结构需求,ISC预计将在2022年进入量产阶段。

I-Cube:横向2.5D组合

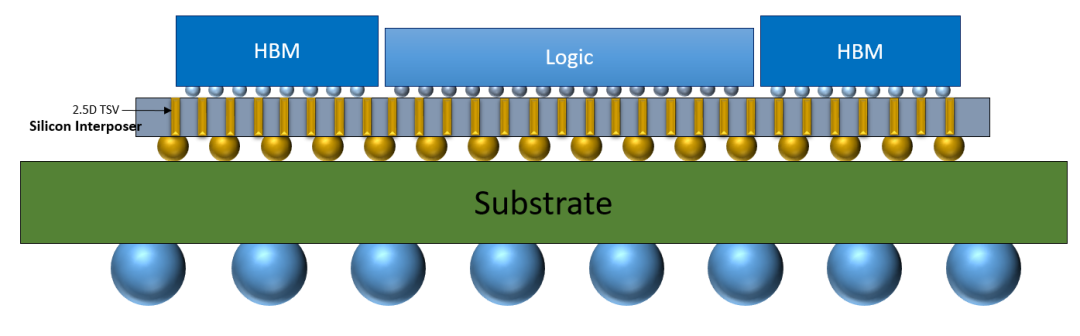

另一方面,为了从横向组合芯片,三星开发了所谓的2.5D技术I-Cube,将逻辑单元与多个HBM集成在同一硅中介层上。目前三星已经成功实现了一个逻辑裸片+两个HBM的I-Cube2量产,成品之一就是百度的昆仑AI芯片。百度的昆仑AI芯片不仅使用了三星的14nm制程,也运用了三星的I-CUBE 2技术。

I-Cube使用了预筛选的技术,在封装的中间阶段进行运算测试,从而提高良率。该技术还采用了无封胶的结构,做到更好的散热性能,据三星强调,与传统的2.5D方案相比,I-Cube的散热效率高上4.5%。此外,与其他代工厂商相比,三星的I-Cube技术还有一些优势,比如与三星内存合作,率先用上最新的内存方案

I-Cube4示意图 / 三星

目前三星已经在计划集成4HBM3模组的I-Cube4量产工作,而6 HBM的I-Cube6也已经做好量产准备,前者预计2022年进入大批量产阶段。三星更是准备了两个逻辑裸片+8个HBM的I-Cube8方案,目前尚处于开发阶段,预计2022年末将正式上线。

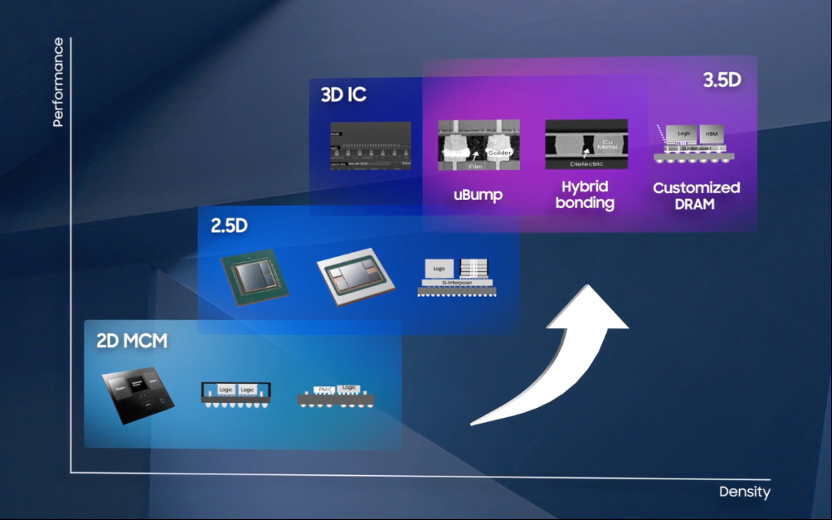

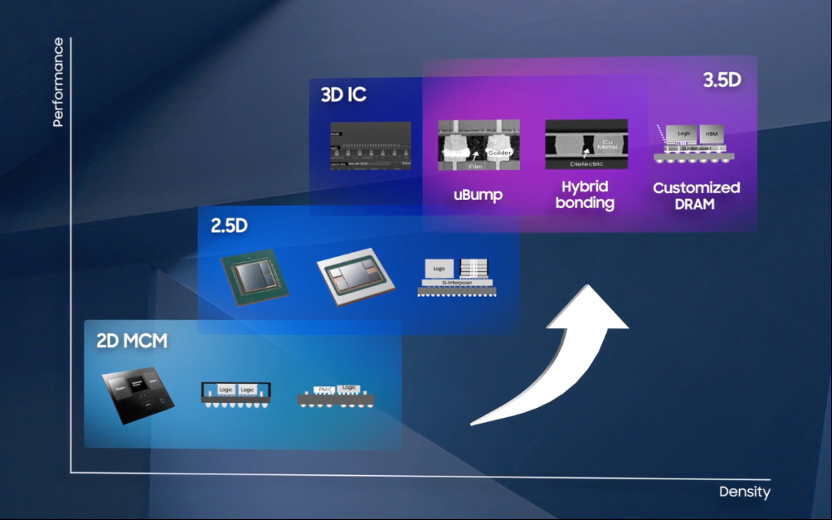

2D至3.5D的封装方案 / 三星

除了2D、2.5D与3D的IC技术之外,三星还在开发全新的3.5D封装技术,这种系统级封装内还将加入堆叠的定制DRAM或SRAM裸片,实现更高的性能与密度。

小结

在开发2.5D/3D集成的多芯片或多Chiplet系统级芯片时,设计者往往还会遇到在传统单芯片设计上罕见的技术障碍,比如多出来的接口IP或潜在的功耗增加。这时候,三星、台积电和刚进入IDM 2.0的英特尔等代工厂商还会提供异构设计的方法和工具,帮助设计者克服这些挑战。在异构集成的大势之下,代工厂也将提供更多的服务模式,增加封装、测试以及一站式的设计服务。

在近期举办的2021年SamsungFoundry论坛上,三星透露了2/3nm制程工艺的新进展,并公开发布了全新的17nm工艺。三星市场战略副总裁MoonSoo Kang也面向产业合作伙伴,公布了三星在异构集成上的计划,如何为摩尔定律再度添加一个“维度”。

旗舰GPU与移动芯片的面积变化对比 / 三星

几十年间,半导体产业一直在不懈地推动摩尔定律,以更先进的制程做到更多的晶体管数目,这就是我们常说的“延续摩尔”方案,也是当前计算与电路领域持续创新最大的推动力。

尽管摩尔定律的延续,芯片面积仍在扩大,比如一直在追求算力的GPU,已经快要逼近光罩尺寸的限度了。再加上晶体管数目的增加,使得芯片设计成本和生产成本无休止地增加。在不少人看来,单靠“延续摩尔”不再是一个技术与成本上可持续的方案。

与此同时,更多的功能与特性集成在单个芯片上,却又没有单个制程可以满足所有不同功能的需求,比如模拟、射频、高压等,即便可以满足也无法达到优秀的性能与成本平衡。“延续摩尔”的方案在这类挑战面前束手无策,因此才出现了异构集成这种“扩展摩尔”的方案。通过两种方案的互补,共同做到“超越摩尔”。

Chiplet:降低成本提高良率的救星

随着单个芯片加入更多特性,即便摩尔定律延续下去,其芯片面积仍在增加,为所有不同功能的设计区块使用同一个制程节点成了抵消的选择,好在如今有了Chiplet这一救星的出现。将一大块裸片分成较小的chiplet,并为每个chiplet使用最优的制程,可以显著提高整个芯片的良率,同时减少生产成本。例如某些特定的接口IP并不会因为采用先进制程而获得面积或性能上的优化,对这些IP使用成熟制程和专用定制制程,可以做到更低的成本以及更优的性能。

Chiplet方案 / 三星

另一个可行方案就是模组化的设计与制造,也就是重复使用相同的组件chiplet。不少IP模组都可以作为chiplet重复使用,只有芯片的其他部分需要重新设计和生产,此举显著减少了设计、开发与生产的成本,芯片厂商可以借此更快实现产品迭代。

X-Cube:垂直3D集成

异构集成不只是为了成本和良率考虑,也能进一步提升芯片性能。传统的2D设计中,信号路径有几毫米长。而在3D集成下,芯片的堆叠可以将信号路径减少至几微米,大大改进了芯片延迟。除此之外,3D集成中更出色的内联间距可以实现更高的带宽,进一步提高芯片性能。

早在2014年,三星就首次实现了将宽IO内存与移动应用处理器的3D堆叠,也就是三星的Widcon技术。随后,3D芯片堆叠技术继续发展,诞生了一系列HBM内存产品。HBM就是由DRAM与逻辑堆叠,并由微凸块和TSV相连而成的。也正是因为3D堆叠技术,三星得以开发出了3层的CMOS图像传感器,由图像传感器、逻辑与DRAM三种不同的裸片堆叠在一起而成。

2020年,三星推出了X-Cube技术,这项技术使得两个逻辑单元裸片可以垂直堆叠在一起,形成一个单独的3D芯片,由微凸块与TSV连接。X-Cube分为两种形式,两个裸片由微凸块连接或是直接铜键合。

X-Cube路线图 / 三星

第一代X-Cube技术(u-Bump)主要依靠微凸块连接,三星已经发布了针对7nm逻辑制程的TSV PDK,采用F2B结构,凸块间距为40um。面向4/5nm的TSV PDK也已经发布,改用F2F的结构,凸块间距降低至25um。尚在开发中的第二代X-Cube技术(Bump-less)则采用了直接铜键合技术,间距降低至4um。

值得一提的是,英特尔的Foveros3D堆叠技术路线与三星X-Cube大致相同。第一代Foveros的凸块间距在36um至50um之间,而下一代FoverosOmni技术同样可以做到25um的凸块间距。尚在开发的Foveros Direct也采用了直接铜键合的方式,宣称凸块间距降低至10um以下。

过去的X-Cube架构中,底部裸片的面积要大于顶部裸片,然而为了更好了满足客户对芯片分区和散热等不同要求,三星也将在后续提供顶部裸片大于底部裸片的结构。目前三星已经完成了3D堆叠SRAM的验证,在7nm的制程下,可以做到48.6GB/s的带宽,以及7.2ns的读取延迟与2.6ns的写入延迟。

除此之外,三星还提供了一项差异化技术,ISC(集成堆叠电容)。这一电容应用了已经在三星DRAM产品中获得验证的硅电容结构、材料和工艺,具有1100nF/mm2的电容密度,可以有效提高电源完整性。三星的ISC还提供了多种不同的配置,比如分立型、硅中介层型和多晶圆堆叠型,以满足客户不同的结构需求,ISC预计将在2022年进入量产阶段。

I-Cube:横向2.5D组合

另一方面,为了从横向组合芯片,三星开发了所谓的2.5D技术I-Cube,将逻辑单元与多个HBM集成在同一硅中介层上。目前三星已经成功实现了一个逻辑裸片+两个HBM的I-Cube2量产,成品之一就是百度的昆仑AI芯片。百度的昆仑AI芯片不仅使用了三星的14nm制程,也运用了三星的I-CUBE 2技术。

I-Cube使用了预筛选的技术,在封装的中间阶段进行运算测试,从而提高良率。该技术还采用了无封胶的结构,做到更好的散热性能,据三星强调,与传统的2.5D方案相比,I-Cube的散热效率高上4.5%。此外,与其他代工厂商相比,三星的I-Cube技术还有一些优势,比如与三星内存合作,率先用上最新的内存方案

I-Cube4示意图 / 三星

目前三星已经在计划集成4HBM3模组的I-Cube4量产工作,而6 HBM的I-Cube6也已经做好量产准备,前者预计2022年进入大批量产阶段。三星更是准备了两个逻辑裸片+8个HBM的I-Cube8方案,目前尚处于开发阶段,预计2022年末将正式上线。

2D至3.5D的封装方案 / 三星

除了2D、2.5D与3D的IC技术之外,三星还在开发全新的3.5D封装技术,这种系统级封装内还将加入堆叠的定制DRAM或SRAM裸片,实现更高的性能与密度。

小结

在开发2.5D/3D集成的多芯片或多Chiplet系统级芯片时,设计者往往还会遇到在传统单芯片设计上罕见的技术障碍,比如多出来的接口IP或潜在的功耗增加。这时候,三星、台积电和刚进入IDM 2.0的英特尔等代工厂商还会提供异构设计的方法和工具,帮助设计者克服这些挑战。在异构集成的大势之下,代工厂也将提供更多的服务模式,增加封装、测试以及一站式的设计服务。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

三星电子

+关注

关注

34文章

15891浏览量

182873 -

异构

+关注

关注

0文章

45浏览量

13490 -

异构集成

+关注

关注

0文章

40浏览量

2248

发布评论请先 登录

相关推荐

热点推荐

三星电子正式发布Galaxy Z TriFold

2025年12月2日,三星电子正式发布Galaxy Z TriFold,进一步巩固了三星在移动AI时代中针对形态创新的行业优势。

0201三星贴片电容的优势与应用

三星0201贴片电容凭借0.50mm×0.25mm的极致尺寸(部分批次为0.6mm×0.3mm),在有限空间内实现高性能集成,成为推动电子设备小型化与功能升级的关键元件。 0201三星贴片电容的优势

三星最新消息:三星将在美国工厂为苹果生产芯片 三星和海力士不会被征收100%关税

给大家带来三星的最新消息: 三星将在美国工厂为苹果生产芯片 据外媒报道,三星电子公司将在美国德克萨斯州奥斯汀的芯片代工厂生产苹果公司的下一代芯片。而苹果公司在新闻稿中也印证了这个一消息,在新闻稿中

曝三星S26拿到全球2nm芯片首发权 三星获特斯拉千亿芯片代工大单

我们来看看三星的最新消息: 曝三星S26拿到全球2nm芯片首发权 数码博主“刹那数码”爆料称,三星Exynos 2600芯片已进入质量测试阶段,计划在今年10月完成基于HPB(High

回收三星S21指纹排线 适用于三星系列指纹模组

深圳帝欧电子回收三星S21指纹排线,收购适用于三星S21指纹模组。回收三星指纹排线,收购三星指纹排线,全国高价回收三星指纹排线,专业求购指纹

发表于 05-19 10:05

详细解读三星的先进封装技术

集成电路产业通常被分为芯片设计、芯片制造、封装测试三大领域。其中,芯片制造是集成电路产业门槛最高的行业,目前在高端芯片的制造上也只剩下台积电(TSMC)、三星(SAMSUNG)和英特尔

三星在4nm逻辑芯片上实现40%以上的测试良率

三星电子在 HBM3 时期遭遇了重大挫折,将 70% 的 HBM 内存市场份额拱手送给主要竞争对手 SK 海力士,更是近年来首度让出了第一大 DRAM 原厂的宝座。这迫使三星在 HBM4 上采用

发表于 04-18 10:52

三星辟谣晶圆厂暂停中国业务

对于网络谣言三星晶圆代工暂停所有中国业务,三星下场辟谣。三星半导体在官方公众号发文辟谣称““三星晶圆代工暂停与中国部分公司新项目合作”的说法属误传,

三星贴片电容封装与体积大小对照详解

在现代电子制造业中,贴片电容作为电子元件的重要组成部分,其封装形式与体积大小对于电路板的布局、性能及生产效率具有重要影响。三星作为全球知名的电子元器件供应商,其贴片电容产品系列丰富,封装多样,满足了

三星电容的耐压与容量,如何满足不同电路需求?

三星电容的耐压与容量是满足不同电路需求的关键因素。以下是对三星电容耐压与容量的详细分析,以及如何根据电路需求进行选择的方法: 一、三星电容的耐压值识别与选择 1、耐压值的概念 :电容长期可靠地工作

三星否认重新设计1b DRAM

据DigiTimes报道,三星电子对重新设计其第五代10nm级DRAM(1b DRAM)的报道予以否认。 此前,ETNews曾有报道称,三星电子内部为解决12nm级DRAM内存产品面临的良率和性能

下一代FOPLP基板,三星续用塑料,台积青睐玻璃

近期Digitimes报道指出,在下一代扇出型面板级封装(FOPLP)解决方案所使用的材料方面,三星和台积电走上了一条明显的分歧之路。 据《电子时报》报道,三星坚持使用塑料,而台积电则在探索用于

容乐电子教你怎么辨别三星原装物料?

在现代电子制造中,原装物料的质量直接影响着产品的性能和可靠性。因此,辨别三星原装物料成为了许多电子产品制造商和采购人员的重要任务。容乐电子作为专业的元器件供应商,且是三星的官方代理商,致力于为客户

三星芯片代工新掌门:先进与成熟制程并重

据韩媒报道,三星电子设备解决方案部新任foundry业务总裁兼总经理韩真晚(Han Jinman),在近期致员工的内部信中明确提出了三星代工部门的发展策略。 韩真晚强调,三星代工部门要实现先进

超越摩尔,三星的异构集成之路

超越摩尔,三星的异构集成之路

评论