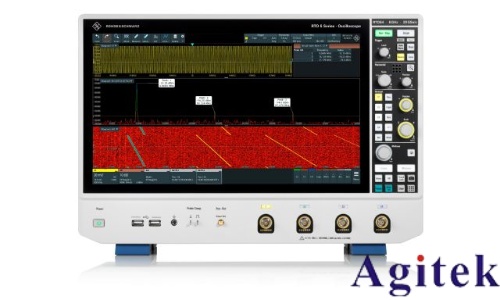

分析高速数据通信接口是一项重要任务,可确保信号完整性。这种分析的一个主要挑战在于连接物理接口和示波器,因为大部分数据通信接口不提供适用于射频的测试接头。这需要使用测试夹具连接高速数据通信中频接口和示波器的射频连接器,但这会影响信号完整性测量。带有高级抖动选件的RTP和最新RTO6示波器可以分析和分离抖动影响。此外,该选件自身还可以评估测试夹具和迹线的影响,有助于用户充分了解测试装置的影响。

解决方案

RTP和最新RTO6示波器能够深入分析信号完整性。抖动分析能够细分关键参数。除了误码率(BER)以外,可以通过时域轨迹、频域频谱和统计直方图查看所有参数。

此外,RTP-K133/RTO-K133高级抖动选件具有两个新功能,将分析扩展到了常见的抖动参数之外:

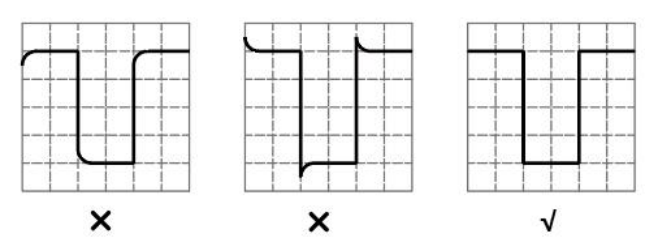

► 合成眼图:让用户探索特定抖动参数对数据眼图的影响

► 传输通道阶跃响应的固有测量:包括被测设备、测试夹具和电缆的数据相关特性

本应用说明描述了分析在误码率测试( BERT )中通过扩频时钟(SSC )和无抖动添加生成的差分信号

( 8. 125 Gbps,PRBS31)。信号在PCIe Gen4 ISI电路板 (PCIe-VAR-ISI)上通过长迹线传播。电路板引起的码间干扰(ISI)是造成抖动的主要因素。如本说明结尾所示, 这种特殊装置能够利用矢量网络分析仪(VNA)验证阶跃响应。

以相同的方式分析抖动至关重要,接收机将接收数据并为其计时。因此,示波器会捕获差分发射数据,并利用硬件时钟数据恢复(CDR)触发数据信号。注意,RTP高性能示波器具有高达122 000波形/秒的一流波形捕获率。

在分析之前,应根据周期性抖动分析需要的最小频率分辨率 设置合适的采集时间。为了实现低至40 kHz的分辨率(在开 关电源(SMPS)范围内)和40 Gsample/s的采样率,记录长度设置为2 Msample(= 2 ×(采样率)/(SMPS开关频 率)),因此采集时间为50 μs。

抖动分解算法将差分通道作为不归零(NRZ)信号进行 分析。必要的CDR配置为含带宽为16 MHz的二阶锁相环 (PLL)。与预期结果一样,主要 以DDJ为主。BER 浴盆曲线说明BER测量值和计算值吻合良好。这种分解算法的新颖之处在估计阶跃响应。阶跃响应是施加到通道传递函数的理想阶跃引起的结果。此估计将未经校准的测试夹具纳入考量。

用户可以配置估计过程中的阶跃响应时长;在本例中,此时长设为75 UI。阶跃响应时长的设置遵循三个原则:

► 配置的阶跃响应时长越长,计算时间越长。

► 阶跃响应时长应大于通道内存。时长较长,有利于详细分析阶跃响应。

► 眼图的运行时长应大于阶跃响应时长。

用户可以使用光标和自动测量等熟悉的工具来分析阶跃响 应。本例中使用光标测量上升时间。通过测量上升时间tr, 用户可以根据有效用于单级低通滤波器的 fB = 0.35 ⁄ tr 公式 估计通道带宽fB。因此,可以在频域中进行更加详细的分析。传递函数的超调、下垂和振铃等现象在频域中同样可见。

除了直方图和估计的阶跃响应外,图3还以幅度(参见标记M1)和相位(参见标记M2)的形式显示了频域中阶跃响应的相关传递函数。为了根据阶跃响应计算频域中的传递函数,数学菜单提供了一组函数 [1]:

► Step2FreqRespNormMag(《channel》,《points》)

► Step2FreqRespNormPhi(《channel》,《points》,

《delay》)

与预期结果一样,幅度显示出频率相关衰减,原因主要在于介电损耗。趋肤效应非常小。相位显示出迹线分散。由于通道带宽有限,因此两条迹线中超出16 GHz的数值均为噪声。8.125 GHz处出现因数据率引起的伪影。

此测量与VNA测量进行了比较。PCIe Gen4 ISI电路板产生ISI,因此在频域中测量相关迹线(差分),并比较传递函数和散射参数差分/差分(S21 DD)(参见图 4)。

两种测量均在0 Hz至16 GHz范围内显示出吻合良好。幅度偏差小于1 dB,相位偏差不足5°。

摘要

RTP和最新RTO6示波器分析数字高速信号的信号完整性。示波器精确测量TJ、RJ、PJ和DDJ等常见的抖动成分。示波器自身还可以分析引起DDJ的传递函数。由于操作不便,因此针对传输路径的各个部分单独进行特性测量颇具挑战性,且信号驱动器的输出阻抗在频率范围内通常未知。因此,固有的传递函数测量是了解DDJ根源的关键要素。

编辑:jq

-

数据通信

+关注

关注

2文章

543浏览量

35173

原文标题:如何应对高速数据通信接口的信号完整性挑战?

文章出处:【微信号:罗德与施瓦茨中国,微信公众号:罗德与施瓦茨中国】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PK6350无源探头在高速数字总线信号完整性测试中的应用案例

高速接口如何选用低电容TVS管?信号完整性与防护性的双重考量

SN65MLVD040:高速数据通信的理想之选

Samtec高速线缆深入解析:高速信号完整性的关键技术

如何在CW32 MCU上优化I2C通信

了解信号完整性的基本原理

高速接口如何选用低电容MDDTVS管?信号完整性与防护性的双重考量

基于高速数据通信接口的信号完整性的解决方案

基于高速数据通信接口的信号完整性的解决方案

评论