随着高速集成工艺技术的发展,锁相频率合成器的集成化程度已大大提高。目前已出现了一系列将高速前置合频器集成在片内的单片集成频率合成器芯片。例如美国Motorola公司的MC145190/191/192、MC145200/201和日本富士通的MA101XT、MB1501/1504系列等等。片内高速换模前置分频器通常为固定÷64/65或÷32/33,工作频率可达500MHz~2GHz。集成单片PLL频率合成器芯片给频率合成器的电路设计带来了极大的方便,而且实现了电路结构的小型化,因此被广泛用在个人移动通信手机、无绳电话和车载移动通信手机中。

下面就Motorola公司的1.1GHz单片频率合成器芯片MC145190/191/192的性能结构和电路设计作介绍。

1 MC145190/191/192的结构特点和引脚功能

MC145190/191/192是带有串行口的最高合成频率可达1.1GHz的单片集成锁相合成器芯片。由于片内采用了面向字节的特有体系结构,因而使其内部编程变得非常容易。由于内部寄存器使用了专门设计的性能优良的箝位寄存器,使得这三个寄存器的数据随机存取不

需要地址控制位即可完成。频率合成器频率的切换可通过Din、CLK、ENB三个串行口,把数据传给24位箝位寄存器A来实现。同时,还允许箝位寄存器C关闭不使用的输出口,以减少系统噪声和接口引入噪声。接口对SP1和MICROWIRETM均兼容。

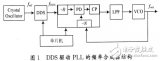

MC145190/191/192的片内功能框图如图1所示。由图中可知,该器件片内专门安排的三个箝位寄存器分别为:24位箝位寄存器A、16位箝位寄存器R和8位箝位寄存器C。其中24bit A寄存器存储A、N计数器数据和控制数据,16bit R计数器存储÷R参考分频器和晶振控制数据,而8bit C寄存则存储控制数据。分频数据和控制数据通过时钟口CLK、数据口Din和使能口ENR经由逻辑控制单元串行送入这三个箝位寄存器。这种器件备有双端频率相位检测输出ΦR、ΦV和单端频率相位检测电流泵输出PDout的两种鉴相输出方式。这两种相位检测输出均有线性传输特性,不存在鉴相死区。但单端鉴相输出的最大电流由Rx管脚到地的外接电阻决定。

参考频率可支持外加晶振产生或直接由REFin端输入,然后经可配置的4分频器后送入13bit的可编程÷R参考分频器,获得所需分辨率fR。输入频率由fin或fin端输入,最高频率为1.1GHz,输入幅度为200mVP-P。经片内输入放大器INPUTAMP放大后送入÷64/65双模分频器分频,然后进入A和N计数器,所以fin和fv之间的分频比为N64+A。

此外,芯片还具有两个通用数据输出口Output A和OutputB。其中Output A当定义为DATAOUT时,可允许芯片级联使用,而Output B则为漏极开路输出口。

Pin12= VCC输入放大器和64/65电源 Pin14= VDD总电源

Pin5= VPD PDA和PDB电源 Pin7 = GND 地

图1 MC145190/191/192内部功能框图

MC145190的VDD为8 ~ 9.5V,MC145191的VDD为4.5 ~ 5.5V,MC145192的VDD为 2.7 ~ 5V。它们的串行口最高送数速率可达4Mbps,因此可以实现高速跳频送数。

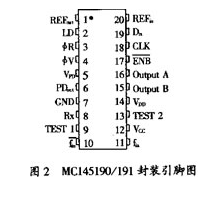

MC145190/191/192的封装有20脚贴片封装式和双列直插式封装两种,其引脚功能图如图2中所示。由图中可知,这20只引脚可分为5类:2只参考信号引脚REFin和REFout,7只回路引脚fin、fin′、PDout、Rx、ΦR、Φv和LD,5只数字接口引脚Din、CLK、ENB‘、Output A和Output B,2只检测引脚TEST1和TEST2,4只电源引脚VDD、VCC×VPD和GND。

REFin 和REFout引脚为Pin20和Pinl,这两个引脚可作为外接晶体或输入参考信号使用。其功能模式有晶体模式和参考模式两种,模式控制由R寄存器中的R13、R14、R15控制位来实现。

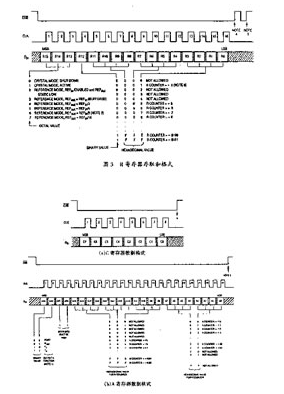

R13、R14、R15控制位的数据格式,示于图3的R寄存器数据存取和格式图中。当R13、R14、R15为八进制1状态,即001时,为外接晶振工作模式,当R13、R14、R15为八进制3状态,为参考频率输入模式,且REFout=REFin。

其他4、5、6、7分别为REFout=FEFin/2,REFout=REFin/4,REFout=REFin/8,REFout=REFin/16等模式。

Din(Pin19)串行数据输入脚、CLK(Pin18)串行口时钟输入脚和ENB′(Pin17)串行使能端输入等组成串行数据输入口,ENB′低电平有效。即ENB′由高电平变为低电平时,时钟CLK信号的上升沿将Din端的串行数据逐位移入相应的寄存器。

Output A(Pin6)可编程数据输出端口。该引脚可作为fR或fv的输出口,也可以用作数据输出端口。其功能由A寄存器的最高两位A23、A22决定,A23、A22控制位的数据格式示于图4的A寄存器数据存取和格式。图中:A23 =A22=1时,OutputA作fR输出口,这时的fR是晶振频率的13位R计数器的分频缓冲输出。因此,测知fR值就可确定R计数器的计数值。由于鉴相器的最高工作频率为2MHz,所以fR必须低于2MHz。

A23=1、A22=0时,Output作fv 输出口,这时的输出频率fv 是输入频率fin的(N*64+A)分之一,同样要求fv小于2MHz。

A23=0,A22=1时,Output A作数据输出口。这是个24位移位寄存器的串行输出口,在时钟脉冲的上升沿逐个输出串行数据,这种方式用以多个器件级联工作。

A23=0,A22=0时,Output A作微机控制端口的扩展口用,信号在C寄存器的port位C1=0时端口为低,C1=1时端口为高。

OutputB(Pin15)漏极开路数字信号输出口,可以用作MCU端口的扩展口。该端口受C寄存器中的outB位C0的控制,C0=0时信号为低,C0=1时端口处高阻状态,这时可外接一个上拉电阻,使其输出电平拉到小于或等于VPD范围内的某个值。

fin 和fin′ (Pin11、10)频率输入引脚,输入幅度为200mVPP,最高频率1.1GHz,采用1000PF电容耦合输入。若只用fin脚输入时,fin′必须通过1000PF电容耦合到地。

PDout和ΦR、ΦV(Pin16和Pin3、4)分别为单端鉴相输出和双端鉴相出。MC145190/191/192的鉴相器与MC145146的鉴相功能基本相同,但PDout的流入流出电流可通过C寄存器中的C3、C2位控制(见图4(a)C寄存器数据格式图),而且还可以通过Rx端(Pin8)外接电阻Rx调节。

Rx(Pin8)外接电阻引脚。外接电阻值结合C寄存器C3、C2确定PDout注入流出电流值,当C3=C2=1时,PDout可得到最大电流。对MC145191Rx的最佳值选择在18k~40kΩ之间,这时PDout的流入流出电流在1~2mA范围内。

LD(Pin2)环路锁定指示端口,输出电平在地或VDD之间变化。环路锁定时,LD端口输出为高阻电平加窄脉冲信号。

TEST1(Pin9)双模前置分频器÷64/65模式控制信号入口端。当TEST1为低电平时,双模前置分频器按÷65分频;当TEST1为高电平时,则按÷64分频。

TEST2(Pin13)前置分频器÷64/65输出端口,输出频率应为输入频率fin的1/64或1/65。

VDD(Pin14)器件CMOS数字部分供电引脚,对MC145191,VDD= 4.5 ~ 5.5V。

VCC(Pin12 )器件RF放大器和双模前置分频器÷64/65的供电引脚,对MC145191,

VCC=4.5 ~ 5.5V。

VPD (Pin5)为鉴相器PDA、PDB的供电引脚,对MC145191,VPD= 4.5 ~ 5.5V。

GND(Pin7)为公共接地端。

2 MC145190/191/192的数据格式与编程

MC145190/191/192的C、R、A寄存器均为箝位寄存器,数据流的输入不需要地址和控制信号,而是由数据流的字长度来决定输入到哪个寄存器。8个时钟周期的数据流移入C寄存器,16个时钟周期的数据流移入R寄存器,24个时钟周期的数据流移入A寄存器。数据流按高位顺序先移入,而C、R、A的有效位则按低位顺序计算。

R寄存器的存取和数据格式如图3所示。高位R15、R14、R13的控制功能如图中所示,低位R0 ~ R12为13位R计数器的数据内容,R=0~8191。

C寄存器为8位控制寄存器,数据格式如图4(a)中所示。

C7-POL位用以选择鉴相器的输出极性。当C7=1时,PDout输出反极性,且ΦR和Φv互换功能;C7=0时,PDout输出正极性,且ΦR和Φv功能不变。

C6-PDA/B位用以选择鉴相器PDA或PDB:C6=1时选用PDA,而PDB则禁止;C6=0时则选用PDB,PDA这时被禁用。

C5-LDE位为环路锁定指示检测位,该位通常置“0”。C4-STBY位用以控制器件处于睡眠备用状态,可节省功耗。

C4=1时,PDout和ΦR、Φv均处高阻状态,且Rx电流关断,A、N、R计数器停止计数,这时器件处于睡眠备用状态;C4=0时,PDout和ΦR、Φv,以及A、N、R计数器进入正常工作状态。

C3、C2位用以控制PDout流入流出电流的大小,当这两位均置高位“1”时,可得到最大电流100%。PDout电流的大小步长还受C1-port数据控制。当OutputA不作数据端口使用时〔通过A寄存器中的A23、A22位置数控制,见图4(b)A寄存器存取和数据格式图〕。

C1=0, 则PDout按10%步长变化电流,C1=1, 则PDout按25%步长变化电流。OutputA用作数据端口使用时,则C1决定OutputA的状态,C1=1, 则Output A为高,C1=0, 则Output A为低。

C0-outB位决定Output B的状态,C0=1时Output B为高,C0=0时Output B为低。

A寄存器的数据格式如图4(b)中所示,A寄存器为24位箝位寄存器。其中高4位为控制码,A23、A22确定OutputA的输出功能,A21

、A20为内部逻辑控制码,必须都置“1”。A0~A7为8位脉冲吞除计数器的数据码A=0~255,A8~A11为12位主计数器N的数据码N=5~4095,N禁止小于5。显然N计数器的容量大于A计数容量。在环路设计时,也必须是N>A。

3 应用设计举例

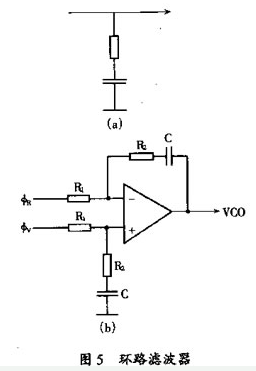

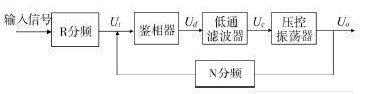

采用MC145109/191/192设计单环频率合成器时,必须外接环路滤波器和配上一只相应的压控振荡器VCO。外接环路滤波器的结构如图5所示,图5(a)适用于PDA,即接于PDAout输出端,这时环路设计关系式为KΦ·KVCO=ωn2 * MC和2ζ=ωnRC,式中M为环路分频比。

图5(b)适用于PDB,这是一个有源滤波器,环路设计关系式为KΦKVCO=ωn2MCR1和2ζ=ωnR2C。

采用PDA的PDout输出图5(a)时,鉴相增益KΦ=Ipout/2πA/rad。Ipout为PDout的流入流出电流,前面已指出由C寄存器控制码和Rx确定其值。

若采用PDB的图5(b)有源滤波器时,KΦ=VPD/2πV/rad。

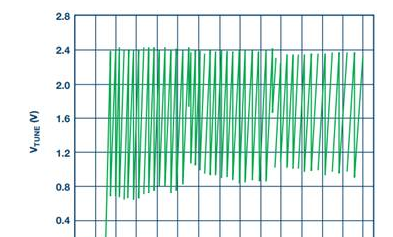

下面以移动通信GSM频段频率合成器为例,介绍MC145191的应用设计方法。移动通信GSM标准的合作频段为935~960MHz和890~915MHz,双工间隔为45MHz,频道间隔为200kHz,换频时间小于5ms。以935~960MHz频段为例,该频率合成器的VCO应满足的频率范围为:

2f0min-f0max=2*935-960=910MHz,

2f0max-f0min=2*960-935=985MHz

变容管的控制电压调谐范围为1~5.5V,则压控灵敏度为:

K0 =(985-910)/(5.5-1) = 17*106(Hz/V)=2π*17*106(rad/s/V)

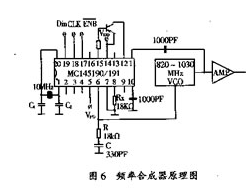

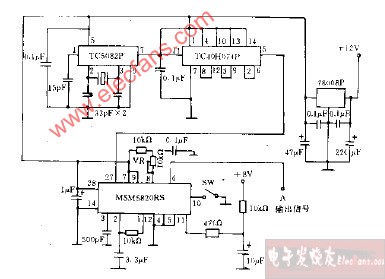

频率合成器的原理图如图6中所示。

单环频率合成器的频率间隔△f0=fR=200kHz,图中采用10MHz晶振。R寄存器的R15、R14、R13置成001,REFin?和REFout?为外接晶振功能,所以÷R计数器的分频比为:

NR = (fosc / fR) = (10*106) /200*103 = 50

将50化为二进制数,即就是13位R计数器R0~R12的数码。环路可编程序分频比M

为:

M1 = ( f01 / fR) = ( 960 / 0.2 = 4800

M2 = ( f02 / fR) =(935 / 0.2 = 4675

环路程序分频器采用换模吞除计数方式,所以有:

M = PN+A

的关系。其中N为主计数值,A为吞除脉计数值,P为高速前置分频器的模值,MC145191中P=64。若以M2=4675为例,由上述关系可确知:

N = 73,A = 3,即M = PN+A = 64*73+3 = 4675。

将A=3,N=73化为二进制数值,即就是A0 ~A7、A8 ~A19的数据码值。其他环路分频比的M值均可以用此方法来确定A0 ~ A19这20位数据值,从而实现编程置数。

鉴相器采用PDA,C寄存器的C6=1,鉴相增益KΦ=Ipout/2πA/rad。为得到最大100%的流入流出电流,C寄存器中的C2=C3=1,Rx取18kΩ,PDout流入流出电流约2mA,即KΦ=2*10-32πA/rad。

压控振荡器的压控特性为正向控制特性,所以希望PDout输出正极性,即C7=0,按10%步长变化电流,即C1=0。所以C寄存器中C7~C0为“01001100”控制码状态。

合成器的输出频率在935~960MHz,跨度为25MHz。由上述可知,环路可变分频比在4800~4675范围内变化。显然,这时锁相环路的ζ和ωn也将是可变的,这种变化将直接影响频率合成器的瞬间特性。为保证合成器性能,通常阻尼系数ζ用ζ=0.707来进行环路设计,当然为使环路满足快速换频特性,也可以放宽到≤1来进行设计。ζ=0.707以后,环路的上限频率ωH ≈ ωn。

考虑环路对鉴相波纹的抑制作用,通常要求ωH ≤ ( 1/5)*ωn,

即ωn ≤ ( 1/5*ωR = 0.2 * 2π * 200 * 103(rad/s)。

由于采用PDA鉴相器,环路滤波器接于PDout端口,如图6中所示。环路设计关系为:

KΦKVCO= ωn2MC和2ζ=ωnRC,即:

C = KΦKVCO / ωn2M

R=2ζ/ωnR

式中M取环路可变分频比中心值,

即M = ( 1 / 2)(M1+M2)= ( 1 / 2)(4800+4675) = 4737.5。

所以

有C = (2*10-3/2π*46.7*106)/((1 / 5)*2π*200*103)2 ×4737.5 = 311.42 PF

R=(2*0.707)/(1 / 5)*2π*200*103×311.42×10-12=18.3 kΩ

实践中C可以取330PF,R可取18kΩ接入电路中。

环路锁定时间可以用下式进行估算:

ts = ( 4 / ζ*ωn) = 22.5 μs

考虑是串行送数置数,以及微机指令时间在内,则频率合成器的频率切换时间tp<1ms是完全可以做到的。

责任编辑:gt

-

芯片

+关注

关注

462文章

53530浏览量

458838 -

频率合成器

+关注

关注

5文章

305浏览量

33410 -

pll

+关注

关注

6文章

976浏览量

137568

发布评论请先 登录

如何利用FPGA设计PLL频率合成器?

pll频率合成器-锁相环频率合成器

DDS PLL短波频率合成器设计

基于DDS芯片和集成锁相芯片构成的宽频合成器设计

基于DDS驱动PLL结构的宽带频率合成器的设计与实现

基于FPGA与PLL频率合成技术设计的整数/半整数频率合成器

集成单片PLL频率合成器芯片的原理、结构特点及应用分析

集成单片PLL频率合成器芯片的原理、结构特点及应用分析

评论