静电,电涌等这些具有非常大的瞬态能量的干扰,会对集成电路造成破坏,所以在实际工程应用中我们会考虑使用TVS进行抑制保护。根据干扰能量等级的不同,我们会选择不同瞬态功率的TVS(Pppm=钳位电压×瞬态峰值电流),也就是TVS瞬态电流(Ippm)的承受能力。

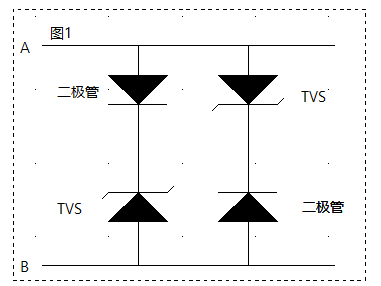

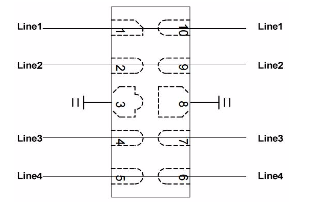

为了获得大一些的承受能力(较大的Pppm),TVS的结面积就会增加,然而,这样就会导致电容量C的增加。C太大将使有用信号衰减,这是不利的,特别是在频率较高的电子系统中。对于频率较高的电子系统的保护应用来说,TVS自身寄生电容的存在是有危害的,寄生电容常可以如图1所示,以此来减少寄生电容的影响。二极管串联支路是用于正负两种极性暂态过电压保护。普通二极管的寄生电容约为50pF,该电容与TVS的寄生电容串联后,其总的支路电容将有较大幅度的减小。

在被保护电子系统正常运行时,当AB两线之间电压超过0.6V后,普通二极管即开始导通,同时向TVS的寄生电容充电,一旦将其充满,作用于二极管上的电压将小于0.6V,使他停止导通,则这条支路将不再从系统中吸收电流,处于开路状态,从而不影响系统的正常运行。

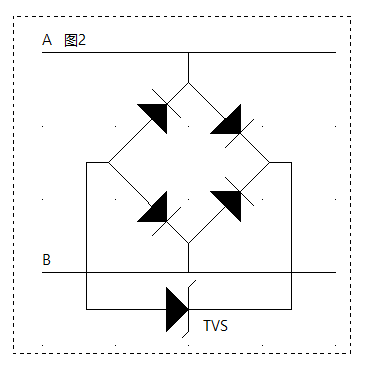

类似的减小寄生电容的原理可以推广到图2,在该图中,AB线间电压必须超过1.2V才能将TVS寄生电容充电,使保护电路停止从正常运行的系统中吸收电流。当采用分立元件来组装这些保护电路时,元件间连线的寄生电感是一个需要重视的问题。

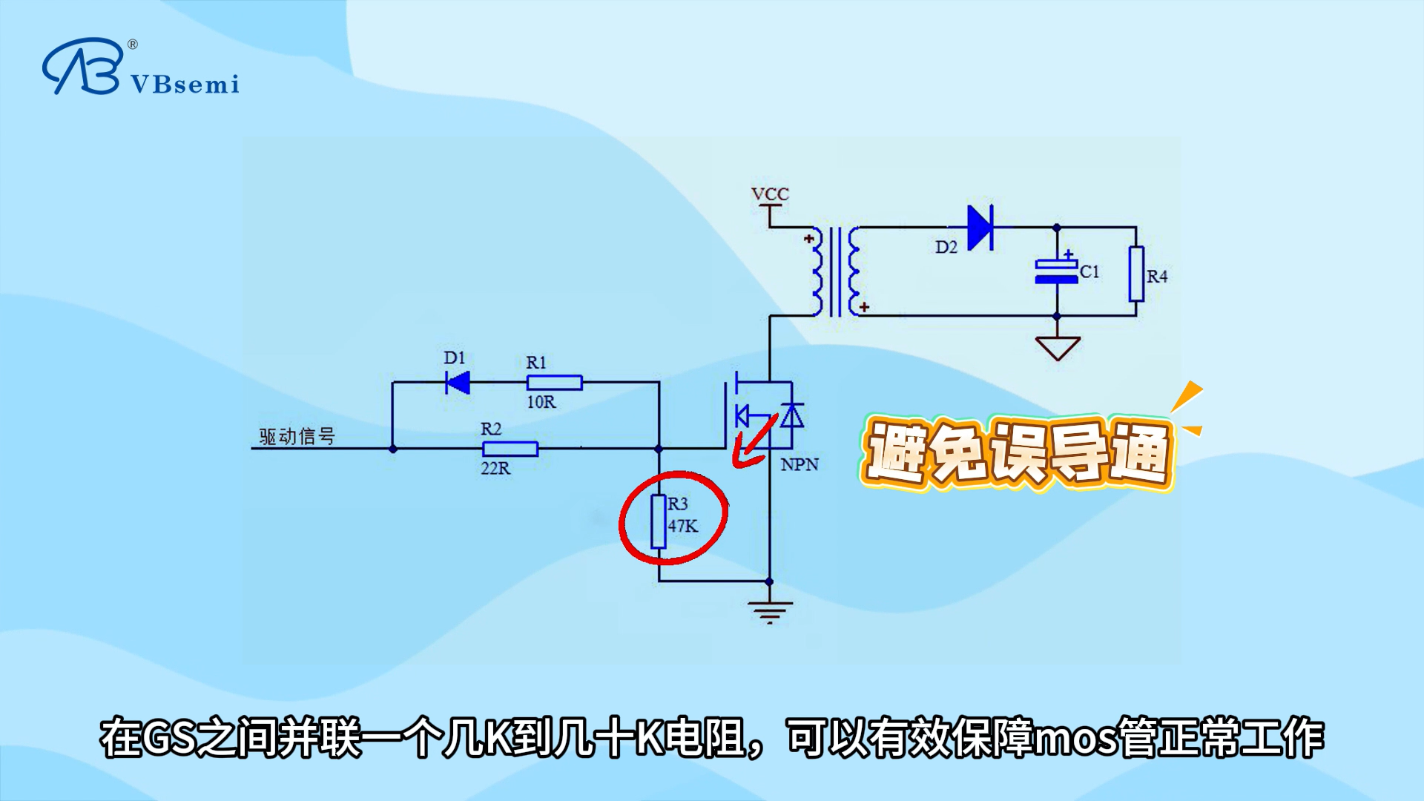

当使用分离元件时,需要使用减小寄生电感的方法。图1和图2所示的保护电路通常是,用于抑制差模过电压。为了实施在平衡线路中对共模过电压的防护,可以采用图3所示的保护电路。

由于普通二极管动作较慢,因此上述两种方法虽然能减小寄生电容,但同时也带来了副作用,即牺牲了整个保护电路一定的响应速度。因此需要根据具体应用来考量。此应用的分析是基于电容串联,总电容减小的基本概念。

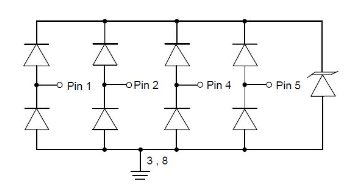

在具体的TVS产品中其实也做到了这一点,这些封装的容值可以做的比较低,同里面的二极管有一定关系。另外集成封装类型的TVS由于本身的制造工艺要求,也需要用到这种TVS与二极管串接的方式。比如常见的2510封装4路TVS,主要用于HDMI和USB3.0,容值可以做到0.2-0.4PF。

编辑:jq

-

二极管

+关注

关注

149文章

10312浏览量

176476 -

静电

+关注

关注

2文章

546浏览量

38014 -

电容

+关注

关注

100文章

6437浏览量

158033 -

TVS

+关注

关注

8文章

946浏览量

63175

原文标题:减小TVS寄生电容的应用

文章出处:【微信号:TLTECH,微信公众号:韬略科技EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

君耀TVS管LCE系列为高速信号链路量身定制的低电容浪涌保护方案

KiCad-Parasitics:KiCad 寄生参数分析插件

如何匹配晶振的负载电容

逆变器寄生电容对永磁同步电机无传感器控制的影响

面向高电容连接的低电流I-V表征测试方案

【干货分享】电源功率器件篇:变压器寄生电容对高压充电机输出功率影响

LCR测试仪中LP(Parallel)与LS(Series)模式的区别

MOSFET讲解-18(可下载)

减少PCB寄生电容的方法

移相全桥ZVS及ZVZCS拓扑结构分析

CAN通信节点多时,如何减少寄生电容和保障节点数量?

简述如何减小TVS寄生电容的应用

简述如何减小TVS寄生电容的应用

评论