杂波和干扰的有效抑制已经成为雷达信号处理的一个主要研究方向。现代雷达面临的杂波环境相当复杂,普通的动目标对消系统主要是对固定的地物杂波有一个很好的抑制效果,但对像气象、海浪、箔条等具有一定速度的运动杂波而言,杂波谱的中心会偏离零多普勒频率,如不采取有效措施,将无法很好地消去这类杂波[1-2]。因此考虑到杂波的运动性、区域性及时变性,为自适应地抑制低速运动杂波,建立动态杂波速度谱图是一个很好的选择。

现有的文献对杂波轮廓图和杂波幅度图研究较多[3-6]。杂波轮廓图可以用来选择正常支路和MTD(或MTI)相参处理支路,在杂波轮廓图内的数据采用相参信号处理后输出,在杂波轮廓图之外的部分采取正常支路输出,从而提高弱小目标在弱杂波或无杂波条件下的检测能力[6]。

杂波幅度图可以用在恒虚警检测中。参考文献[7]和参考文献[8]对三维立体杂波图的形成与应用进行了研究。而目前对杂波速度图的研究相对较少。

1 自适应杂波抑制技术

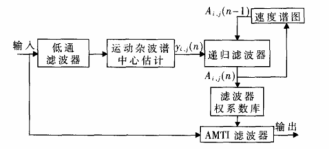

对于运动杂波,在计算得到其多普勒频率之后,抑制杂波的方法一般有两种[9]:(1)对回波信号u(t)进行运动杂波谱中心补偿,将运动杂波谱中心移动到零频,再用凹口位于零频的MTI滤波器抑制运动杂波;(2)直接采用凹口位于fd处的MTI滤波器来抑制运动杂波,而凹口于fd处的MTI滤波器权系数可预先存储在一个滤波器权系数库中,如图1所示。

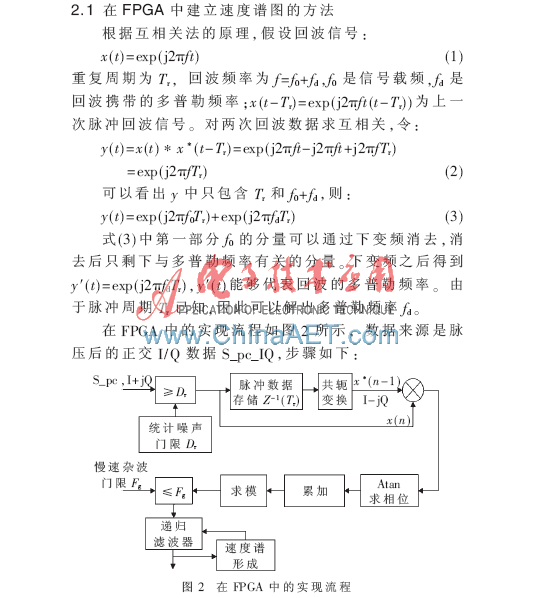

不管是对运动杂波进行多普勒中心补偿,还是利用权库法,都需要计算出运动杂波谱中心,即运动杂波的速度。因此在这里设计了一种求杂波速度谱图的方法,统计缓慢移动杂波的速度,将杂波的多普勒中心频率存储,利用FPGA的高效处理能力,通过软件编程的方法实现杂波速度谱图的建立,工程实现方便。

2 速度谱图的实现

求杂波速度的方法有多种,一种是经典的谱估计FFT法,速度精度与FFT的点数有关。在信号重频已知的情况下,FFT点数越高速度分辨精度越高。还可以用arctan求相位差的方法求杂波速度,在求解反正切函数的运算中,传统的方法有查表法、多项式近似法、查表与多项式结合法、逐位法等[10]。然而,这些方法在速度和精度上达不到要求并且硬件实现困难。

为了方便在FPGA中实现,适合FPGA中的操作流程,本设计选择互相关法进行多普勒速度的求解。

3 仿真与实验结果分析

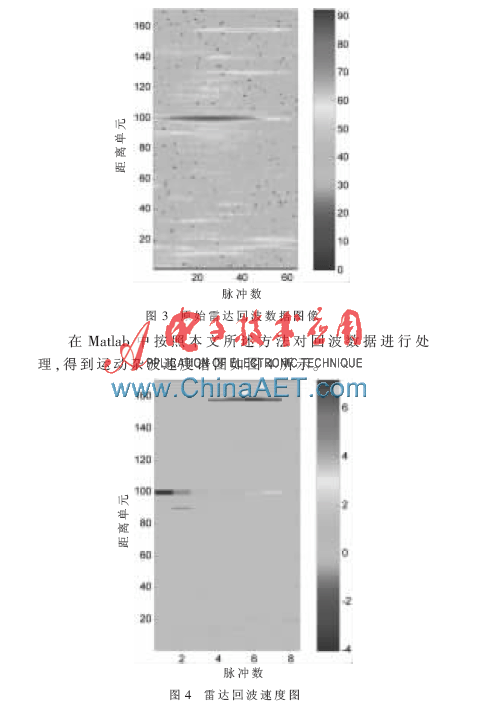

本实验利用雷达采集到的真实回波数据进行处理分析。图3显示的是雷达原始回波数据图像,纵坐标是距离单元,横坐标是脉冲数,灰度代表回波强度。其中在距离单元为160处有一个运动目标,而在距离单元为100处有一个静止的大物体,其回波强度远大于运动目标的回波强度。

从图4中可以很方便地看出各个距离单元的速度,在距离单元为100处有一个缓慢的速度变化过程,是由于天线扫描调制所引起的。此杂波速度图为抑制静止物体回波和缓慢运动杂波提供了良好的依据,可以有效地检测出快速运动目标。

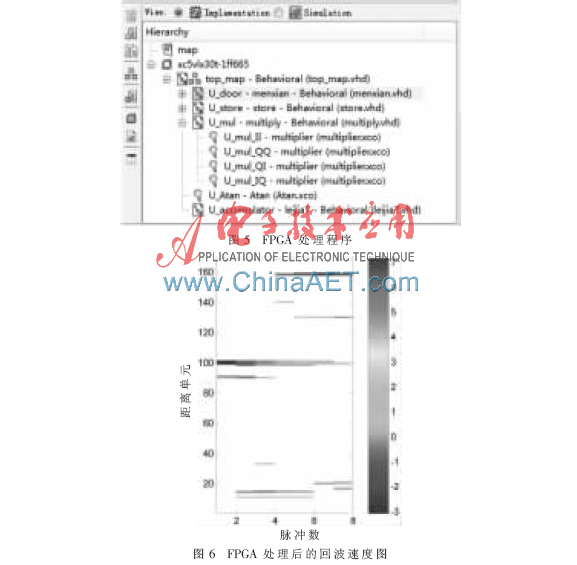

在ISE开发环境中进行编程,FPGA处理程序如图5所示。将雷达数据通过ISIM导入到ISE中,对回波数据在FPGA处理之后,再利用Matlab画出其速度谱图,如图6所示。可以看出,通过硬件处理之后的速度图与仿真结果吻合,验证了此方法的可行性。

本文主要研究了一种杂波速度谱图的建立方法,目的是统计缓慢移动的杂波速度,将杂波的多普勒中心频率存储,可以用来补偿运动杂波的速度或者结合权系数库完成杂波的自适应抑制。利用可编程器件FPGA高效的并行处理能力,通过VHDL软件编程的方法实现杂波速度谱图的建立,实现方便,对工程应用具有一定的指导意义。

参考文献

[1] 韩栋,汤建龙。基于杂波多普勒相位估计补偿的AMTI方法[J]。电子科技,2011,24(1):68-70.

[2] 李涛,钟志峰,黄坚。一种新的雷达动目标检测方法[J]。微型机与应用,2012,31(17):72-74.

[3] Chen Xiaolong,Huang Yong,Guan Jian,et al.Sea clutter suppression and moving target detection method based on clutter map cancellation in FRFT domain[C].2011 IEEE CIE International Conference,2011,1:438-441.

[4] HOURIA M,M′HAMED H,FATIHA Y E.A real time implementation on FPGA of a clutter map CFAR detector[C]。 Radar Symposium(IRS),2011 Proceedings International,IEEE,2011:207-211.

[5] 王雪,雷卓,欧阳耀果。基于雷达杂波图的CFAR算法[J]。火控雷达技术,2010,39(4):52-55.

[6] 刘俊涛,侯颖妮,宋万杰,等。轮廓杂波图恒虚警处理中面杂波性能分析[J]。电子学报,2006,34(9):1649-1652.

[7] 闫修林,阮增苗。杂波图技术在雷达终端信号处理中的应用[J]。现代雷达,2004,26(5):34-36.

[8] 刘俊涛,宋万杰,吴顺君。基于FPGA三维杂波图的设计与实现[J]。现代雷达,2005,27(12):17-20.

[9] 吴顺君,梅晓春。雷达信号处理和数据处理技术[M]。北京:电子工业出版社,2008.

[10] 骆艳卜,张会生,张斌,等。一种CORDIC算法的FPGA实现[J]。计算机仿真,2009,26(9):305-307.

编辑:jq

-

FPGA

+关注

关注

1664文章

22504浏览量

639296 -

数据

+关注

关注

8文章

7349浏览量

95025 -

FFT

+关注

关注

15文章

458浏览量

63234 -

MTI

+关注

关注

0文章

8浏览量

7757

发布评论请先 登录

使用单芯片 8 x 8 级联收发器实现 4D 雷达成像

详解FPGA定点数计算方法

pwm关闭后,有杂波怎么解决?

图达通通过港交所聆讯 前9月交付激光雷达超18万台

如何使用FPGA实现SRIO通信协议

AMG049-003多普勒雷达速度传感器

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

定华雷达仪表学堂:如何区别高频与低频雷达物位计性能比较?

ASP4644芯片在雷达FPGA供电系统中的适配与性能分析

4D毫米波雷达比3D毫米波雷达到底强在哪儿?

关于FPGA的雷达杂波速度谱图的实现方法

关于FPGA的雷达杂波速度谱图的实现方法

评论