因为最近事情还挺多的,有一段时间没有更新了,然后想想还是再积累一下再写新的文章,结果就一个月过去了。。。。所以避免拖延症继续发作还是写一篇一直想写的文章吧。

最近自己尝试搭建一个简单的验证平台,入门就先从简单开始!

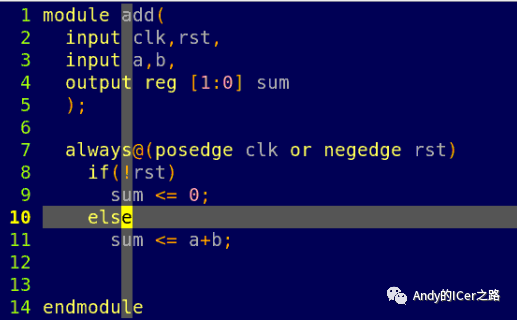

1 RTL设计

RTL就是一个带时序的1bit加法器,然后验证是否功能正确。理论上的正确功能应该是输入数据a和数据b之后的下个周期输出结果sum等于a+b。

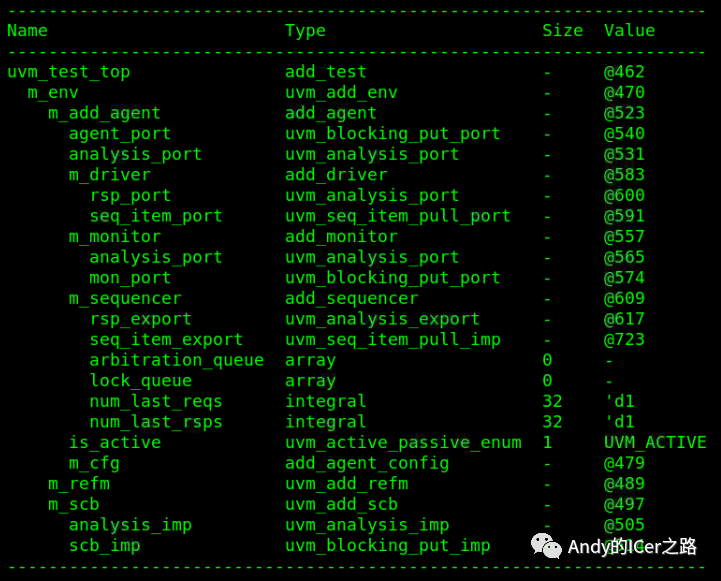

2 UVM验证平台建立

将整个UVM验证平台分为4个部分agent、env、test、tb,逐层递进,关于层次大小结构图可以看这篇文章,下图是整个验证平台的hierarchy。

AndyICer,公众号:Andy的ICer之路路由器的System Verilog验证平台

2.1 agent

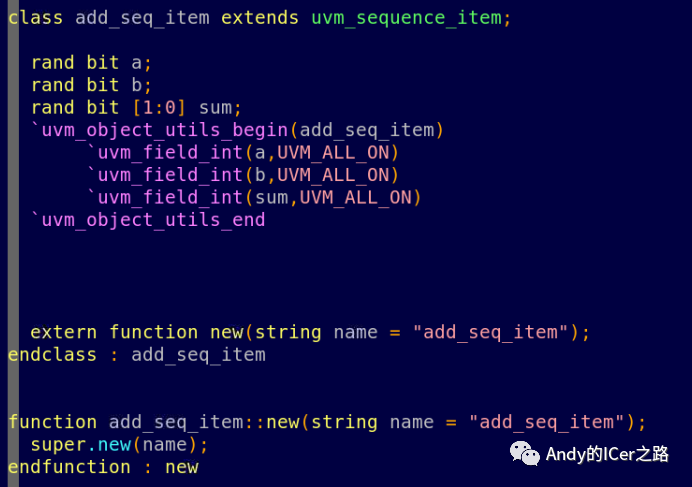

2.1.1 add_seq_item

首先建立一个transaction,即建立一个数据包。

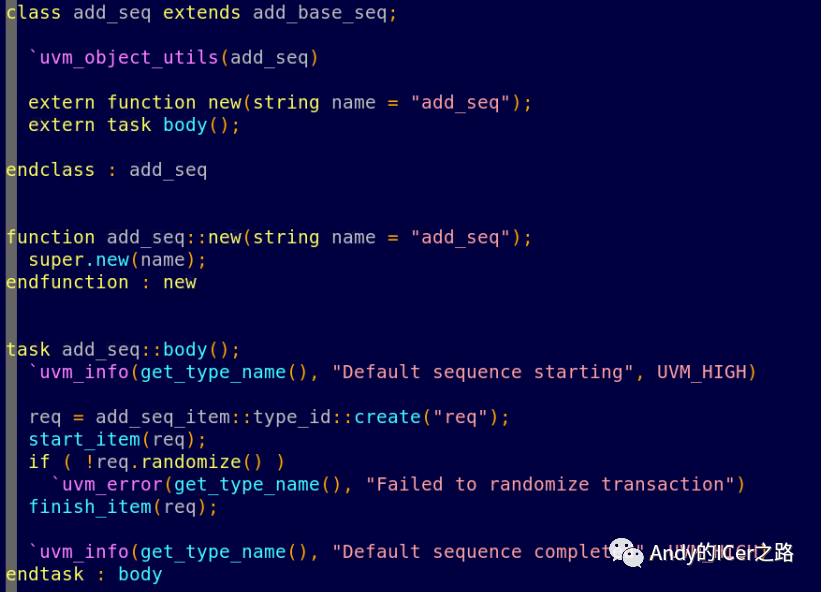

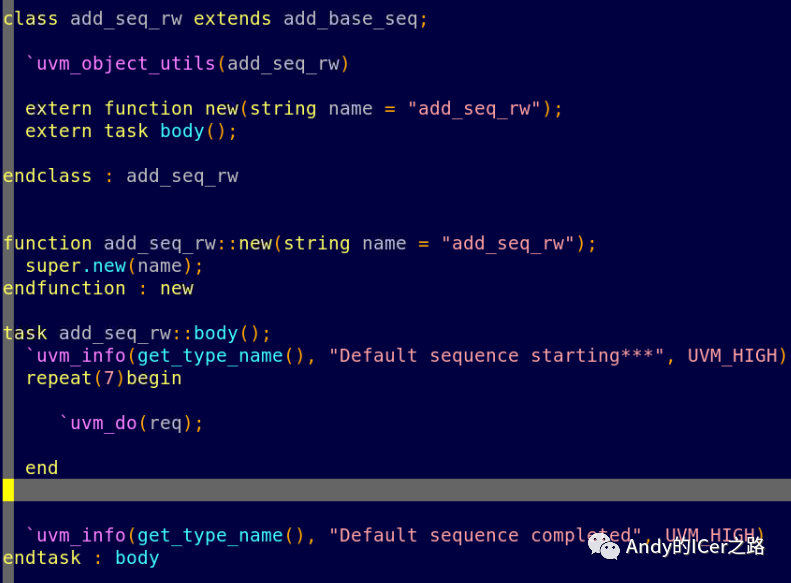

2.1.2 add_seq

建立一个sequence,用来发送transaction。发送transaction的方式有两种,一种是用start_item()和finish_item(),另外一种是用`uvm_do()的宏。但是两种方法的原理是一样的。

法一:

法二:

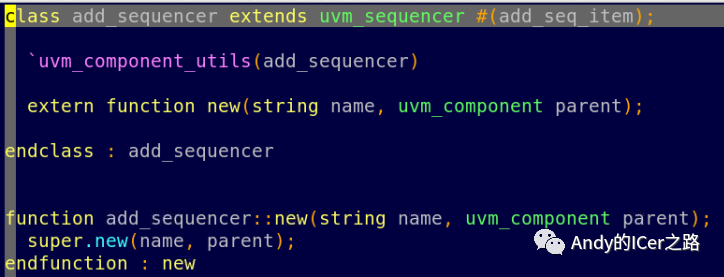

2.1.3 add_sequencer

建立一个sequencer用于与其他模块通信。

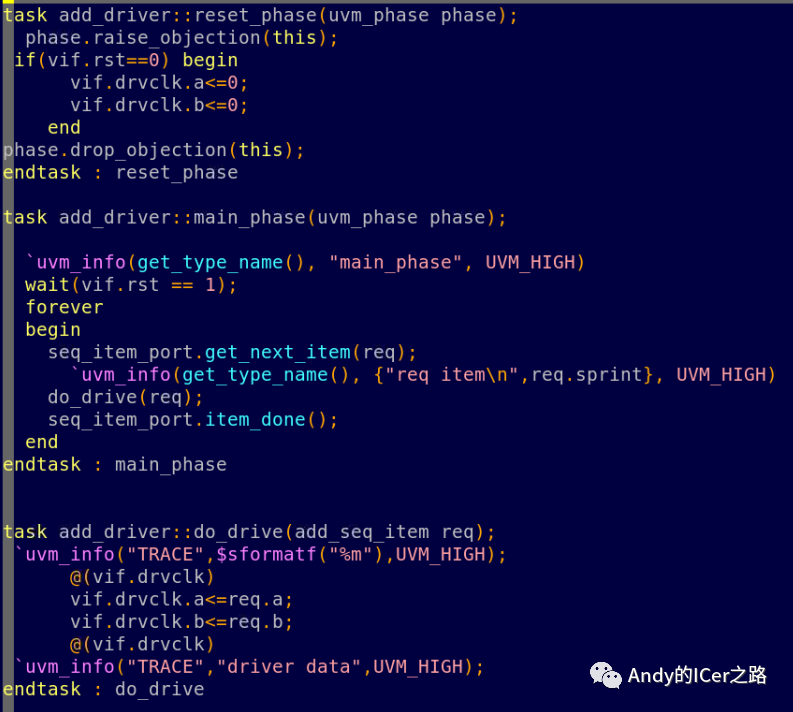

2.1.4 add_driver

driver模块进行给DUT传输数据,reset phase进行DUT复位,main phase进行激励输入。

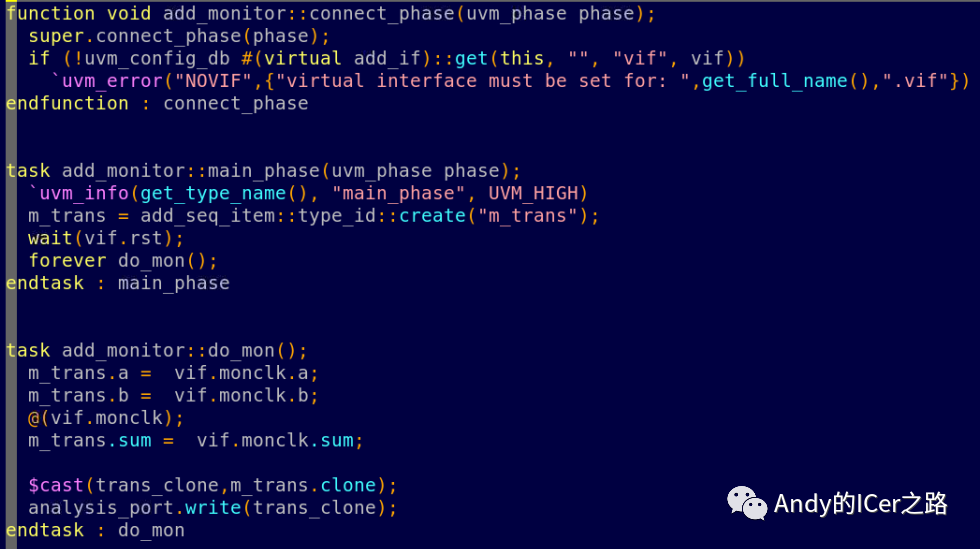

2.1.5 add_monitor

monitor模块接收DUT发来的数据,并通过TLM通信发送给scoreboard。

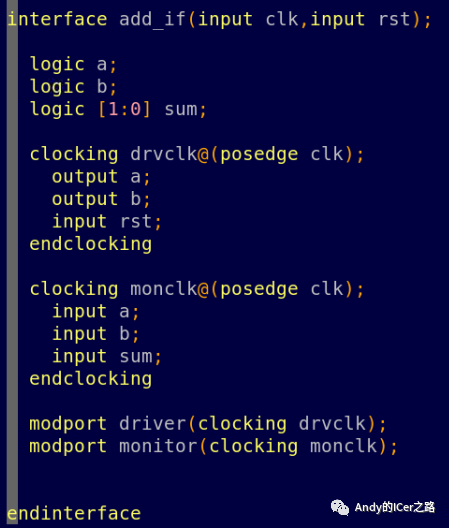

2.1.6 add_if

定义一个Interface,里面包含有两个clocking block,定义了driver和monitor接口的输入输出方向。

2.2 env

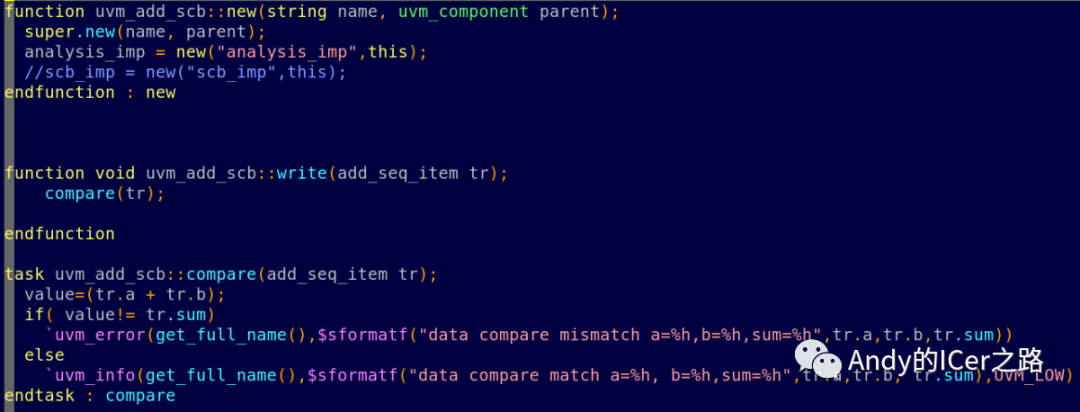

2.2.1 add_scoreboard

建立scoreboard,进行硬件结果和软件结果的对比。

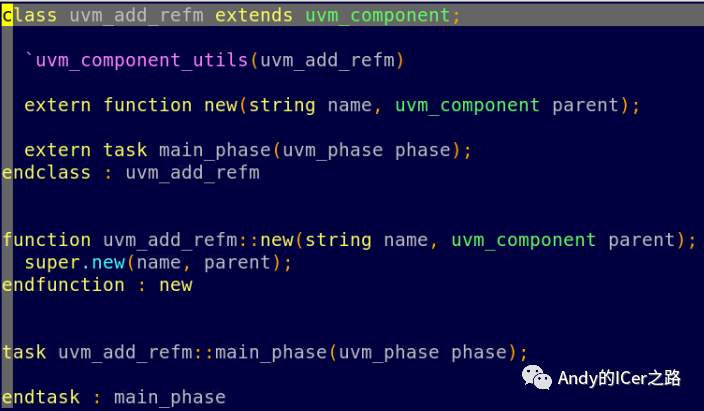

2.2.2 add_reference_model

这里的逻辑比较简单,就没有使用到reference model了,但是还是保留有这个模块。

2.2.3 add_env

env就是把agent、scoreboard、reference model都build并connect起来。

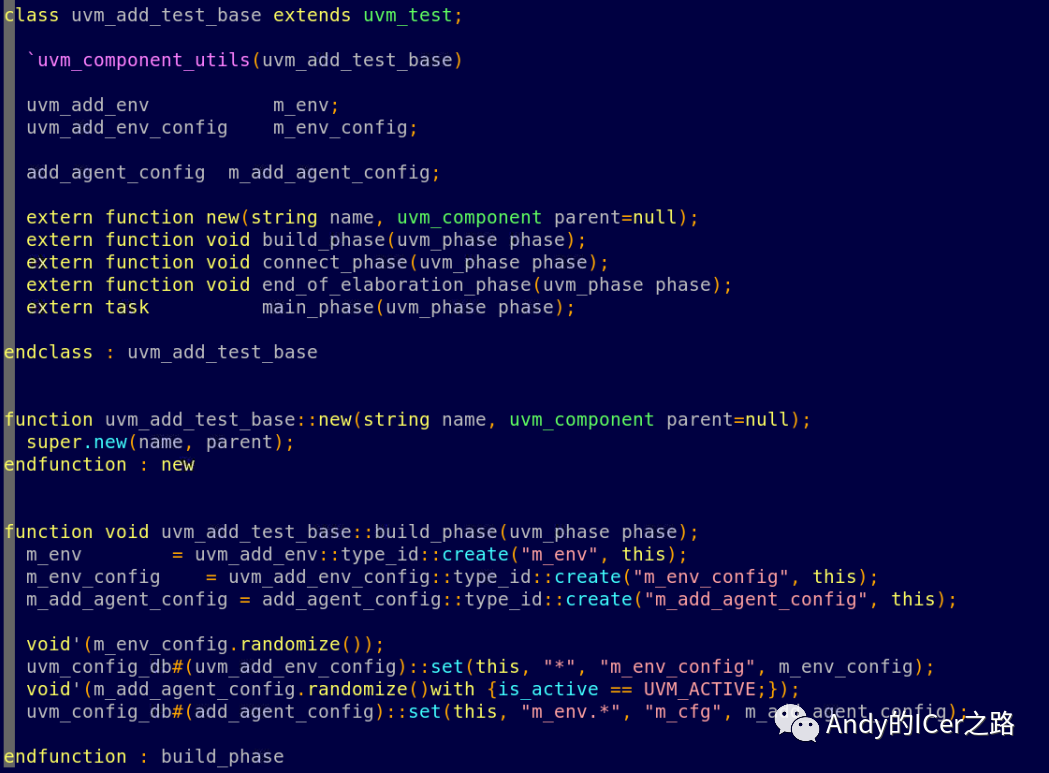

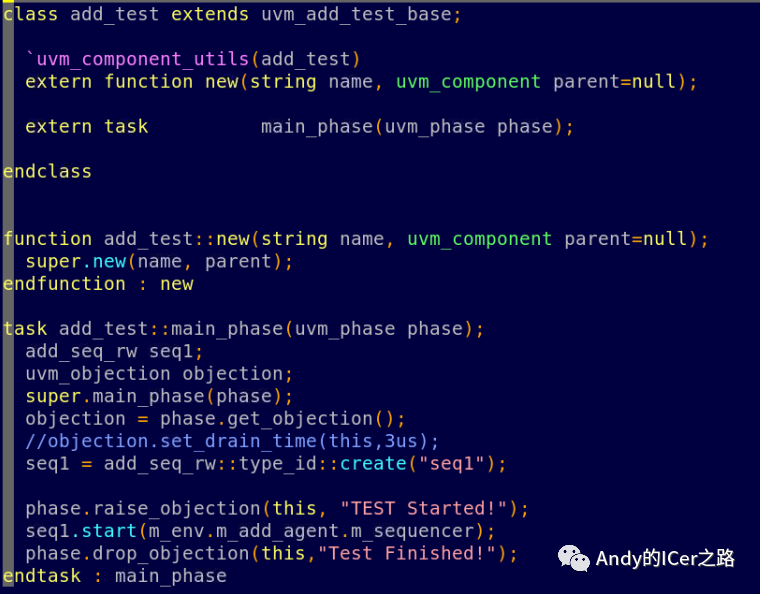

2.3 test

test是验证环境的顶层,顶层中将env建立好并将configure也建立好,在顶层中进行设置。

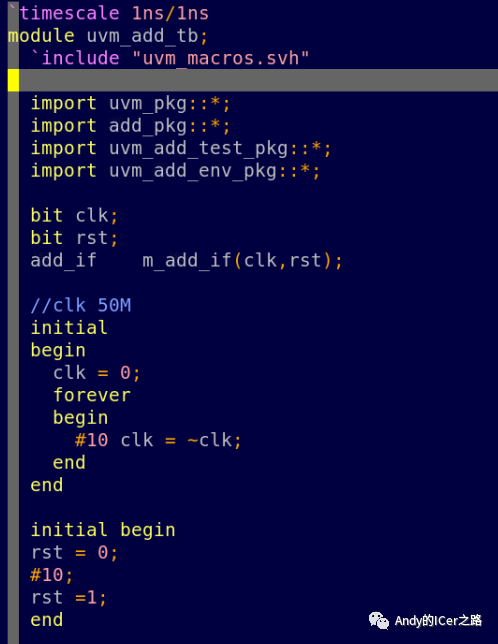

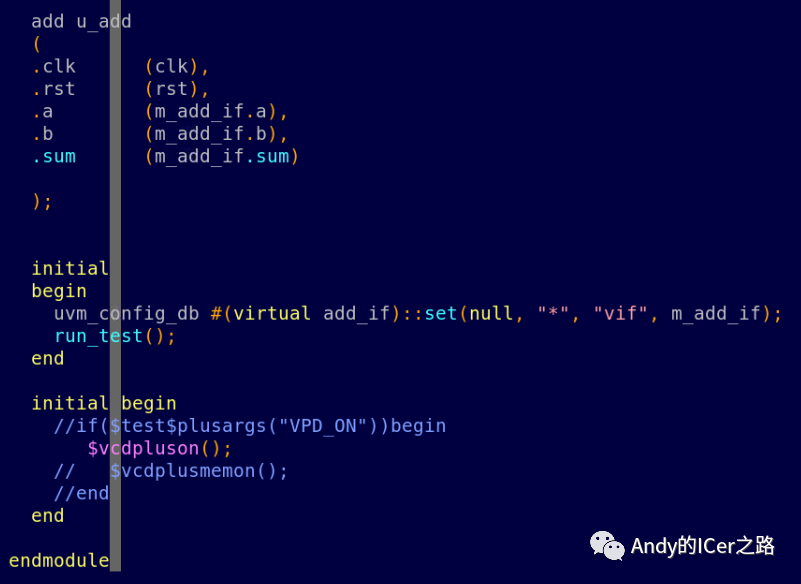

2.4 Testbench

将硬件DUT和软件验证环境联系起来,形成一个完成的测试平台。

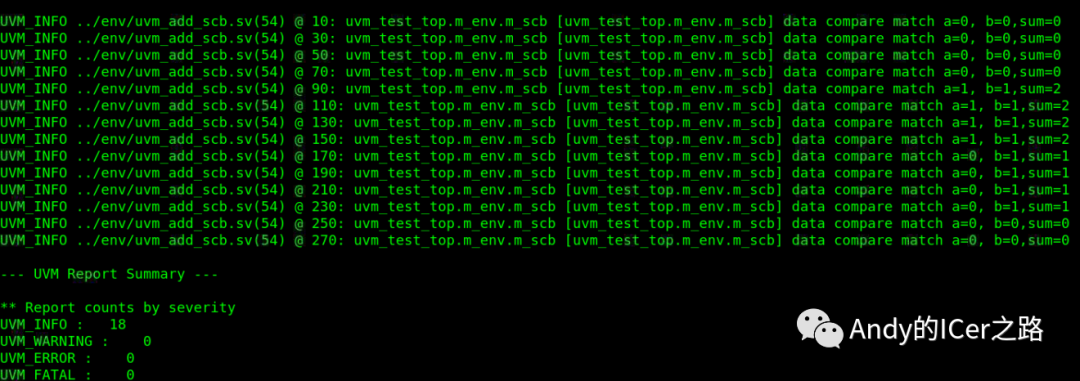

3 验证结果

可以看出验证功能正确,并且通过对于driver和monitor时序的调整可以控制输出结果的时序,大家也可以尝试搭建一个验证平台,对于UVM会有一个更加直观的感受。

编辑:lyn

-

加法器

+关注

关注

6文章

183浏览量

31543 -

UVM

+关注

关注

0文章

183浏览量

20095

原文标题:一个加法器的UVM验证平台设计

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CD54/74AC283与CD54/74ACT283:4位二进制加法器的技术解析

深度解析CD54/74AC283与CD54/74ACT283 4位二进制加法器

深入解析CD54/74AC283与CD54/74ACT283 4位二进制加法器

高速低功耗的利器:MC10H180双2位加法器/减法器

深入解析DM74LS83A 4位二进制快速进位加法器

深入剖析 DM74LS283:4 位快速进位二进制加法器

74F583 4位BCD加法器:高速运算的理想之选

十进制计算机算术运算器“加法器”专利申请解析

如何搭建一个加法器的UVM验证平台

如何搭建一个加法器的UVM验证平台

评论