介绍了PHILIPS公司的第二代实时MPEG-2编码芯片SAA6752的主要功能及性能特点,提出了一种基于SAA6752的MPEG-2编码系统,并且对该编码系统的硬件框图和软件编程进行了简要说明。

数字电视世界范围内得到了非常迅速的发展,电视广播的全部流程,即从节目的提摄、制作、传输到插出等正在逐步实现数字化。MPEG视频/音频压缩标准的出现,解决了电视信号数字化后信息量过大而信道带宽有限的问题;数字视频硬件产品的不断进步,促进了各种数字视频产品的推出,给观众带来了高品质的画面和音响效果。这一切,都预示着电视广播全面步入了数字化的时代。

目前世界上的数字电视系统标准有欧洲的DVB系统、美国的ATSC系统和日本的ISDB系统。这几种系统在视频压缩上都采用MPEG-2标准,我国也正在积极地制定自己的数字电视标准。本文将介绍PHILIPS公司生产的芯片SAA6752,它能在开发欧洲DVB标准常规数字电视和DVD的前端系统的产品过程中,实现MPEG-2编码。

1 SAA6752的主要特点

SAA6752又称为EMPRESS,是PHILIPS公司第二代实时MPEG-2编码芯片。它将音频、视频编码和复用集成在一个芯片中,具有很强的功能,外部只需加入简单的相关芯片就能实现整个编码系统,从而降低系统成本。同时,所有的视频、音频压缩算法都运行在EMPRESS的内部MIPS处理器上,编码软件都已固化在芯片中,无需额外的软件开发,系统主控芯片通过I2C总线就可以设定必要的编码参数。此外,由于它较好地解决了视频编码中的主要问题——噪音过滤和运动预测,所以可以在低码率情况下实现高品质视频编码,从而达到在存储介质上可以存储更多视频和音频信息的目的。

该芯片主要提供以下功能:

(1)视频压缩

·实时MPEG-2编码(符合MP@ML)

·支持分辨率:D1、2/3D1、1/2D1和SIF

·在所有模式下支持IPB、IP和I帧编码

·支持的码率:1.5~25Mbps(对于只有I帧编码)

1.5~15Mbps(对于只有IP帧编码)

1.5~15Mbps(对于只有IPB帧编码)

·支持CBR(Constant Bi Rate)和VBR(Variable Bit Rate)

·具有可编程的GOP(Grup of Picture)结构

(2)音频压缩

·AC-3音频编码:码率为256kbps或385kbps

·MPEG-1 Layer2音频编码(16或20位):码率为256kbps或384kbps

(3)系统复用

·符合MPEG系统标准(ISO 13818-1)的视频和音频流的复用

·产生和输出符合DVD、D-VHS和DVB标准的MPEG-2传输流(TS)、MPEG-2节目流(PS)、打包的基本流(PES)和基本流(ES)

·产生和插入MPEG时间标记(PTS/DTS/SCR/PCR)

2 基于SAA6752的MPEG-2编码系统

2.1 系统框图

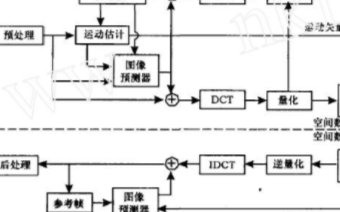

因为SAA6752没有片内CPU,为了实现编码功能,所以必须由一个片外CPU对其进行控制。而对SAA6752的所有控制(例如码率控制、PS流和TS流输出等)均是通过I2C总线完成的,因而非常简单。图1给出了基于SAA6752的MPEG-2编码系统的方框图。

该编码系统主要分为视频输入部分、音频输入/输出部分、EMPRESS部分、复位部分、输出接口、电源部分以及I2C和UART接口。

2.1.1 视频输入部分

视频输入部分提供两路模拟输入接口,一路为CVBS信号,另一路为YC信号。该部分可以由PHILIPS SAA7114完成,对其所有的控制均通过I2C总线完成。

2.1.2 音频输入/输出部分

由于EMPRESS提供了音频I2S接口,该部分主要完成模拟拟音频转换为数字音频12S信号的功能。

2.1.3 EMPRESS部分

由于SAA6752采用多个处理器模块,各个处理器和控制模块之间相互独立,所以模块之间的数据传送主要通过FIFO存储器或外部SDRAM来实现。该系统采用16Mbit或64Mbit SDRAM。EMPRESS SAA6752可以产生打包的基本流,其码流可以根据不同的应用进行设定,一种是对应于DVD格式的PES流,其码诣可变的;另一种是对应于TS的PES流,其码率是恒定的。

2.1.4 复位部分

该系统提供两种复位方式:一种是硬复位;另一种是利用I2C控制软件实现软复位。

2.1.5 输出接口部分

该系统提供两种TS并行输出接口:一种是TTL接口;另一种是标准LVDS接口。

2.2 软件编程

为了控制EMPRESS的编码,I2C接口线被用来将该系统与计算机相连以实现计算机控制EMPRESS芯片的目的,同时初始化SAA7114。所有的相关操作均是通过I2C总线访问寄存器实现的。在I2C控制软件中,需要确定EMPRESS和SAA7114的I2C读写地址。

EMPRESS的I2C读写地址:

(1)当EMPRESS的I2C选择信号为低时,其I2C写地址为40H,读地址为41H。

(2)当EMPRESS的I2C选择信号为高时,其I2C写地址为42H,读地址为43H。

SAA7114的I2C读写地址:

(1)当SAA7114的I2C选择信号为低时,其I2C写地址为40H,读地址为41H。

(2)当SAA7114的I2C选择信号为高时,其I2C写地址为42H,读地址为43H。

为了防止EMPRESST和SAA7114的I2C地址发生冲突,将EMPRESS的I2C选择信号设置为低电平,则EMPRESS的I2C写地址定义为40H;将SAA7114的I2C选择信号设置为高电平,则SAA7114的I2C写地址定义为42H。

控制软件应实现以下的I2C接口函数:

(1)Void I2C_Read_One_Byte(int address,int subaddress,int value)

该函数主要实现对给定寄存器一个字节的读取,address确定需要访问的芯片,subaddress确定需要访问的寄存器,value为返回寄存器值。

(2)I2C_Write_One_Byte(int address,int subaddress,int value)

该函数主要实现对给定寄存器一个字节的写入,address确定需要访问的芯片,subaddress确定需要访问的寄存器,value为要写入寄存器值。

(3)I2C_Read_Muiti_Bytes(int address,int subaddress,int count,int *buffer)

该函数主要实现对给定寄存器多个字节的读取,address确定需要访问的芯片,subaddress确定需要访问的寄存器,buffer为返回多个寄存器值。

(4)I2C_Write_Multi_Bytes(int address,int subaddress,int count,int *buffer)

该函数主要实现对给定寄存器多个字节的写入,address确定需要访问的芯片,subaddress确定需要访问的寄存器,buffer为要写入多个寄存器值。

通过调用这些函数,就可由I2C接口为EMPRESS和SAA7114的片内寄存器进行设置。

使用I2C控制软件,可以任意修改参数(PID、码率等)产生和输出所需要的TS、PS、PES、ES流。在设定输出码率为5~9Mbit/s时,可以得到较高品质的视频图像。

SAA6752采用噪声过滤和运动估计技术,使得基于SAA6752的MPEG-2编码系统在低码率压缩情况下,对于有干扰的输入信号仍能提供高质量编码效果。这特别适合于以较低码率压缩的作用,例如DVD视频刻录和个人视频刻录(Personal Video Recording)。

在保证高编码质量的同时,基于SAA6752的MPEG-2编码系统设计非常简单,易于实现。当使用该芯片设计MPEG-2编码系统时,只需在外围添加视频模/数转换芯片、音频模/数转换芯片和外部SDRAM,普通的模拟视频和音频信号就可以被压缩成高质量的MPEG-2视频流和MPEG-1 layer2或AC-3音频流,复用成为PS或TS,提供给存储或广播媒介。由于所有的视频和音频编码算法和软件都是运行在片内处理器中,因而只需较少的系统控制资源。而主控芯片只要通过I2C总线设置编码参数即可,无需用户具有较多的MPEG编码经验或投入过多的设计成本,缩短了设计周期。

因此,用SAA6752设计低成本高品质的编码系统,可以被广泛应用于新的消费类数字视频产品中。

责任编辑:gt

-

处理器

+关注

关注

68文章

20332浏览量

254919 -

芯片

+关注

关注

463文章

54422浏览量

469266 -

数字电视

+关注

关注

3文章

326浏览量

47059

发布评论请先 登录

基于SAA6752HS芯片和TMS32VC5502实现MPEG-2视频编码系统的设计

MPEG-2压缩编码技术原理应用

分析一款不错的基于SAA6752的MPEG-2的编码系统

基于MIPS体系结构的嵌入式MPEG-2音视频解码设计

MPEG-2系列编码器

SUNNISKY ENC1000视音频MPEG-2压缩编码器

5300系列MPEG-2高清模块MediaPort

SD3000标清编码器SD MPEG-2 Encoder

嵌入式MPEG-2远程网络视频监控系统的实现

基于MPEG-2编码芯片SAA6752实现应用系统的设计

基于MPEG-2编码芯片SAA6752实现应用系统的设计

评论