昨晚AMD发布了RX 6700 XT显卡,这是RDNA2架构家族第二波产品,国内售价3699元,针对友商的RTX 3070显卡。

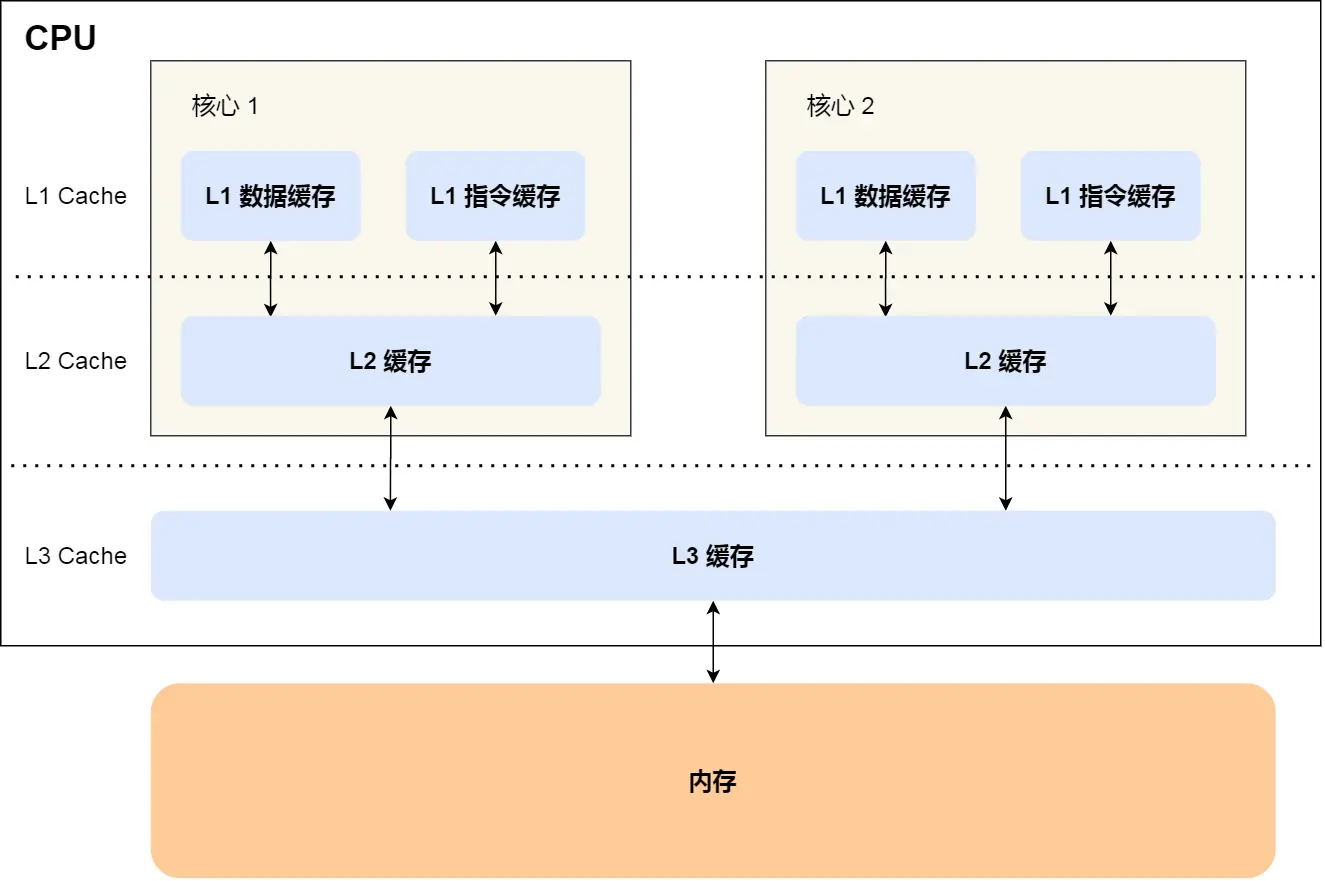

在AMD的RDNA2架构中,有一项独特的技术很重要,那就是Infinity Cache(无限缓存),这是一种高速缓存,灵感来自于Zen架构CPU,它能够以低功耗和低延迟提供卓越的带宽性能。

整个显卡核心均可访问此全局高速缓存,有助于捕捉即时的重用机会,从而能够快速访问数据。

根据AMD的说法,Infinity Cache 充当着海量带宽放大器的角色,实现的有效带宽最高可达256位16Gbps GDDR6的3.25 倍。

在RX 6800/6900系列显卡上,AMD就靠着128MB Infinity Cache+ 256bit GDDR6 显存的方案相比传统的 384bit GDDR6 显存带宽翻倍,而且功耗还更低。

在RX 6700 XT的Navi 22核心上,AMD的Infinity Cache砍了一部分,只剩下96MB,匹配192bit位宽。

未来还会有Navi 23核心,显卡对应的应该是RX 6600系列,那它的Infinity Cache技术会不会砍掉呢?毕竟成本还是挺高的。

答案是不会,已经有网友在Linux代码中发现了线索,Navi 23会给每个显存通道分配4MB Infinity Cache缓存,而显卡应该是128bit位宽,也就是8个32bit GDDR6,所以Infinity Cache容量会减少到32MB。

总之,这个技术对提高带宽很有帮助,虽然成本高了点,但AMD依然会保留在低端的Navi 23核心上,RX 6600系列显卡也不会阉割太狠。

责编AJX

-

amd

+关注

关注

25文章

5707浏览量

140402 -

显卡

+关注

关注

17文章

2523浏览量

71717 -

缓存

+关注

关注

1文章

248浏览量

27812

发布评论请先 登录

忆联自研芯片以压缩技术重塑KV Cache存储效率

京东缓存中间件架构与缓存内核优化

KeepAlive:组件缓存实现深度解析

C语言的缓冲区(缓存)详解

从NOR转向使用CS SD NAND:为什么必须加入缓存(Cache)机制?

AMD UltraScale架构:高性能FPGA与SoC的技术剖析

串口DMA发送有缓存吗?

今日看点丨华为发布AI推理创新技术UCM;比亚迪汽车出口暴增130%

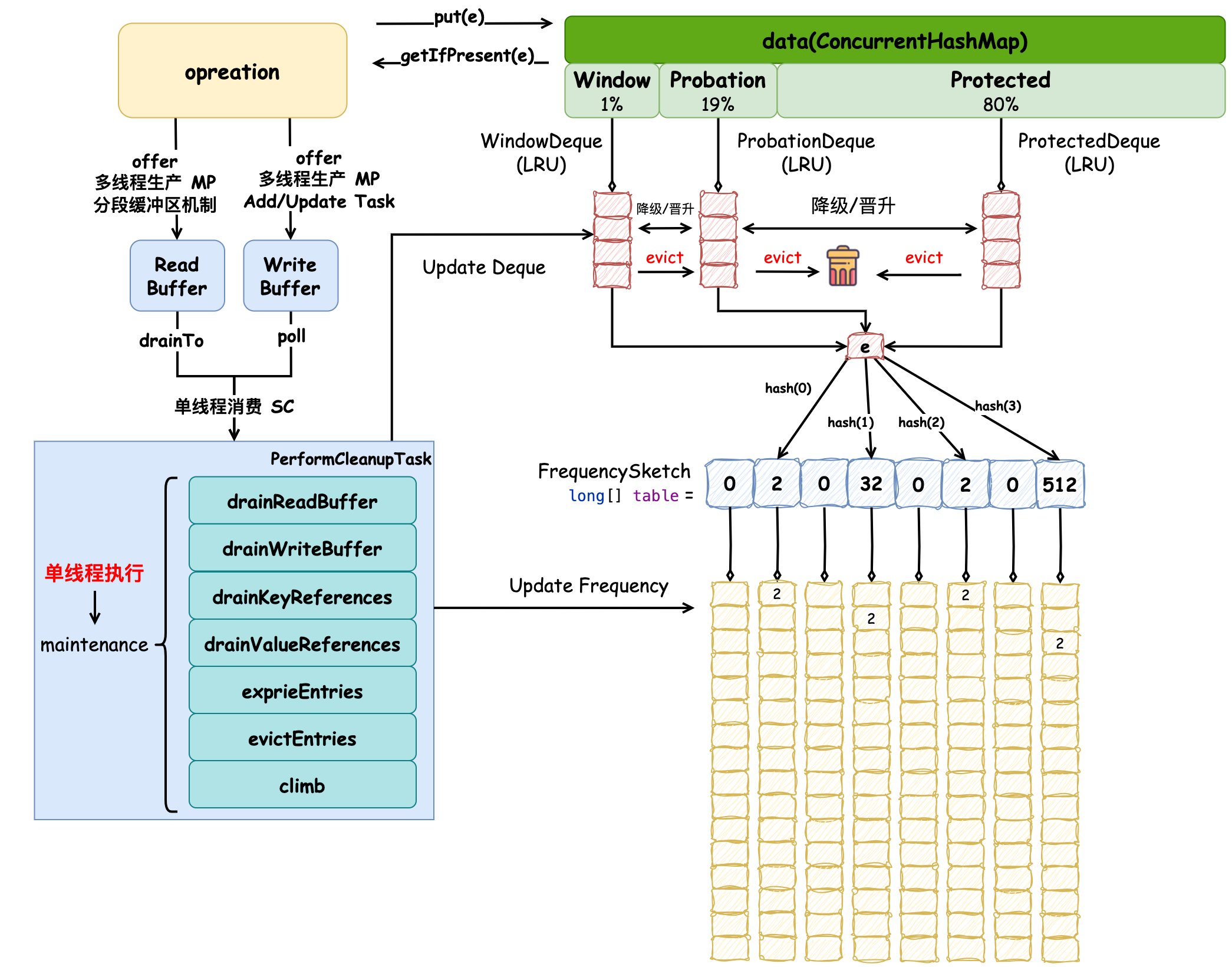

缓存之美:万文详解 Caffeine 实现原理(上)

高性能缓存设计:如何解决缓存伪共享问题

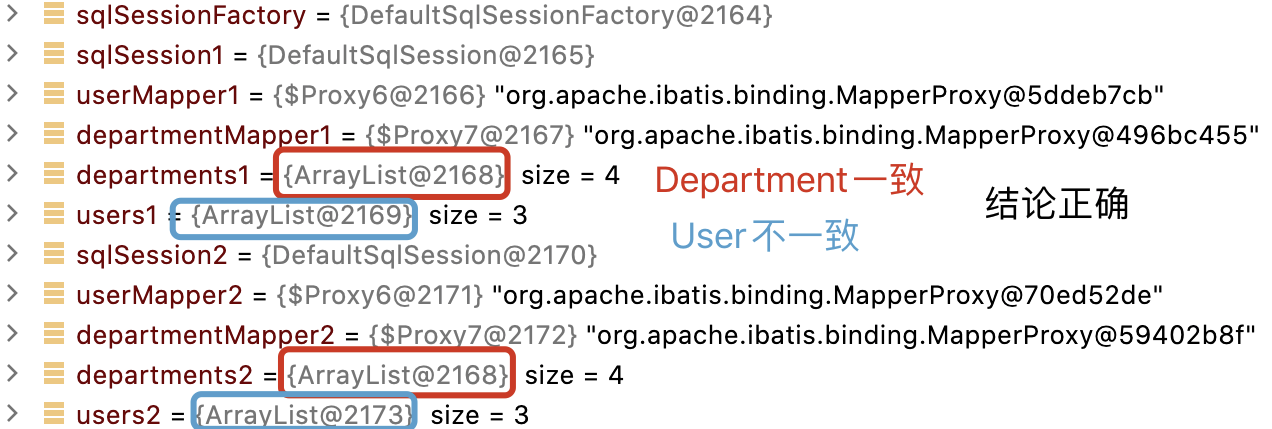

由 Mybatis 源码畅谈软件设计(八):从根上理解 Mybatis 二级缓存

AMD承诺不会砍掉Infinity Cache缓存技术

AMD承诺不会砍掉Infinity Cache缓存技术

评论