sparc体系架构的窗口寄存器的深入理解

1.概述

2.窗口寄存器的特性

3.程序的设计

1.概述

sparc这种架构有着特殊的窗口寄存器,使用sparc芯片,一定会对这种窗口寄存器产生疑惑,然而这种硬件特性却让软件设计有着更加独特的方式。下面来描述一下sparc架构中这种串口寄存器的特性以及编程模型。

采用窗口寄存器,可以减少函数调用过程中返回时间,因为通过硬件进行压栈操作时,可以减少指令条数以及减少访问存储器的次数。

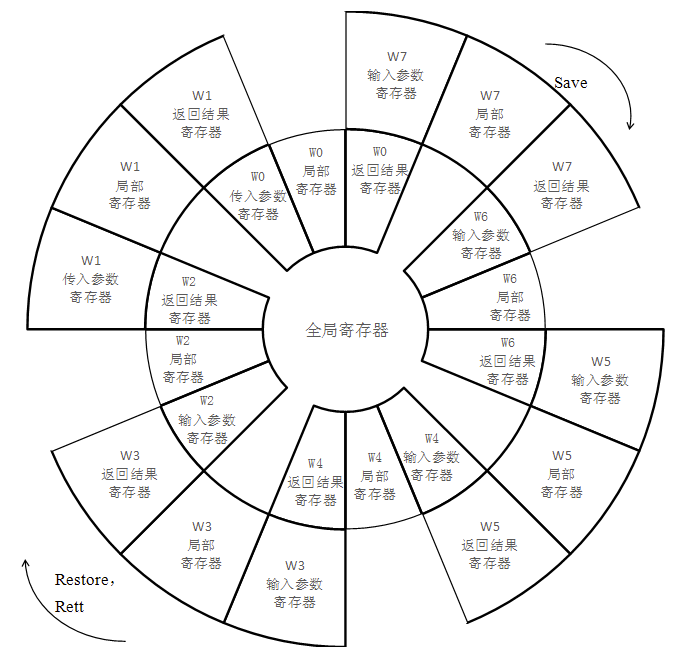

窗口寄存器的本质是每当执行一次函数调用过程时,寄存器窗口会自动的指向下一个窗口,当子程序返回时,也不需要额外的出栈操作,只是将窗口偏移到上个寄存器即可。

而两个相邻的窗口则有重叠部分,可以对两个父子函数之间进行参数传递,这样大大的提高了访问的效率以及寄存器的专一性。

2.窗口寄存器的特性

当在实际的程序中使用时,往往会涉及到多个函数的嵌套,这些在复杂程序设计上非常的普遍,业务逻辑的增加会显著的增加函数调用的深度。如果函数调用超过了这些8个窗口,sparc架构又是该如何处理呢?

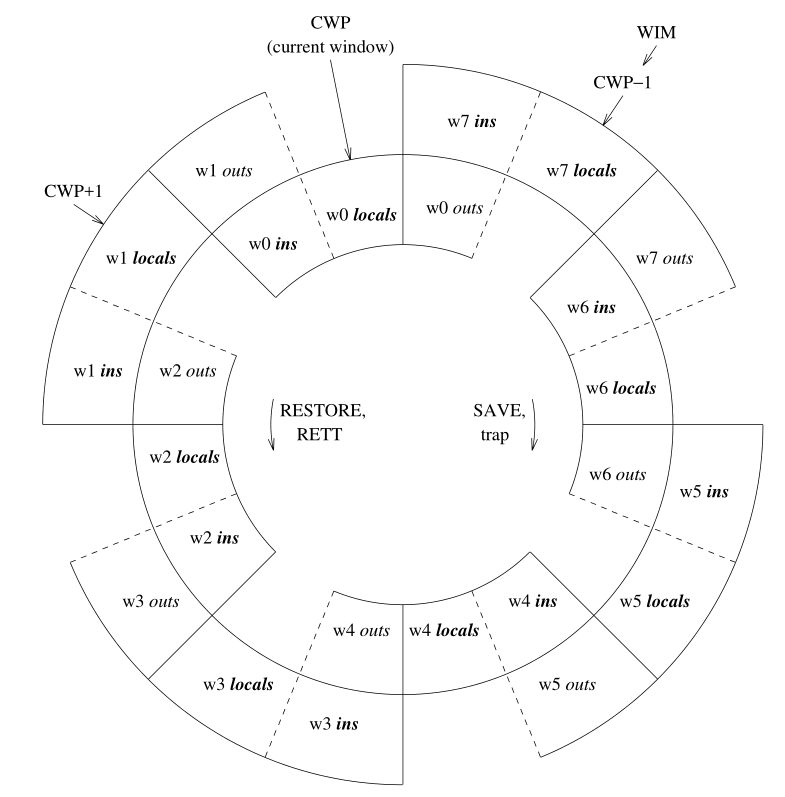

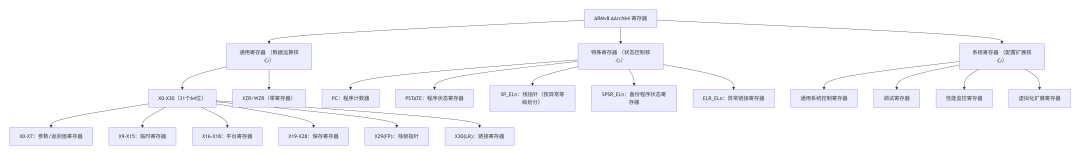

在sparc的架构中,CWP(当前窗口指针)是PSR(程序状态寄存器)的一部分,在某一固定的时刻,处理器中都只会有32个整数寄存器可以被使用。这32个寄存器为8个全局寄存器、8个返回结果寄存器、8个局部寄存器、8个输入寄存器。CWP通常会因SAVE指令(SAVE指令一般在过程调用时使用,用来开辟新的栈帧并切换寄存器窗口)而减一,因RESTORE指令(在从过程中返回前切换回调用者的寄存器窗口)而加一,陷阱事件(中断,异常或TRAP指令)和RETT指令(从陷阱中返回)也会改变CWP,不过函数调用比陷阱更为常见。

窗口无效掩码(WIM) WIM指示了哪个窗口是无效的,无效的意思是该窗口保存了调用者的信息所以不可再使用,上图中,WIM指向w7,而CWP指向w0,所以现在如果执行一条SAVE指令,则会触发窗口溢出陷阱,反之,如果CWP指向w0且又执行了一条RESTORE指令,则会触发窗口下溢陷阱。

所谓的窗口下溢则是说当前窗口不够用了,需要将已经满了的窗口寄存器的数据压入到栈上,也就是内存中,压入后的窗口寄存器又可以重新利用起来了,而上个满了的窗口寄存器则存在内存中了。当函数返回到窗口无效寄存器时,则发生上溢陷阱,该陷阱中会执行出栈的操作,从而将寄存器进行恢复。

3.程序的设计

对于C语言来说,并不用关注架构的不同带来的差异性,而对于汇编来说,则设计却是完全的不同。GCC已经处理好了C转换成汇编的逻辑。

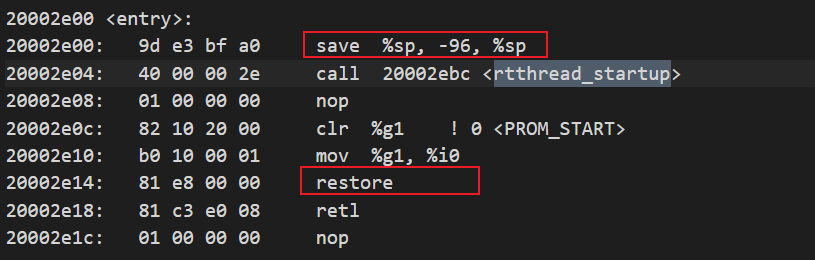

每个save指令都是在被调用的函数的第一条指令处开始执行。而SAVE的指令与ADD的指令相同,其功能是可以将sparcCWP减一。让CWP-1窗口成为新的当前的窗口。

当函数执行完成后,则执行restore指令,让窗口指令加一。窗口就回归原位了。

4.sparc设计对于嵌入式编程的优劣

对于嵌入式来说,如果只设计可控的程序,逻辑设计上尽可能的单一可控,并且最好函数的嵌套深度不应该超过8个,最好不发生上溢或者下溢操作。这样不用访问存储器,并且底层的指令很少,对于程序的执行效率很有保障。有上溢或者下溢,一次性就需要压栈或者出栈操作,使得其程序的执行效率不在那么高效。

而对于rtos来说,设计上也稍微复杂了一些,需要不仅需要判断当前窗口的溢出情况,还需要保存窗口寄存器的栈,这样对于系统上下文的线程栈需要的空间消耗是非常大的。目前也没有想到合适方式去减少栈的消耗,而且在rtos上,sparc架构所占的优势并不是很明显,以上仅仅是我对这种架构在嵌入式上使用的一些看法。

总结起来,sparc架构的好处是由于有了窗口寄存器模型,如果程序设计的优秀简单,这个是非常好的,效率也可以非常高,简洁的寄存器、简洁的控制状态,需要编程人员要有很高的水平。缺点就是不考虑sparc架构的编程方式,将会使得程序的效率非常的低下,sparc芯片的使用也变得十分的困难。

责任编辑:xj

原文标题:sparc体系架构的窗口寄存器的深入理解

文章出处:【微信公众号:嵌入式IoT】欢迎添加关注!文章转载请注明出处。

-

寄存器

+关注

关注

31文章

5619浏览量

130422 -

窗口

+关注

关注

0文章

66浏览量

11313 -

SPARC

+关注

关注

0文章

16浏览量

10186

原文标题:sparc体系架构的窗口寄存器的深入理解

文章出处:【微信号:Embeded_IoT,微信公众号:嵌入式IoT】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

深入解析SN74SSTVF16857 14位寄存器缓冲器

深入解析SN74SSTU32864D:25位可配置寄存器缓冲器

深入解析SN74SSTV16857 14位寄存器缓冲器

SN74SSTV16857:14位寄存器缓冲器的技术剖析

深入解析 SSTV16859:双输出 13 位寄存器的卓越性能与应用

深入理解积分型ADC

74AHC594:8位移位寄存器的详细解析与应用

74HC595 8位移位寄存器:设计与应用全解析

74LV595A:8位移位寄存器的全方位解析

深入剖析74HCT595:8位移位寄存器的卓越之选

深入解析STPIC6D595:8位移位寄存器的卓越性能与应用

深入解析CY74FCT399T:一款高性能的四2输入寄存器

从“能用”到“懂原理”:ARMv8寄存器架构深度拆解

LAT1170+如何理解 RAMECC FAR 寄存器的值

使用寄存器点亮LED灯

sparc体系架构的窗口寄存器的深入理解

sparc体系架构的窗口寄存器的深入理解

评论