FinFET晶体管架构是当今半导体行业的主力军。但是,随着器件的持续微缩,短沟道效应迫使业界引入新的晶体管架构。在本文中,IMEC的3D混合微缩项目总监Julien Ryckaert勾勒出了向2nm及以下技术节点发展的演进之路。在这条令人振奋的道路上,他介绍了Nanosheet晶体管,Forksheet器件和CFET。其中一部分内容已在2019 IEEE国际电子器件会议(IEDM)上发表。

FinFET:今天最先进的晶体管

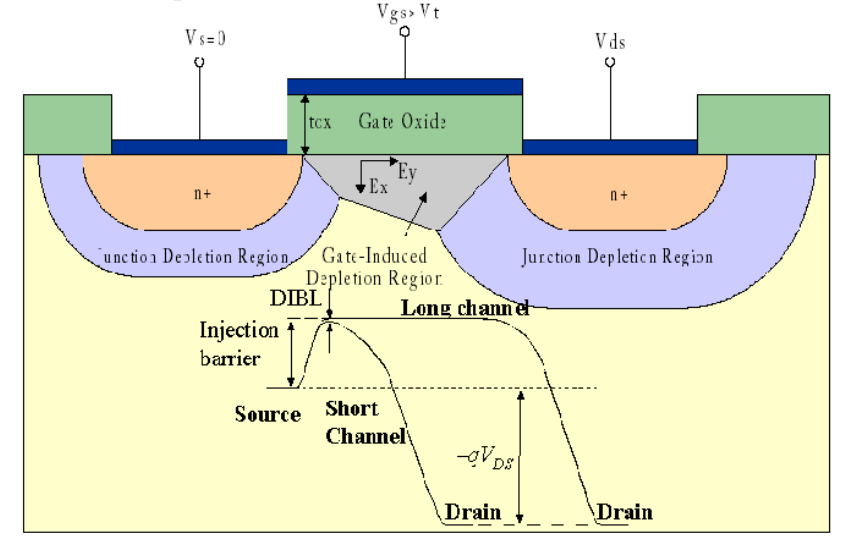

在每一代新技术上,芯片制造商都能够将晶体管规格微缩0.7倍,从而实现15%的性能提升,50%的面积减小,40%的功耗降低以及35%的成本降低。几年前,业界为了维持这种微缩路径,从“老式”平面MOSFET过渡到FinFET晶体管架构。在FinFET中,源极和漏极之间的沟道为fin的形式。栅极环绕该3D沟道,可从沟道的3个侧面进行控制。这种多栅极结构可以抑制在栅极长度降低时带来的短沟道效应。

出色的短沟道控制能力至关重要,因为它奠定了器件微缩的基础,允许更短的沟道长度和更低的工作电压。

2012年,首款商用22nm FinFET面世。从那时起,FinFET体系结构进行了持续的改进,以提高性能并减小面积。例如,FinFET的3D特性允许增加fin片高度,从而在相同的面积上获得更高的器件驱动电流。如今,业界正在加快生产的10nm / 7nm芯片也是基于FinFET。在最先进的节点的标准单元大多是6T单元高度,也就是是每个器件最多拥有2根fin。

Nanosheet:器件进化第一步

但是,随着工艺微缩至5nm节点,FinFET架构可能不再是主流。在沟道长度小到一定值时,FinFET结构又无法提供足够的静电控制。最重要的是,向低轨标准单元的演进需要向单fin器件过渡,即使fin高度进一步增加,单fin器件也无法提供足够的驱动电流。

随着技术节点的不断变化,半导体行业并不急于转向其他晶体管架构。一些公司甚至可能决定在某些节点停留更长的时间。但是,仍然存在需要最新的“通用” CMOS解决方案的应用,例如机器学习,大数据分析和数据中心服务器。通过这种通用CMOS解决方案,可以在相同技术节点中使用相同的晶体管架构来实现芯片上所有的功能。

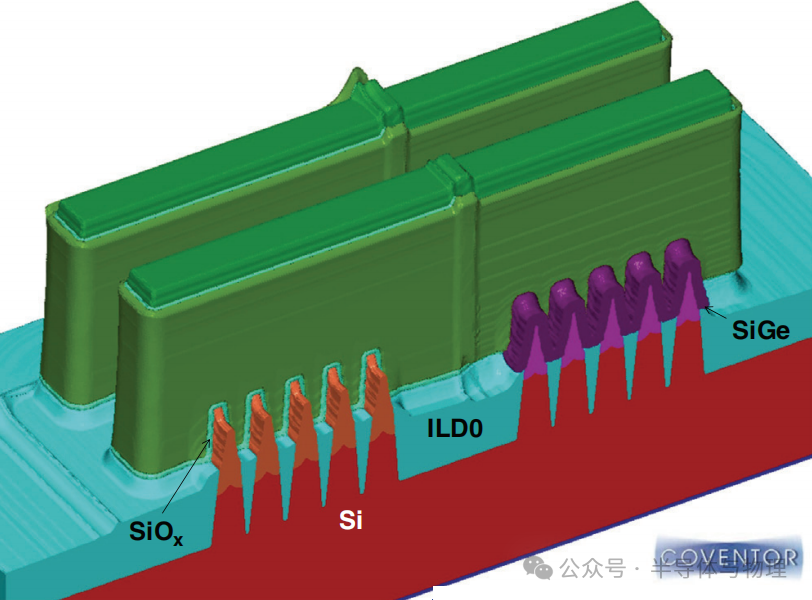

在这里,Nanosheet可以来帮助解围。Nanosheet可以被视为FinFET器件的自然演变版本。想象一下将FinFET的沟道水平切割成多个单独Nanosheet沟道,栅极也会完全环绕沟道。与FinFET相比,Nanosheet的这种GAA特性提供了出色的沟道控制能力。同时,沟道在三维中的极佳分布使得单位面积的有效驱动电流得以优化。

从FinFET到Nanosheet的自然演变。

需要微缩助推器

在6T和5T的低单元高度下,向Nanosheet器件的迁移变得最佳,因为在这种情况下,fin的减少会降低传统基于FinFET的单元中的驱动电流。

但是,如果不引入结构化微缩助推器(如埋入式电源轨和环绕式接触),就无法将单元高度从6T减小到5T。

电源轨为芯片的不同组件提供电源,并且一般由BEOL中Mint和M1层提供。但是,它们在那里占据了很大的空间。在嵌入式电源轨结构中,电源轨埋在芯片的前段,以帮助释放互连的布线资源。此外,它们为采用节距微缩而增加BEOL电阻的技术提供了较低的电阻局部电流分布。BEOL没有电源轨后,可以将标准单元的高度从6T进一步降低到5T。

下一步:缩小p和n之间的间距

随着走向更小的轨道高度的旅程的继续,单元高度的进一步减小将要求标准单元内nFET和pFET器件之间的间距更小。但是,对于FinFET和Nanosheet而言,工艺限制了这些n和p器件之间的间距。例如,在FinFET架构中,通常在n和p之间需要2个dummy fin的间距,这最多消耗总可用空间的40-50%。

为了扩大这些器件的可微缩性,IMEC最近提出了一种创新的架构,称为Forksheet器件。Forksheet可以被认为是Nanosheet的自然延伸。

与Nanosheet相比,现在沟道由叉形栅极结构控制,这是通过在栅极图案化之前在p和nMOS器件之间引入“介电墙”来实现的。该墙将p栅沟槽与n栅沟槽物理隔离,从而允许更紧密的n到p间距。

从FinFET到Nanosheet再到Forksheet的自然演变。

用于制造Forksheet的工艺流程与用于制造Nanosheet的工艺流程相似,仅增加一些额外的工艺步骤。n和p之间的介电隔离还具有一些工艺优势,例如填充功函数金属的工艺更简化。在此基础上,由于大幅减少了n到p的间距,预计该Forksheet具有更佳的面积和性能的可微缩性。

Forksheet工艺流程中的关键步骤,即有源区形成后“介电墙”的形成步骤。

-

半导体

+关注

关注

336文章

29985浏览量

258297 -

IC设计

+关注

关注

38文章

1369浏览量

107914 -

晶体管

+关注

关注

78文章

10257浏览量

146285

发布评论请先 登录

从模拟到数字——电话配线架的技术演进

JEDSD204B标准verilog实现-协议演进

突破边界:先进封装时代下光学检测技术的创新演进

OpenTenBase技术创新与演进分论坛成功举办

体硅FinFET和SOI FinFET的差异

动态IP技术演进:从网络基石到智能连接时代的创新引擎

华为成功举办5G-A产业演进峰会

从CPU到GPU:渲染技术的演进和趋势

FinFet Process Flow-源漏极是怎样形成的

FinFet Process Flow—哑栅极的形成

后FinFET时代的技术演进说明

后FinFET时代的技术演进说明

评论