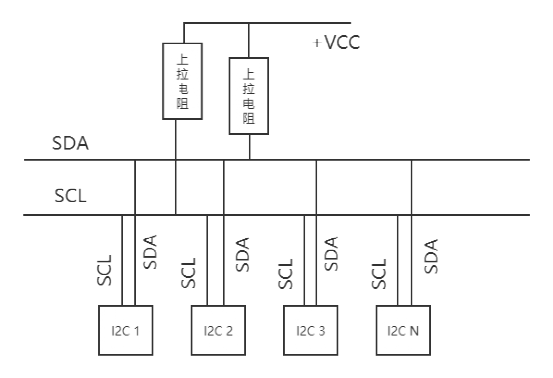

i2c上拉电阻大小

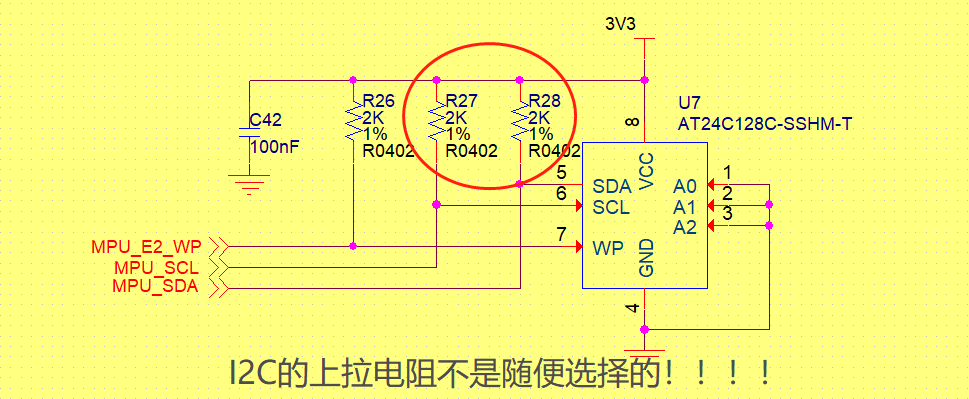

I2C的上拉电阻可以是1.5K,2.2K,4.7K, 电阻的大小对时序有一定影响,对信号的上升时间和下降时间也有影响,一般接1.5K或2.2K。

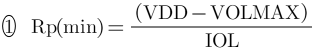

I2C上拉电阻确定有一个计算公式:

Rmin={Vdd(min)-o.4V}/3mA

Rmax=(T/0.874) *c, T=1us 100KHz, T=0.3us 400KHz

C是Bus capacitance

Rp最大值由总线最大容限(Cbmax)决定,Rp最小值由Vio与上拉驱动电流 (最大取3mA) 决定;

于是 Rpmin=5V/3mA≈1.7K(@Vio=5V)或者2.8V/3mA≈1K(@Vio=2.8V)

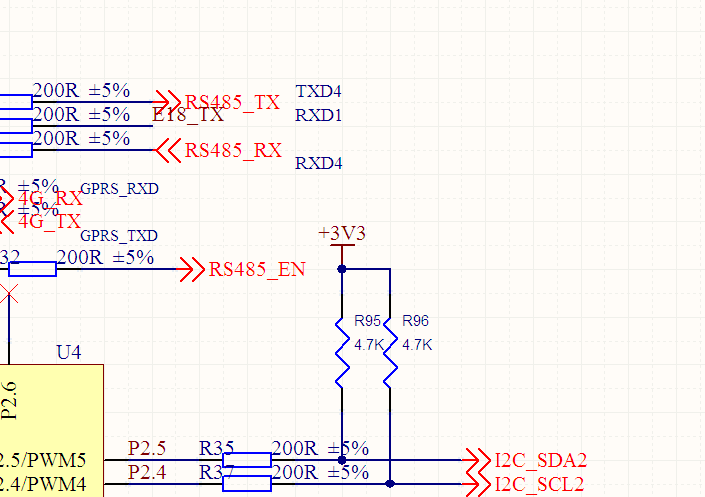

标 准模式, 100Kbps 总线的负载最大容限 《=400pF ;快速模式, 400Kbps 总线的负载最大容限 《=200pF ,根据具体使用情况、 目前的器件制造工艺、PCB的走线距离等因素以及标准的向下兼容性,设计中以快速模式为基础,即总线负载电容《200pF,也就是传输速度可以上到 400Kbps是不成问题的。于是Rpmax可以取的范围是1.8K~7K @ Vio=5V对应50pF~200pF

根据Rpmin与Rpmax的限制范围,一般取5.1K @ Vio=5V , 负载容限的环境要求也容易达到。在2.8V系统中,console设计选3.3K,portable/handset等低供耗的设计选4.7K牺牲速度换取电池使用时间

总的来说:电源电压限制了上拉电阻的最小值 ; 负载电容(总线电容)限制了上拉电阻的最大值。

i2c上拉电阻的作用

做过I2C碰到过各种问题,多半是上拉电阻或者控制器时钟的问题。没上拉电阻或者上拉电阻过大,都会导致不稳定而出现寻址不到的问题。

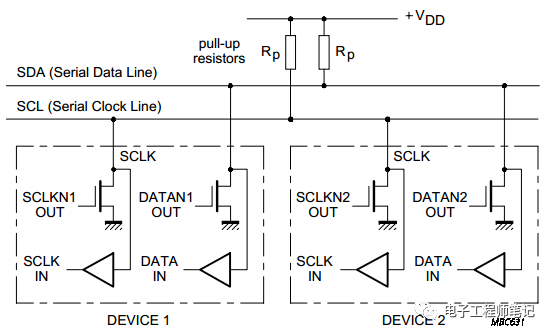

在工业和通讯领域中,上拉电阻在电路系统中常常会具有中断GPIO控制、I2C等信号方面,对于系统稳定性和输出电平的稳定具有无可替代的作用。今天就让我们以手机I2C设计为案例,深入探寻上拉电阻在该系统中的作用,以及I2C上拉电阻最大值都是由哪些因素来决定的。 I2C总线的设计一般都会采用OC或者OD门,如果内部的芯片中没有设置上拉电阻,那么就必须要在外部接一个上拉来保证高电平的输出,从而增加这一系统的稳定性。一般情况下I/O端驱动能力会保持在2mA-4mA左右的量级范围内,而OC或者OD门的导通电压一般为0.4V左右,手机中加在上拉电阻上的电压一般都是2.8V。

在该设定下,I2C上拉电阻的最小值不能低于800R。当电压为5V时,上拉最小值不能低于1.5K。在这种情况下想要中断和GPIO信号本身,是不需要增加多余的驱动设备的,只需要保持一个高电平就可以了。此时,上拉电阻可以选取大一点的阻值以减小功耗,但须注意一个问题,那就是这个阻值不能太大,经验值一般在4.7-100K之间,否则会和PCB走线,器件等负载电容影响信号上升时间。 由于目前大多数的I2C接口都采用了OD机制,所以工程师在实际操作的过程中,需要另外加一个上拉电阻才能维持输出高电平,上拉电阻的最小值须符合之前所提到的要求。 那么,I2C上拉电阻最大值都与哪些因素有关呢? 通常情况下,I2C总线的传输速率分为标准模式和快速模式(在快速模式的情况下,I2C总线传输速率为400Kbit/s),总线负载的最大容限分别是400pF和200pF。根据I2C总线协议的要求,I2C上拉电阻最大值是被总线电容所限制。下图是上拉电阻的取值数据图,图中的Rs指的是I2C设备串联在I2C总线上的电阻,它可以有效的防止SDA和SCL高电压毛刺波产生。

图为上拉电阻取值数据 由上图的曲线走势可以看出,上拉电阻的最小值由上拉电源决定,最大值由总线电容决定。 通过对I2C上拉电阻的实例分析,我们可以看出,上拉电阻在I2C总线中可以起到维持输出电平稳定、保护芯片的作用。而上拉电阻的最大阻值则是由总线的电容所决定的,工程师在进行上拉选取时,需要依据总线电容和上拉电源的电压来判断。

责任编辑:YYX

精彩阅读推荐:

-

上拉电阻

+关注

关注

5文章

366浏览量

31719 -

I2C

+关注

关注

28文章

1562浏览量

131731

发布评论请先 登录

I2C总线一定要接上拉电阻?上拉电阻阻值怎么确定?

在I2C总线上需要接上拉电阻?您对I2C上拉电阻足够了解吗

I2C的开漏输出和上拉电阻

i2c上拉电阻大小_i2c上拉电阻的作用

i2c上拉电阻大小_i2c上拉电阻的作用

评论