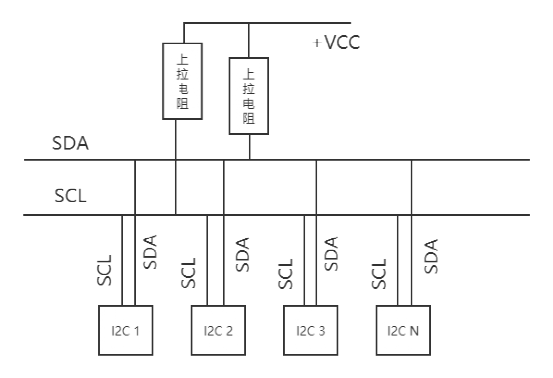

I2C总线是由Philips公司开发的一种简单、双向二线制同步串行总线,它采用同步方式串行接收或发送信息,I2C总线是由串行数据线SDA和串行时钟线SCL组成。因为I2C只有一根数据线,故发送信息和接收信息无法同时进行,I2C工作时的传输速率在标准模式下可达100kbit/s,快速模式下可达400kbit/s,高速模式下可达3.4Mbit/s。I2C总线采用漏极开路的设计,且SDA和SCL通过上拉电阻连接V CC 。今天就和大家来探讨一下I2C为什么需要用开漏输出和上拉电阻。

首先,让我们简单地来回顾一下上周所介绍的推挽输出和开漏输出。

开漏输出:如果输出控制电路接收到低电平(0)时,此时地N-MOS导通,不管有没有接上拉电阻,I/O端口处的电平都会被N-MOS管拉低。但是当输出控制电路接收到高电平(1)时,N-MOS管截止,有上拉电阻存在时,输出高电平,没有上拉电阻存在时,输出电路开路,不能输出高电平。简而言之,开漏输出只有接上上拉电阻时,才有输出高电平的能力。

推挽输出:因为增加了一个P-MOS管,当CPU输出逻辑“1 ”时,P-MOS管导通,输出高电平。当CPU输出逻辑“0 ”时,P-MOS管截止,输出低电平。

为什么I2C需要用开漏输出?

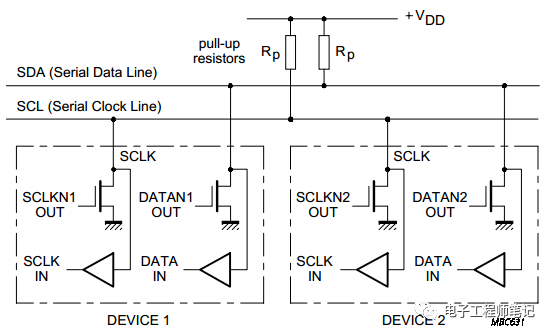

因为I2C协议是支持多个主设备与多个从设备在一条总线上的,此时就会有多个GPIO口连接在同一条总线上,就势必会出现输出高、低电平不统一的情况,如果采用推挽输出时,就可能会出现某个GPIO的Vcc和GND连接在一起造成短路的情况,当你采用开漏输出时,因为有上拉电阻的存在就可以避免这一问题的出现。

为什么要上拉电阻?

①:因为开漏输出不接上拉电阻时无法输出高电平。而I2C通信需要有输出高电平的能力,故在漏极接上上拉电阻

②:I2C总线由SDA(串行数据接线)和SCL(串行时钟线)及上拉电阻组成,这样能够实现“线与”功能,不仅简化了电路,而且依照“线与”逻辑,可以实现多个主设备抢占总线时的仲裁,因为如果一个设备需要启动I2C时,它需要在SCL为高电平时,将SDA由高电平拉低作为启动信号,SDA拉高后,设备会对SDA的电平进行检查,如果此时SDA为低电平,就表示总线已经被占用,如果SDA为高电平,就说明总线可以被占用。

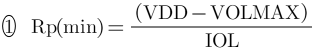

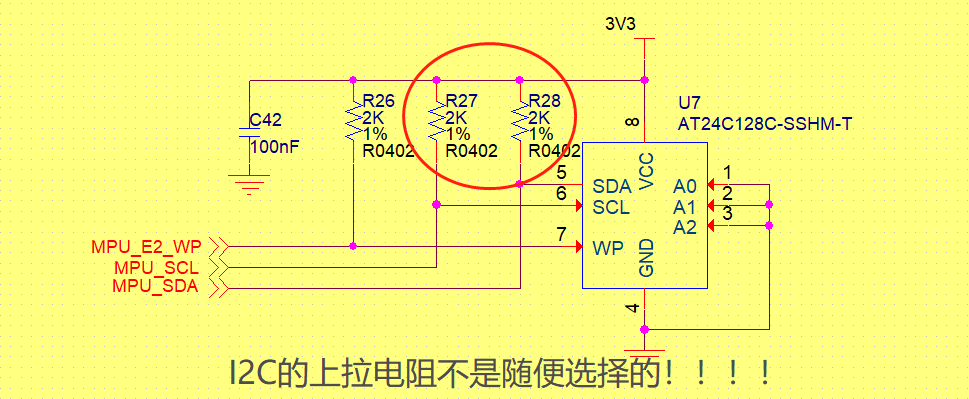

上拉电阻阻值怎么确定?

一般I\\0端口的驱动能力在2mA-4mA量级。

阻值不能过小:

当上拉电阻阻值过小时会导致从VCC输入的电路较大,进而使得MOS管不完全导通(由饱和状态变成放大状态),因为I2C协议规定,端口输出低电平的最高允许值为0.4V,故这样就会使得端口输出的低电平值增大。所以上拉电阻选取时不能低于1KΩ。

阻值不能过大:

因为上拉电阻和总线电容之间形成了RC,如果电阻过大会导致总线拉高的时间拉长以及输出阻抗的增大,当输出阻抗增大到可以与负载阻抗抗衡时,输出的高电平会因为分压而减少。

综上所述,建议上拉电阻选择使用1.5K、2.2K、4.7K。

-

上拉电阻

+关注

关注

5文章

366浏览量

31552 -

总线

+关注

关注

10文章

3014浏览量

91304 -

I2C

+关注

关注

28文章

1547浏览量

130481 -

SDA

+关注

关注

0文章

125浏览量

29397 -

开漏输出

+关注

关注

0文章

77浏览量

7638

发布评论请先 登录

i2c上拉电阻大小_i2c上拉电阻的作用

经过验证的GPIO模拟I2C时序代码

I2C为什么要接上拉电阻?上拉电阻阻值怎么确定?

I2C通讯为什么要用开漏输出和上拉电阻?

I2C的开漏输出和上拉电阻

I2C的开漏输出和上拉电阻

评论