CrowdSupply刚上线一个众筹项目 - 称之为Precursor的便携式、开源RISC-V SoC开发套件,使用了分别来自Xilinx和Lattice的两颗流行的FPGA。

从外观上看,它像极了一个智能手机,它号称,通过编程,你确实可以把它当成一个智能手机或平板电脑使用,且你可以对它有完全的控制,因为你可以编程它的每一个bit,沉到硬件的最底层!

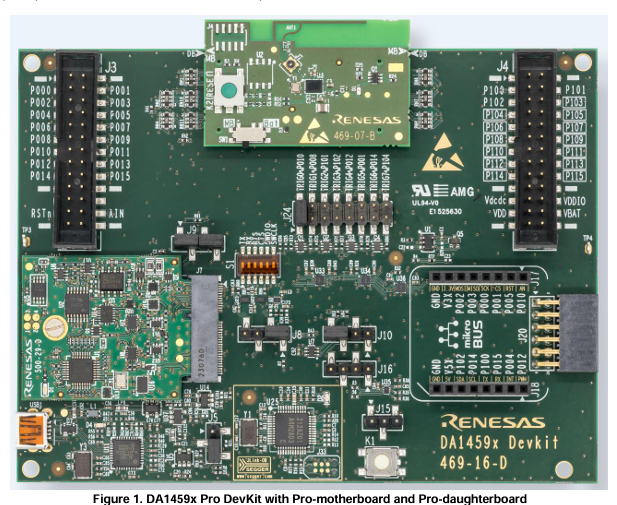

套件的正面照片

背面照片

拆开了由以下一些部分组成:

一块电路板

一个单色的LCD屏

一个键盘

看看键盘的电路板:

内部的结构:

高度安全、完全可信任

从下面的对比图中可以看到其主要的功能:

再跟其它的FPGA开发板比较一下:

价格高是有原因的。

下面是其结构框图:

功能特性:

Made for developers

No adhesives holding the bezels in place – just one screw driver is all it takes

Want to add hardware? Maybe a cellular modem? No problem!

Battery compartment is a blank check for your peripherals

Install a smaller battery for more space

Flex PCB breakout for 8x FPGA GPIO into the battery compartment

Bezel is made out of FR-4, and can be user-customized to hold additional components

Inspect, modify and compile your SoC and embedded controller from source

All source fileshosted on GitHubfor convenient fork, pull request, and issue tracking

Open source PCB and case design

Easy-access developer's cable (included)

Low-level debugging (GDB + Chipscope) and firmware flashing via developer's cable plugged into a custom Raspberry Pi HAT (included)

Middleware debugging via USB cable via wishbone tunnel

Open source to the core

Extendable and modifiable

Slim and light mobile form factor

6063 alloy aluminum case -– 3D files provided, so you can mill your own case!

FR-4 front bezel -– PCB source provided

ABS + PC polymer antenna radome -– 3D printable

69 mm x 138 mm x 7.2 mm

96 grams reference weight

Compare to iPhone X at 70.9 mm x 143.6 mm x 7.7 mm and 174 grams

Accessible mechanical design

User-customizable CPUs

Manages power, standby, and charging functions

Tested with 18 MHz VexRISC-V, RV32I, no cache

-L1 speed grade for longer battery life

Tested with 100 MHz VexRISC-V, RV32IMAC + MMU, 4k L1 I/D cache

Xilinx XC7S50 primary System on Chip (SoC) FPGA

iCE40UP5K secondary Embedded Controller (EC) FPGA

16 MB external SRAM

128 MB Flash

100 MHz DDR 8-bit wide bus for fast XIP code performance

Dual hardware TRNG

External discrete noise generator

In-SoC ring oscillator based TRNG

Inspectable I/O

Physical keyboard with changeable layout overlays

200 ppi black and white LCD (336 x 536 resolution), 100% inspectable with standard optical microscope

Both keyboard and LCD are backlit for night-time use

Modular keyboard PCB -- customize layouts, add sensors, or swap in a touch surface

Audio with safe defaults

Integrated 0.7 W speaker for notifications

Vibration motor

3.5 mm headset jack

No integrated microphone -- audio surveillance is not possible when headset is unplugged

Integrated Wi-Fi

Sandboxed in a hardware-delineated untrusted domain

Silicon Labs WF200C chipset

USB Type-C port

Supports charging at 5 V; over-voltage protection tolerant to 20 V

Power negotiation to 5 V @ 1.5 A (source and sink)

Supports legacy USB 2.0 full-speed PHY

Basic DRP negotiation hardware support

1100 mAh Li-Ion battery

Approx. 100 hours standby with Wi-Fi + embedded controller + static display enabled

Approx. 700 mW "on-state" (most features enabled and active, backlight off) power draw, or 5.5 hours continuous use

Integrated gas gauge for more accurate battery life estimate

Full charge in about three hours

Runtime depends on user application

Anti-tamper features

User-sealable metal can for trusted components

Dedicated real-time clock (RTC) with basic clock integrity monitoring

Power monitors trip reset in case of power glitches

Always-on accelerometer/gyro to detect movement in standby

Support for instant secure erase via battery-backed AES key and self-destruct circuit

责任编辑:xj

原文标题:便携、安全、开源RISC-V SoC开发套件

文章出处:【微信公众号:FPGA入门到精通】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22508浏览量

639495 -

soc

+关注

关注

40文章

4635浏览量

230272 -

Xilinx

+关注

关注

73文章

2208浏览量

131966 -

RISC-V

+关注

关注

49文章

2954浏览量

53598

原文标题:便携、安全、开源RISC-V SoC开发套件

文章出处:【微信号:xiaojiaoyafpga,微信公众号:电子森林】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Banana Pi 开源社区联合进迭时空发布最新RISC-V芯片K3开发套件:BPI-SM10(K3-CoM260)

RISC-V,正式崛起

重磅合作!Quintauris 联手 SiFive,加速 RISC-V 在嵌入式与 AI 领域落地

为什么RISC-V是嵌入式应用的最佳选择

开源鸿蒙RISC-V SIG线下技术融合交流会圆满收官

大湾区RISC-V生态全景展示:RISC-V生态发展论坛、开发者Workshop和生态应用专区

生态合作 | 匠芯创加入RuyiSDK开发者社区 合力推动RISC-V生态持续发展

赛昉科技入驻RuyiSDK开发者社区,双平台协同推进RISC-V生态

普华基础软件亮相2025 RISC-V中国峰会

RISC-V 手册

时擎科技亮相2025 RISC-V中国峰会,深度解析高性能RISC-V SoC技术挑战与创新

跃昉科技正式入驻RuyiSDK开发者社区,助力RISC-V生态建设

DA14594 BLE Pro开发套件 开源 (原理图+BOM+PCB)

CrowdSupply项目:便携式、开源RISC-V SoC开发套件Precursor

CrowdSupply项目:便携式、开源RISC-V SoC开发套件Precursor

评论