高性能控制器设计使用位片组件来提高速度和设计灵活性。常见的是每秒10-20百万条指令(MIPS)的速度,设计人员可以利用位片设计的灵活性在一条指令中执行对速度有严格要求的运算。

位片与RISC架构

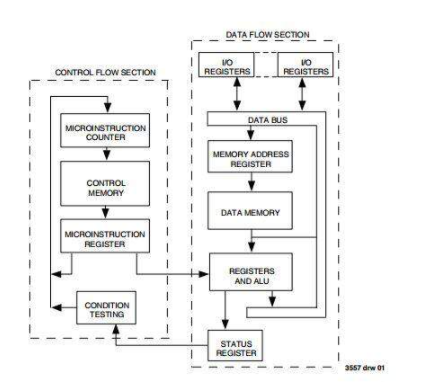

图1中的典型位切片控制器设计示例。它由控制流部分和数据流部分组成。控制流程部分具有微指令计数器和控制存储器。数据流部分。控制流部分具有一个寄存器和ALU元素(位片),以及一个数据总线上的数据存储器和I / O寄存器。注意,控制存储器和数据存储器是分开的。使用单独的数据指令存储器称为哈佛架构。分离的控制存储器提供了与位片设计相关的某些速度,因为它与数据存储器一起工作。这允许从控制存储器中提取下一条微指令,同时可以从数据存储器中读取当前指令的数据。这与常规微处理器相反,常规微处理器交替地从同一存储器中获取指令和数据。将单个存储器用于指令和数据的这种使用称为Non Neumann体系结构。

比较图1和图2,位片控制器的框图与典型的RISC CPU的框图有明显的相似之处。不同之处在于,控制器的控制存储器和数据存储器已被指令高速缓存所取代RISC CPU中的内存和数据高速缓存。指令和数据高速缓存存储器的工作方式与它们的微代码副本相同,不同之处在于它们都在公共主存储器中包含数据的副本。程序员看到的是一个内存-主内存-而硬件则好像有两个独立的内存一样工作。以这种方式,RISC计算机具有哈佛体系结构的速度优势以及用于非诺伊曼体系结构的程序和数据的单个存储器。

位片控制器框图

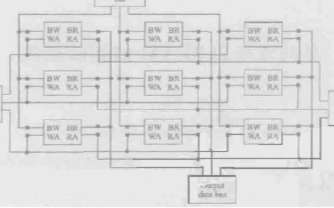

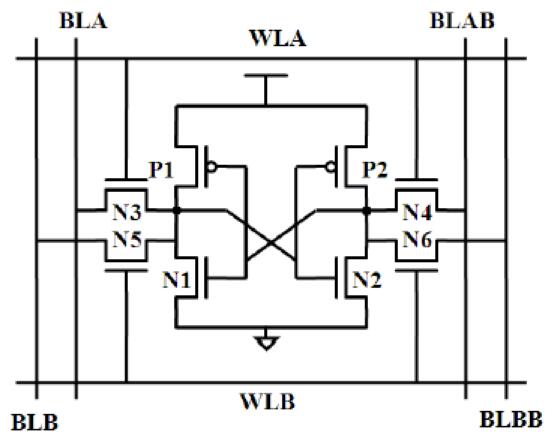

RISC体系结构的指令和数据高速缓存等效于在一个存储器上具有两个端口。通过使用高速双端口内存代替高速缓存,我们可以将此概念应用于位片控制器。双端口SRAM允许指令和数据端口同时且独立地处于活动状态,同时使双方都可以访问一组通用的SRAM单元。由于两个端口都在同一存储器中工作,因此数据流部分可以以与常规微处理器相同的方式加载和移动这两个数据指令。结果,该设计用作常规的交互式软件工具,例如解释器和监视器,以用于系统开发和调试。

RISC CPU框图

编辑:hfy

-

控制器

+关注

关注

114文章

17638浏览量

190228 -

cpu

+关注

关注

68文章

11216浏览量

222921 -

RISC

+关注

关注

6文章

485浏览量

86089

发布评论请先 登录

采用基于字的检测方法对单向双端口SRAM进行测试

多片SRAM的可测试设计怎么优化?

单端口SRAM与双端口SRAM电路结构

SOC中多片嵌入式SRAM的DFT实现方法

双端口SRAM中读干扰问题,读干扰的原理分析

如何对SRAM进行分类

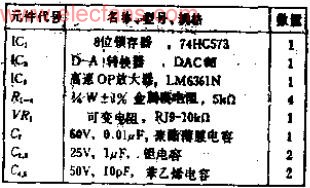

AN-325:12位模拟I/O端口采用AD7549双12位DAC和8051单片机

32位MCU外扩SRAM芯片VTI7064MSME

应用分享| HPM6000系列片上SRAM揭秘

双端口SRAM可产生无微码的位片设计

双端口SRAM可产生无微码的位片设计

评论