在高速电路设计中,元件和元件封装可能影响芯片内以及PCB的信号完整性。实际上,信号完整性包括一组确定信号质量的测量值,作为分析和减轻噪声,失真和损耗影响的一种方法。这是一组设计实践和测试,有两个常见的信号完整性电路设计问题,即信号的时序和质量。信号应按预期到达目的地吗?到达那里后状况?

在高速电路设计项目中,信号完整性(SI)是获得设计成功的必备条件。因此我司会对设计的电路板进行信号完整性分析,以确保产品完整性和无故障高速电路设计。而我们的信号完整性分析如下:

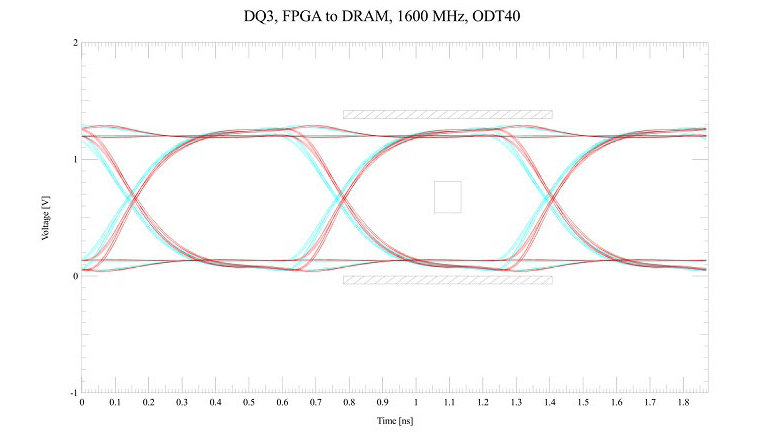

1、布线前后的高速信号完整性分析和仿真

2、28GHz +收发器和40GHz +封装级仿真

3、信号完整性驱动的层堆栈和约束生成

4、针对复杂拓扑的网络调度和设计优化,例如多点总线(DDR3,DDR4)

5、减少反射和串扰,以改善时序裕度和发射

6、优化去耦,实现电源完整性和较低成本

7、同时考虑开关噪声和设计策略

8、组件和系统特性,包括完整的S参数,增益和噪声系数优化

9、针对敏感信号和监管批准的屏蔽设计和分离平面优化

10、比吸收率(SAR)分析

编辑:hfy

-

电路设计

+关注

关注

6732文章

2576浏览量

217968 -

信号完整性

+关注

关注

68文章

1473浏览量

97768 -

高速电路

+关注

关注

8文章

165浏览量

24805

发布评论请先 登录

无故障高速电路设计的信号完整性分析

无故障高速电路设计的信号完整性分析

评论