所谓的Xnet,是指在无源器件的两端,两个不同的网络,但是本质上其实是同一个网络的这种情况。比如一个源端串联电阻或者串容两端的网络。在实际设计情况中,我们需要对这种进行Xnet的设置,方便进行时序等长的设计,一般信号传输要求都是信号的传输总长度达到要求,而不是分段信号等长,这时采用Xnet就可以非常方便的实现这一功能,在allegro软件中添加xnet的具体步骤如下所示:

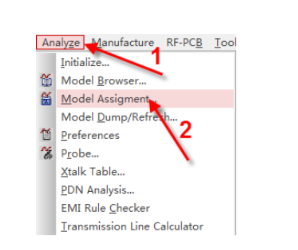

第一步,执行菜单命令Analyze-Model Assigment,进行模型的指定,如图5-112所示;

图5-112 创建模型示意图

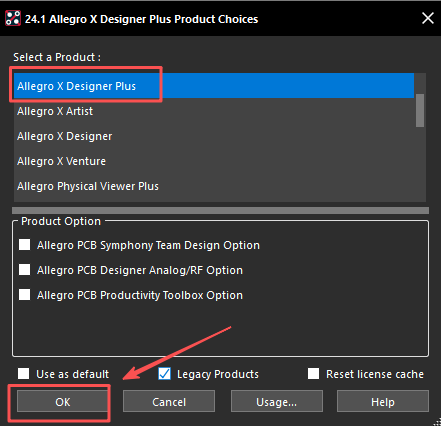

第二步,点击指定模型之后,会弹出如图5-113所示的界面,这些是没有解决的问题,一般都是电压的问题,系统会显示这个是个电源,但是并没有赋予电压值,所以会显示错误。一般我们添加Xnet可以忽略掉这些,不用管这些错误,直接点击OK按钮即可;

图5-113 SI Design Audit示意图

第三步,在PCB界面点击需要设置Xnet模型的元器件,右侧对应列表中会同步进行选中,也可以将同一类型的全部选中,如图5-114所示;

图5-114 给元器件创建模型示意图

第四步,选中需要创建模型的元器件之后,点击如图352-3所示的列表的下方“Create Model”选项,进行模型的创建,在弹出的界面中,按照默认的即可,选择“Create ESpiceDevice model”即可,如图5-115所示;

图5-115 给元器件创建模型示意图

第五步,在弹出的对话框中,如图5-116所示,需要我们自己填写的是:Value值按照实际Value值去填写,仿真的时候会用到这个数据;Single Pins需要我们去对应好电阻的关系,如图5-116输入中的一致,表示的含义是1 8是一个电阻,一个电阻两端的网络是同一个网络,以此类推,这个我们举例添加的排阻有四个Xnet;

图5-116 设置模型参数示意图

第六步,添加完成以后,可以回到PCB界面,点击查询按钮,可以查询该网络,是否添加了Xnet,如图5-117所示。

图5-117 Xnet显示示意图

上述,就是在Allegro软件中添加Xnet的方法解析,一般多用于带有串阻串容的时序等长中。

编辑:hfy

-

pcb

+关注

关注

4391文章

23744浏览量

420780 -

allegro

+关注

关注

42文章

755浏览量

149490 -

无源器件

+关注

关注

5文章

225浏览量

24245

发布评论请先 登录

技术资讯 I 在 Allegro PCB 中如何快速布局

如何将“同步scons 配置至项目”功能添加到编译步骤中?

技术资讯 I Allegro PCB设计中的扇出孔操作

技术资讯 I Allegro PCB 设计中布线优化

PCB抄板全流程解析:从拆解到测试,技术要点全揭秘!

Allegro更新原理图导入网表后,Xnet混乱何解?

Allegro Skill字符功能之补齐REF字符

借助Cadence工具简化PCB设计流程

解锁未来汽车电子技术:软件定义车辆与区域架构深度解析

Allegro Skill封装功能之添加禁布区介绍

PCB技术:allegro软件中添加xnet的步骤解析

PCB技术:allegro软件中添加xnet的步骤解析

评论