1、介绍

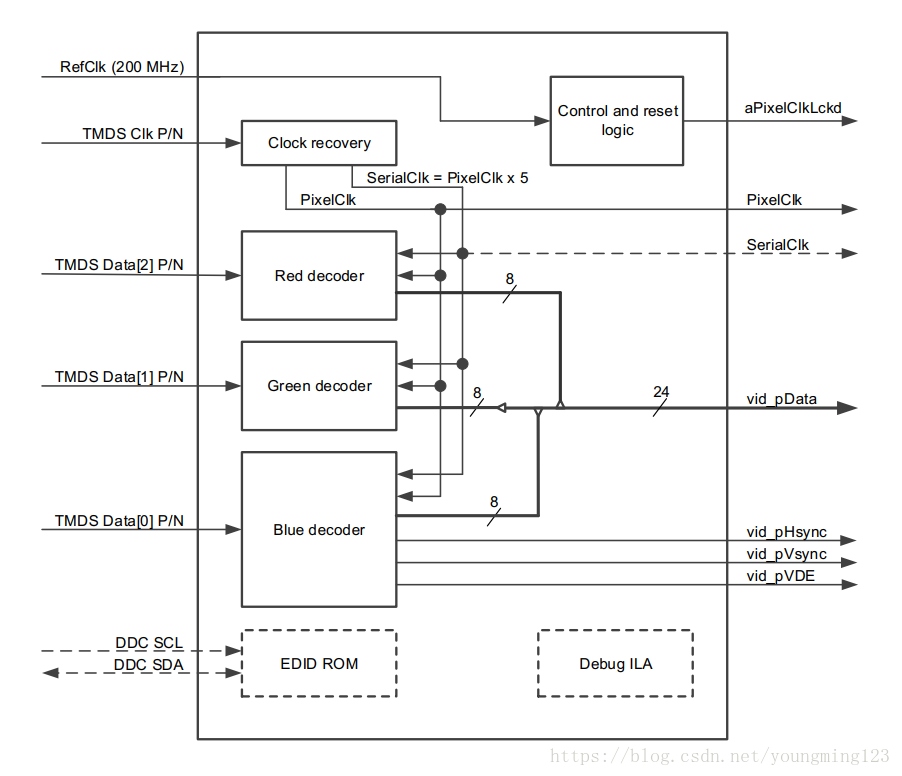

本用户指南介绍了Digilent DVI-to-RGB视频解码器知识产权。 该IP直接连接到Sink器件的DVI 1.0规范中定义的原始转换最小化差分信号(TMDS)时钟和数据通道输入。 它解码视频流并输出24位RGB视频数据以及从TMDS链路恢复的像素时钟和同步信号。

2、特性

•直接连接到顶级数字视频接口(DVI)端口

•24位视频(带同步信号的时钟并行视频数据)输出

•带有内置EDID ROM的显示数据通道接口

•支持的分辨率:1920x1080 / 60Hz至800x600 / 60Hz(148.5 MHz - 40 MHz)

•EDID中可选的首选分辨率

•使用Xilinx接口:IIC,vid_io

•使用Digilent接口:TMDS

3、性能

IP将TMDS_Clk限制在165 MHz,这是DVI 1.0规范中列出的最大频率。 但是,根据实际的FPGA部件或速度等级,最大支持频率可能较低。 如果顶层设计在IP实例内的脉冲宽度检查上没有约束,TMDS_Clk需要(重新)限制到项目部分支持的最大频率。 检查FMAX_BUFIO部分的数据表,这是定时失败的最可能原因。 TMDS_Clk应该限制在FMAX_BUFIO / 5。 因此,这是FPGA系列和速度等级支持的最大像素时钟频率。

4、 概览

IP由多个模块构成:一个时钟恢复模块,每个数据通道一个数据解码器模块(参见[3],[4]),一个可选的DDC(显示数据通道)模块和一个控制/复位模块。

4.1、时钟复位

时钟通道载有一个字符速率频率参考。 一个字符(或10比特)在每个数据信道的每个周期传输。 专用解串器原语(需要快速串行时钟)将用于对串行数据流进行采样。 时钟恢复模块从时钟通道产生一个串行时钟和一个像素时钟。 两个时钟之间的频率比是5:1。

由于时钟频率相对较高并且恢复的时钟具有严格的相位要求,因此在该块内部实例化专用时钟基元。 这些可以在图2中看到。MMCM原始设备包含一个压控振荡器(VCO),其具有FPGA数据手册中指定的工作范围。 由于没有一组MMCM参数可将整个DVI像素时钟频率范围映射到VCO范围,因此可以使用IP定制参数来优化预期的分辨率和像素时钟频率。

4.2、数据解码

恢复的像素时钟或串行时钟与数据通道之间不存在相位关系。 此外,数据通道本身在它们之间允许相当大的偏差。 所以解码器块需要将串行时钟的相位与数据位对齐,并在每个数据流中找到字符边界。 由于这必须在三个数据通道中的每一个上独立完成,因此在保持时钟相位固定的同时改变数据流的相位是有意义的。

4.2.1、同步

为了帮助同步,DVI协议规定了要发送的周期线索(控制令牌)。这些控制令牌与数据的其余部分充分不同,它们的继承可用于同步。当检测到并恢复稳定的时钟时,同步会自动(重新)开始。锁定所需的时间取决于时钟和数据流的相位关系。它不应该持续超过1分钟。

DVI字符的长度为10位,因此需要对数据流进行10:1的反序列化。这可以通过级联DDR配置中的两个ISERDESE2原语来实现。在这种配置中,主机和从机ISERDESE2接收串行数据流并在串行时钟的两个边沿对其进行采样。因此,对于每五个串行时钟周期,十个数据位被采样。这个10位数据然后与一个分频时钟同步输出,这是我们来自时钟恢复模块的像素时钟。虽然这可以从数据流中恢复10位字,并且频率可以传递给FPGA内部的通用逻辑,但确实保证字实际上始于字符边界,或者数据稳定时采样数据流。

为了找到采样数据流的最佳时刻(即,睁眼的中间),在ISERDESE2之前插入IDELAYE2基元。该原语能够以分接增量来延迟数据信号。在这个IP中,一个78ps的增量用于总共32个增量。对于支持的最高像素时钟频率(165 MHz),以7个抽头增量覆盖一个位周期。目标是找到抽头延迟值,将数据移动到足够的位置,以便在稳定区域的中间进行采样。相位对齐模块将10位字与四个特殊控制令牌进行比较。如果在超时时段内未识别出连续的令牌,则我们处于抖动区域,并且会增加抽头延迟。这一直重复进行,直到控制令牌被可靠地识别并且算法稳定在稳定位周期(开放眼睛)的中间。一个“开放的眼睛”是由一系列最小数量的抽头值(3)定义的,其中控制令牌可以被可靠地检测到,并且它在两端由一个抽头值定界,但不能。但是,使用此定义将会漏掉开始或结束于分接延迟范围(0或31)末端的睁眼,因为不会找到两个抖动分隔符。所以即使睁开的眼睛在四肢开始或结束,如果它足够长(16次增量),它将被视为有效的眼睛。但是,IDELAYE2原语仅在位级别上提供了精细的相位调整,而不是覆盖整个字符。为了找到字符边界,需要粗略的相位调整。这是通过ISERDESE2原语的“bitslip”功能实现的。如果所有的分接增量都已经尝试过,并且控制标记还没有被检测到,那么就认为我们不在正确的字符边界。在这种情况下,调用“bitslip”会导致在10位字中右移一位或在hree中左移一位。 “bitslip”完成后,相位对齐再次开始,循环通过抽头增量。直到找到令牌。当在所有数据通道上可靠地检测到连续的控制令牌时,认为相位对齐完成。此时所有三个数据通道都被认为是有效的。

然而,由于对间信道时滞不可忽略且信道独立对齐,所恢复的数据流可能具有不同的延迟。为了消除这种偏差,通道通过在FIFO存储器中缓冲并独立保持它们直到视频消隐周期同时在所有三个时间同时开始而被结合。在这个阶段,所有三个数据通道都是有效的并且是同步的。

4.2.2、 解码

TMDS标准对数据进行编码,以便串行数据流包含很少的转换(0到1或1到0)和一个DC平衡(长时间内相同数量的零和1)。 每个10位字符实际上封装了8位有用数据。 这个例外是控制令牌,它封装了2位控制数据。 数据解码器模块应用DVI 1.0规范中规定的解码算法。 在解码之后,我们在消隐期间留下控制数据或者在有效期内保留像素数据。 由于每个数据通道携带一种颜色,因此从IP输出一个24位RGB像素总线。

4.3、 EDID ROM(数据显示通道)

DDC模块模拟包含缺省Digilent品牌扩展显示标识数据(EDID)的只读存储器。 有四种变体只在首选分辨率上有所不同。 该参数是用户可在IP自定义向导中选择的。 EDID在与IP捆绑在一起的src / *。data文件中定义(参见第6.4节)。 合成后,对应于首选分辨率的文件将被纳入网表。 允许修改这些文件,只要它与DDC规范兼容即可。

5、端口描述

表1列出了DVI至VGA内核的信号。

6、 围绕IP核设计

6.1、 约束

TMDS时钟输入Clk_p / n被限制在最大DVI时钟频率165 MHz的IP中。 在某些体系结构中,这可能导致无法实现。 根据应用的不同,如果较低的像素时钟频率可以接受,则时钟可以被限制在顶层,这将覆盖IP内部约束。

例如,要限制720p分辨率(74.25 MHz)的设计,计算de clock period(13.468ns),并将以下内容添加到项目XDC文件中,以约束顶层输入端口上的时钟:

create_clock -period 13.468 -waveform {0.000 5.000} [get_ports hdmi_rx_clk_p]

6.2、 定制

IP提供以下可自定义的参数:复位信号的极性,PixelClk时钟缓冲器类型,TMDS时钟的频率范围,调试逻辑的实例化,要在捆绑的EDID中声明的首选分辨率,DDC通道的可用性,和串行时钟输出。启用DDC通道和串行时钟将会将相应端口添加到IP中,并可用于用户逻辑。并行像素时钟(PixelClk)通过使用BUFR缓冲器进行恢复。由于BUFR仅限于一个时钟区域,并且从内核输出的视频数据与PixelClk同步,因此任何下游消耗视频数据的逻辑也都受限于此时钟区域。重新缓冲PixelClk的选项在BUFR之后引入BUFG,并将视频数据重新注册到BUFG域。这将允许下游逻辑放置在设备的任何位置。通过设置预期的TMDS时钟频率,IP可以实例化符合时钟恢复逻辑中时序要求的FPGA原语。如果从流中恢复的实际像素时钟落在此处设置的范围之外,FPGA的VCO工作范围可能不受尊重,并且在极端情况下,时钟恢复可能会失败,并且视频流将无法正确解码。

如果启用了DDC通道,则可以设置首选分辨率。 此处设置的分辨率将为模拟的EDID ROM选择正确的初始化文件。 这个EDID将被连接的数据源读出,并可能选择以这个分辨率传输。

调试模块可以通过启用向导中的选项来实例化。 启用它将导致合成两个ILA内核,这些内核可用于Vivado硬件管理器来分析一些帮助调试的内部状态信号。

6.3、SerialClk的使用

虽然快速串行时钟通常仅用于内部反序列化,但在其他有限的情况下它可用并且有用。 这个限制源于这样一个事实,即该时钟的频率通常太大(PixelClk频率的五倍),无法为用户逻辑提供时钟。 例如,1080p将导致742.5 MHz SerialClk。 BUFIO原语驱动这个时钟网络以适应大的频率,这只能在相同的存储区/时钟区域为I / O列提供时钟。 一种情况是使用此时钟驱动Digilent RGB2DVI内核,共享两个内核之间的时钟逻辑。

6.4、 EDID捆绑

IP带有几个EDID文件,每个EDID文件声明不同的首选/原生分辨率。 名为* .data的文件包含Vivado合成可读格式的256个字节的EDID数据。 每行只有一个二进制格式的字节。 字节0是文件中的第一个字节。 下表总结了人类可读格式的EDID。 您也可以在您可以在EDID编辑器工具中打开的docs /目录中找到* .dat文件。

7、 调试

当启用调试模块时,将添加两个ILA内核,每个时钟域一个:RefClk和PixelClk。 即使TMDS接口上没有接收到时钟,RefClk域也包含活动的控制逻辑。 与重置和时钟恢复有关的信号与该ILA相关联。

编辑:hfy

-

FPGA

+关注

关注

1655文章

22283浏览量

630145 -

压控振荡器

+关注

关注

10文章

174浏览量

30365 -

DDC

+关注

关注

2文章

99浏览量

38104 -

视频解码器

+关注

关注

0文章

83浏览量

20252 -

差分信号

+关注

关注

4文章

405浏览量

28871

发布评论请先 登录

增强T-BOX设计,新唐编解码器的重要作用

0.1-2.7 GHz SP4T 开关,带集成逻辑解码器 skyworksinc

0.25 - 2.15 GHz 4x2 开关矩阵,带音调/电压解码器 skyworksinc

4 x 2 开关矩阵,带音调/电压解码器 250 MHz–2.15 GHz skyworksinc

OT82111_VC1:USB OTG音频解码器固件技术解析

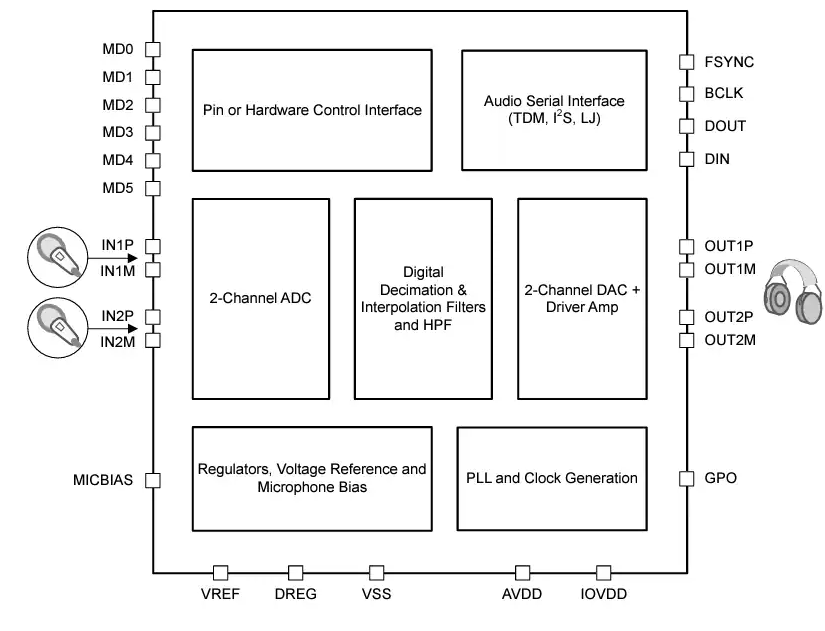

Texas Instruments TAC5x42接口编解码器数据手册

芯原发布高效的VC9000D_LCEVC视频解码器,支持8K超高清

HT1002D 16路视频解码器规格书

EE-203:通过异步端口将ADSP-BF535/ADSP-BF533 Blackfin处理器与NTSC/PAL视频解码器连接

一文解读Digilent DVI-to-RGB视频解码器

一文解读Digilent DVI-to-RGB视频解码器

评论