本片主要介绍PCIe总线的电源管理,主要包括不同板卡的功耗、板卡的能耗等级等。

1、功耗等级

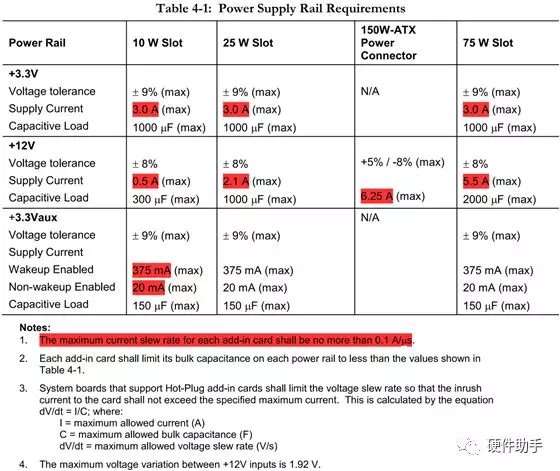

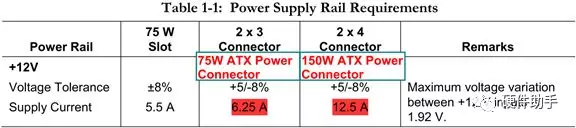

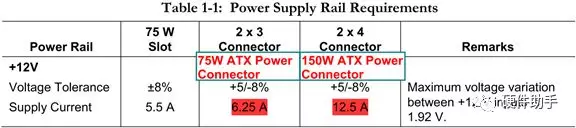

根据《PCIx系列之“PCIe总线信号介绍”》,PCIe接口的电源包括+12V、+3.3V、+3.3Vaux三种。根据功耗的不同,三种电压的供电能力不同,PCIe卡可以分为以下几种:

- 10W,直接通过金手指提供;

- 25W,直接通过金手指提供;

- 75W,直接通过金手指提供;

- 150W,需同时通过金手指和2×3Connector提供;

- 225W,需同时通过金手指和2×4Connector提供;

- 300W,需同时通过金手指和2×3Connector和2×4 Connector提供;

3、电源管理

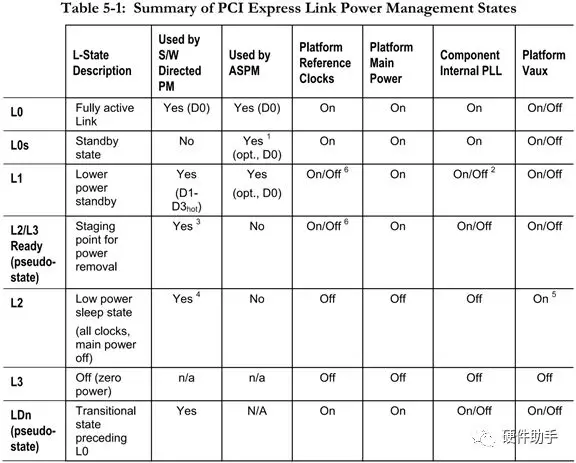

PCIe卡和RC建立连接后,Link power management states有如下几种:

- L0 – Active state. 是工作状态,所有的PCIe操作都可以进行。

- L0s – A low resume latency, energy saving “standby” state. 是节能的待机状态,但是能很快恢复到工作状态。

- L1 – Higher latency, lower power “standby” state. 是低能耗的待机状态,需要比L0s更多的时间恢复到工作状态。

- L2/L3 Ready – Staging point for L2 or L3.

- L2 – Auxiliary-powered Link, deep-energy-saving state. 使用辅助供电,深度节能状态,实现上面属于可选的状态。

- L3 – Link Off state. 是完全关闭的状态。

- LDn – A transitional Link Down pseudo-state prior to L0.

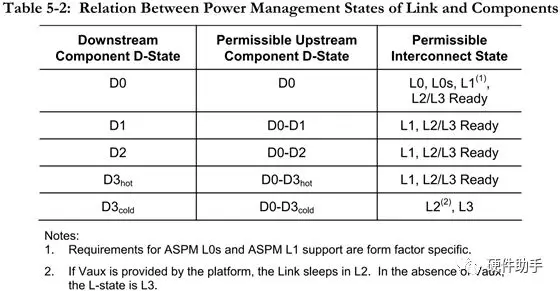

Device Power Management States有如下几种:

- D0 State

D0 uninitialized state

D0 active state

- D1 State

- D2 State

- D3 State

D3 hot state

D3 cold state

每一种尺寸的卡,在上电时其默认最大功耗是有限制的,可以通过软件配置更高的功率。每种尺寸的卡的默认功率为:

- A x1 standard height, half-length card is limited to a 10 W maximum power dissipation.

- A x1 low profile card is limited to a 10 W maximum power dissipation.

- A x1 standard height, full-length card is limited to a 10 W maximum power dissipation at initial power up. When the card is configured for high power, by default, it must not exceed a 25 W maximum power dissipation oroptionally it must not exceed a 75 W maximum power dissipation.

- A x4/x8 or a x16 standard height or low profile card is limited to a25 W maximum power dissipation at initial power up. When a card is configured for high power, it must not exceed a 75 W maximum power dissipation.

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PCIE总线

+关注

关注

0文章

58浏览量

14048 -

PCIe卡

+关注

关注

0文章

12浏览量

7715

发布评论请先 登录

相关推荐

热点推荐

小尺寸车规贴片电容 车载 ADAS 模块电源去耦

尺寸车规贴片电容在车载ADAS模块电源去耦中的应用,以下从核心参数、选型要点、典型应用场景及推荐方案四个方面展开分析: 一、核心参数:小尺寸与车规级性能的平衡 封装尺寸与

【「高速数字设计(基础篇)」阅读体验】第六章 去耦电容的容量需求分析

不同设计场景

倍乘系数法:适合负载电容明确的简单电路,快速出结果;

功耗电容法:解决复杂IC负载电容难测的问题,通过功耗反推更具实操性;

电压波动约束法:从电源噪声指标倒推,精准度高。

发表于 11-19 20:48

【「高速数字设计(基础篇)」阅读体验】第五章 去耦电容

最近在啃《高速数字设计》,第五章“去耦电容:远交近攻”把高速电路里电源噪声的问题讲透了,对于做硬件设计的同学来说,这章简直是“电源完整性”的

发表于 11-19 20:35

如何从电容值去区分电容的类型及使用范围

- 1000nF)

立刻想到:去耦、信号处理。

首选类型:MLCC (X7R, X5R材质)、薄膜电容。

应用:

100nF (0.1µF):经典的IC电源

发表于 11-13 15:20

【「高速数字设计(基础篇)」阅读体验】+第五章去耦电容阅读体验

去耦电容是PCB设计中用于稳定电源电压、滤除高频噪声的关键元件,其作用与布局要求直接影响电路性能。以下是核心要点总结:

一、去

发表于 11-06 17:01

NVMe高速传输之摆脱XDMA设计之12:PCIe请求模块设计(上)

请求模块的具体任务是将系统的请求转换成为axis接口形式的TLP或配置管理接口信号。这些请求主要包含初始化配置请求和门铃写请求,初始化配置请求由初始化模块发起,当配置请求的总线号为0时,请求通过

发表于 08-03 22:00

PCB设计如何用电源去耦电容改善高速信号质量

,高速先生则默默的看向本文的标题:如何用电源去耦电容改善高速信号质量?

没错,高速先生做过类似的案例。

如前所述,我们的Layout攻城狮经验丰富,在他的努力下,找到了另外一个对比模型

发表于 05-19 14:28

nvme IP开发之PCIe下

配置空间 管理PCIe总线。PCI配置空间头分为Type0和Type1两种类型,Type0类型配置空间 头在PCIe总线中用于EP,Type

发表于 05-18 00:48

nvme IP开发之PCIe上

体系架构

RC是PCIe体系树形结构中的根节点。RC主要负责配置PCIe总线上的所有设备,分配资源、处理传输请求,并管理数据流动。在处理器系统中,RC是负责连接CPU与

发表于 05-17 14:54

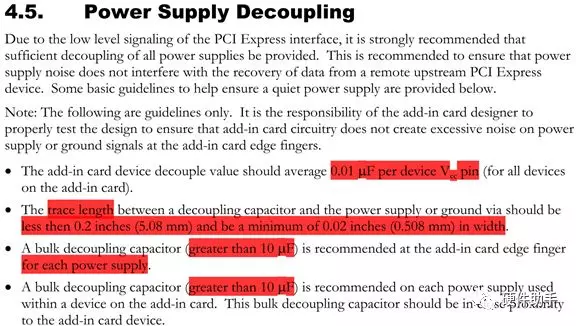

PCIe总线的电源管理之去耦电容

PCIe总线的电源管理之去耦电容

评论