今天,我们聊聊双核通信。双核通信的基础是已经建立好了双核工程,且配置完成。两个CPU之间传递数据,采用了共享内存,共享内存设置在OCM(On Chip Memory)内。

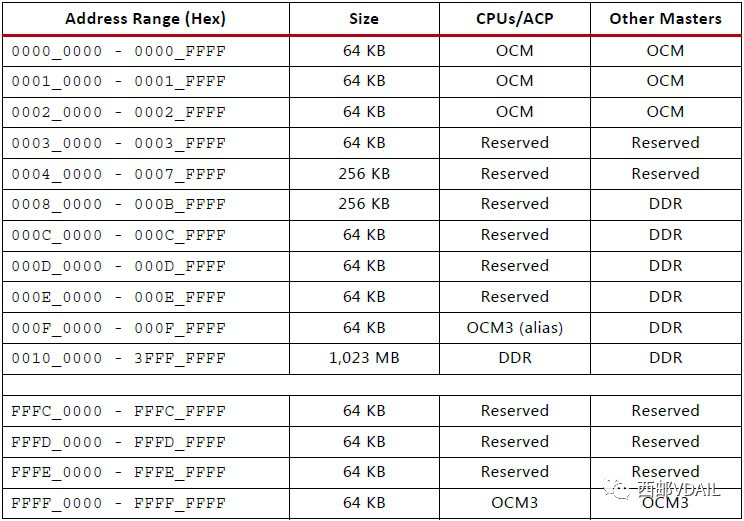

在没有做其他设置的情况下,ZYNQ上电后地址空间分别如下图所示:

OCM共256KB按照64KB分为4块,其中前三块在SDK中表述为RAM0占192KB处于地址空间的最开头和DDR共用地址空间,最后一块64KB处于地址空间的最后。ZYNQ的DDR固定占地址空间的最开头1GB字节因而ZYNQ的DDR最大容量就只有1GB。

为了避开OCM从上图可知实际使用的DDR只有1023MB(最开头的1MB被保留避开OCM的前三块)。从0x40000000到0xDFFFFFFF的2GB空间留给了自定义IP或者其他IP的寄存器,从BSP的xparameters.h可以看出在PL部分添加的IP其基址都是从0x40000000开始的,而ZYNQ自己的寄存器则从0xE0000000开始编制,具体寄存器内容请查阅UG585的附录B Register Details。

其实Standalone作为基础的BSP所作的工作都是在通过指针访问各个寄存器而已,在不考虑安全性的前提下可以完全不用BSP直接操作寄存器对ZYNQ进行操作。

需要在SDK中进行双核通信的设置,主要是程序的设置。

1、CPU1需要被CPU0启动

CPU0的配置

设置共享内存区域:

#define Send_CPU1_Status (*(volatile unsigned int *)(0xFFFF0000))

在主函数中添加:

Xil_SetTlbAttributes(0xFFFF0000,0x14de2);// CPU0中禁止OCM的Cache属性

2、CPU1通信配置

CPU1的配置

设置共享内存区域:

#define Send_CPU1_Status (*(volatile unsigned int *)(0xFFFF0000))

在主函数中添加:

Xil_SetTlbAttributes(0xFFFF0000,0x14de2);// CPU0中禁止OCM的Cache属性

3. 设置完成

双核之间通过对该内存区域进行读写操作完成通信功能。

编辑:hfy

-

cpu

+关注

关注

68文章

11332浏览量

225975 -

Zynq

+关注

关注

10文章

633浏览量

49588

发布评论请先 登录

双展同启·“芯”品首发|度亘核芯重磅新品亮相上海光博会 美国OFC!

探索SGM48759双路双边模拟开关:特性、应用与设计要点

双编码器:解锁未来科技的“双核密码”

XC7Z020-2CLG484I 双核异构架构 全能型 SoC

如何在rt-thread studio上开发STM32H747这类双核的单片机?

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 异构架构下的智能边缘计算标杆

单核CPU网关和双核CPU网关有什么区别

鸿雁电器携手智芯科推出离线双核语音控制单火线开关

Analog Devices Inc. ADSP-SC592 SHARC+®双核DSP数据手册

ZYNQ学习要点:双核通信

ZYNQ学习要点:双核通信

评论