3月11日,自适应和智能计算的全球领先企业赛灵思公司(Xilinx, Inc.,(NASDAQ: XLNX))今天宣布推出Versal ACAP产品组合第三大产品系列—— Versal™ Premium。 Versal Premium 系列具备高度集成且功耗优化的网络硬核,是业界带宽最高、计算密度最高的自适应平台。Versal Premium 专为在散热条件和空间受限的环境下运行最高带宽网络,以及需要可扩展、灵活应变应用加速的云提供商而设计。

Versal 是业界首款自适应计算加速平台( ACAP ),是一个功能远超常规芯片架构的革命性全新异构计算器件类别。全新Versal Premium 采用台积电( TSMC ) 7nm 工艺制程打造而成,融软件可编程能力与动态可配置硬件加速、预制连接和安全功能为一体,为加快产品上市进程提供了强大引擎。作为Versal ACAP 的最新产品系列, Versal Premium 系列可提供比当前FPGA高达三倍的吞吐量,且内置以太网、Interlaken 和加密引擎以打造快速、安全的网络。该系列提供了当前部署主流 FPGA 两倍的计算密度,同时还面向持续扩展的多元化且不断演进的云工作负载及网络工作负载,提供了灵活应变的能力。

赛灵思产品和平台营销副总裁 Kirk Saban 表示:“Versal Premium 系列将 ACAP 推向了一个新高度,通过网络硬核 IP 的突破性集成,成就了单芯片 400G 和 800G 的解决方案。面向下一代网络和云部署,Versal Premium 在软件和硬件开发者皆可轻松编程的可扩展平台上,提供了出色的带宽和计算密度,实现了加速功能的优化并大幅降低了总拥有成本。”

Versal Premium 系列基于当前正在供货的 Versal AI Core 与 Versal Prime ACAP 系列而打造。Versal Premium 的新颖和独到之处在于 112Gbps PAM4 收发器、数百 GbE (千兆位以太网)和 Interlaken 连接、高速加密以及内置 DMA、同时支持CCIX 和 CXL 支持的 PCIe® Gen5。配合 Vitis™ 统一软件平台与 Vivado® 设计套件,Versal Premium 可为软件与硬件开发者提供完整的解决方案堆栈,助力实现最高生产力。

更快速、更安全的网络

随着 5G 网络投入运营,网络流量大幅增长,导致现有空间和功耗范围内功耗优化吞吐量与计算密度的需求不断提高。为支持业界应对这一挑战,Versal Premium 系列提供了高达 9Tb/s 的可扩展、自适应串行带宽。具体方法是将 112G PAM4 收发器与集成的网络功能模块用于核心网、城域网和数据中心互联( DCI )基础设施,将每端口带宽密度提高两倍,并降低时延高达 50%。

这种预制连接可实现安全的多太位以太网(multi-terabit Ethernet),灵活支持各种数据速率与协议。通道化以太网硬核能够以最小占板空间提供高达 5Tb/s 的吞吐量,同时高速加密引擎可提供高达 1.6Tb/s 的加密线路速率吞吐量,并支持 AES-GCM-256/128、MACsec 和 IPsec 。

TIRIAS Research 首席分析师 Jim McGregor 表示:“随着对核心网需求的持续增长,对灵活应变基础架构硬件的需求也相应地大大增加。全新 Versal Premium ACAP 基于赛灵思面向通信网络的业界验证的高性能和自适应产品组合而打造。通过集成功耗优化的网络硬核,其将为电信运营商构建快速且安全的网络提供强大动力,而针对那些正驱动网络和数据中心转型的新型数据密集工作负载,Versal Premium 也将提供灵活应变的加速功能。”

灵活应变的云加速

Versal Premium 系列旨在帮助超大规模数据中心用户为多元化的数据中心工作负载实现最高加速水平。将超过 120TB/s 的片上存储器带宽与可定制存储器层级相结合,能够减少数据移动从而消除相应的关键瓶颈,与此同时,还支持以嵌入式方式将预制连接与硬核集成到现有云基础设施中。从基因组学、数据分析和视频转码,到针对语音和图像识别的 AI 推断,Versal Premium 提供了高度集成的云就绪平台,为多元化的工作负载提供突破性能。

责任编辑:gt

-

FPGA

+关注

关注

1664文章

22504浏览量

639296 -

台积电

+关注

关注

44文章

5811浏览量

177055 -

赛灵思

+关注

关注

33文章

1798浏览量

133663

发布评论请先 登录

基本半导体推出第三代碳化硅MOSFET顶部散热封装系列产品

易灵思2026技术研讨会圆满举办,16nm 钛金系列重塑FPGA效能边界

AD7739:高精度、高吞吐量模拟前端ADC的深度解析

赛灵思FPGA电源解决方案全解析

欧洲快递行业巨头部署全新Matrix 830/930系统以应对高吞吐量业务

罗德与施瓦茨携手瑞昱展示蓝牙低功耗高数据吞吐量测试解决方案

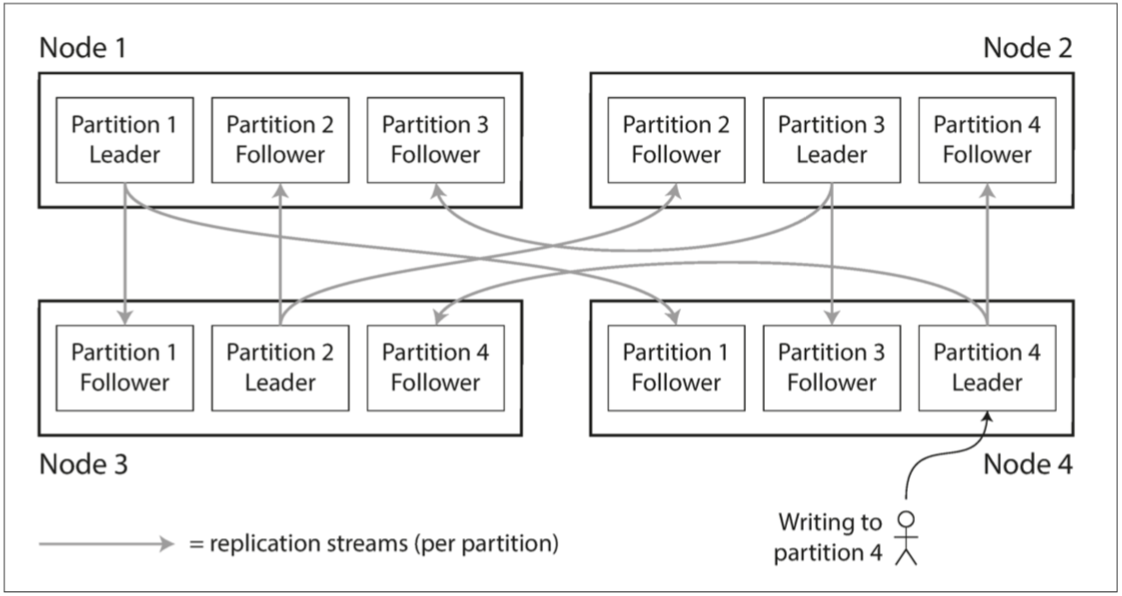

用“分区”来面对超大数据集和超大吞吐量

NVIDIA 推出 Nemotron 3 系列开放模型

使用罗德与施瓦茨CMX500的吞吐量应用层测试方案

赛灵思推出Versal ACAP第三大产品系列,吞吐量比当前FPGA高达三倍

赛灵思推出Versal ACAP第三大产品系列,吞吐量比当前FPGA高达三倍

评论