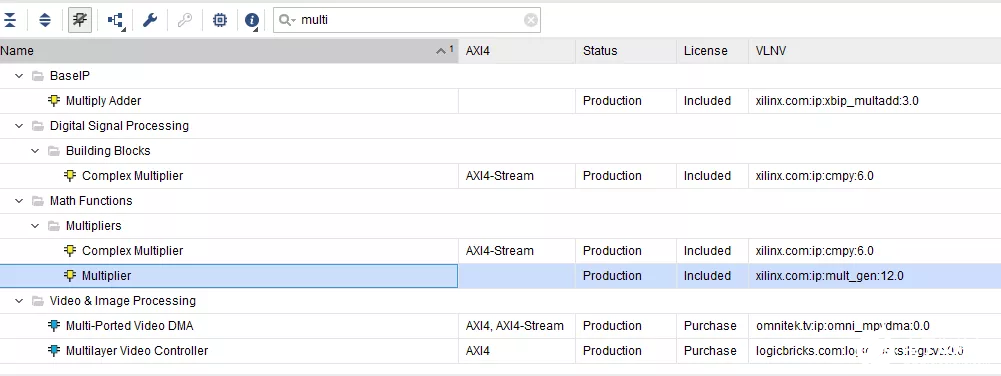

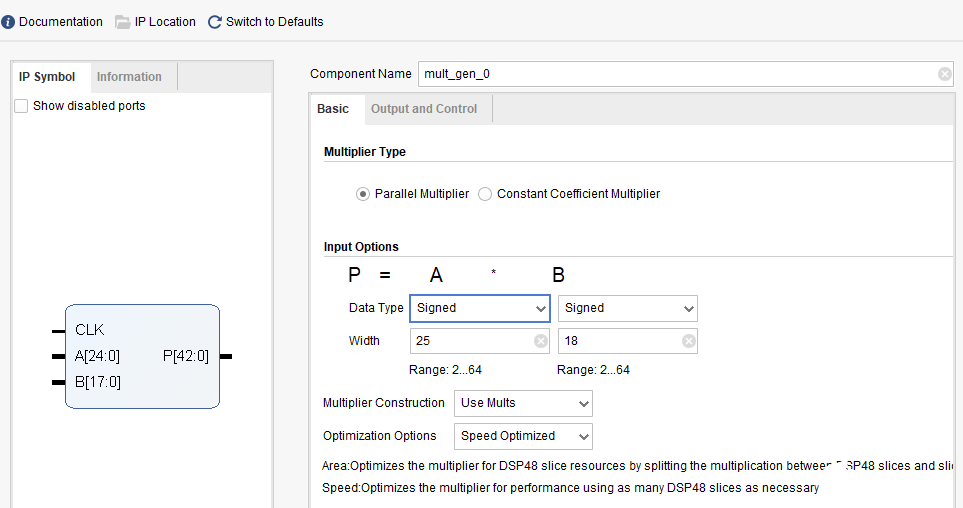

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。

当然,我们也可以直接使用*符合来进行乘法,对于无符号的乘法

reg [7:0] ubyte_a; reg [7:0] ubyte_b; (* use_dsp48="yes" *) output reg[15:0] u_res; always @ ( posedge clk ) begin if(rst) u_res <= 'b0; else u_res <= ubyte_a * ubyte_b; end

有符号乘法可以在Verilog中使用signed来标注。

reg signed [7:0] byte_a;

reg signed [7:0] byte_b;

(* use_dsp48="yes" *)

reg signed [15:0] res;

always @ ( posedge clk ) begin

if(rst)

res <= 'b0;

else

res <= byte_a * byte_b;

end

当然我们也要理解有符号数乘法的原理,其实就是扩位乘法,把高位都补充为符号位。

有符号数乘法:

reg [7:0] ubyte_a;

reg [7:0] ubyte_b;

(* use_dsp48="yes" *)

reg [15:0] res_manul;

always @ ( posedge clk ) begin

if(rst)

res_manul <= 'b0;

else

res_manul <= {{8{byte_a[7]}},ubyte_a} * {{8{ubyte_b[7]}},ubyte_b};

end

关于乘法输出的位宽,我们知道,两个8bits的无符号数乘法,结果的位宽是16bits,但对于两个8bits有符号数的乘法,只要两个数不同时为-128,即二进制0b1000_0000,那么输出结果的高两位都是符号位,我们只需要取低15bits即可。因此,如果我们可以保证两个输入的乘数不会同时为有符号数所能表示的负数最小值,那么乘法结果的高两位都是符号位,只取其中一位即可。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

561文章

8276浏览量

368301 -

FPGA

+关注

关注

1664文章

22504浏览量

639316

发布评论请先 登录

相关推荐

热点推荐

位操作的常见错误与应对策略

的,可能会导致数据溢出或丢失。

(三)数据类型位表示的理解要点

在嵌入式系统中,不同的数据类型有着不同的位表示方式,这一点在进行位操作时尤为重要。有符号数和无符号数的位表示就存

发表于 11-24 07:50

使用Xilinx 7系列FPGA的四位乘法器设计

随着 IoT、边缘计算等应用对低位宽、高并行、高效率算术运算的需求攀升,基础算术电路,如 4 位乘法,如何在 FPGA 上做到“资源最小化+速度极致”便成为一道新的挑战。来自日本信州大学

一个提升蜂鸟E203性能的方法:乘除法器优化

,同样对于无符号乘法进行一位符号扩展后统一当作有符号数进行运算,另外,由于加减交替法迭代所得的结果存在着1比特精度的问题,因此还需要额外3个

发表于 10-27 07:16

E203V2长周期乘法器核心booth算法解读

E203V2乘法器所在模块为e203_exu_alu_muldiv.v,其中包含乘法和除法两大块,这里仅对乘法模块进行解读。

乘法模块首先进行booth编码,其目的为方便两个

发表于 10-24 09:33

(九)浮点乘法指令设计

⊕ sb,得到结果的符号位

阶码相加减

按照定点整数的加减法运算方法对两个浮点数的阶码进行加减运算,因为规格化数的价码e满足1≤e≤254,而ec有可能超出1~254范围,所以当1≤ec≤254,相乘结果

发表于 10-24 07:11

通过内联汇编调用乘法指令mulh\\mulhsu\\mulhu

高32位

mulhsurd, rs1,rs2

将rs1当作有符号数,rs2当作无符号数相乘,取高32位

2.由于C语言中的乘法符号,

发表于 10-24 06:52

Verilog实现使用Booth编码和Wallace树的定点补码乘法器原理

对于有符号整数乘法操作,E203使用常用的Booth编码产生部分积,然后使用迭代的方法,每个周期使用加法器对部分积进行累加,经过多个周期的迭代之后得到最终的乘积。其基本硬件原理图如图所

发表于 10-23 08:01

对于指令集中back2back情况的简单介绍

(64 位中的低 32 位)就用 mul 指令。要得到高 32 位,如果操作数都是有符号数,就用 mulh 指令;如果操作数都是无符号数,就

发表于 10-23 06:52

Booth编码的原理及选择

Booth提出该算法的初衷是基于当时计算机中的移位运算比加法运算要快这个硬件环境,其目的是通过移位运算代替部分加法运算来提高乘法运算速度。然而,Booth算法更大的优势在于,它对有符号数和无符

发表于 10-22 07:53

RISC-V M扩展介绍

。

3.硬件乘法器将两个操作数进行乘法运算,并将结果存放到指定的寄存器中。

4.如果乘法结果超出了寄存器的位数,需要进行截断以适应寄存器的大小。

需要注意的是,RISC-V

发表于 10-21 06:50

Copilot操作指南(一):使用图片生成原理图符号、PCB封装

的操作方法。 ” 图片生成原理图符号(Symbol) Copilot 支持图片生成原理图符号功能,支持原理图编辑器与符号编辑器两种场景。只需在 Copilot 中 @图片生成

FPGA有符号数乘法操作指南

FPGA有符号数乘法操作指南

评论