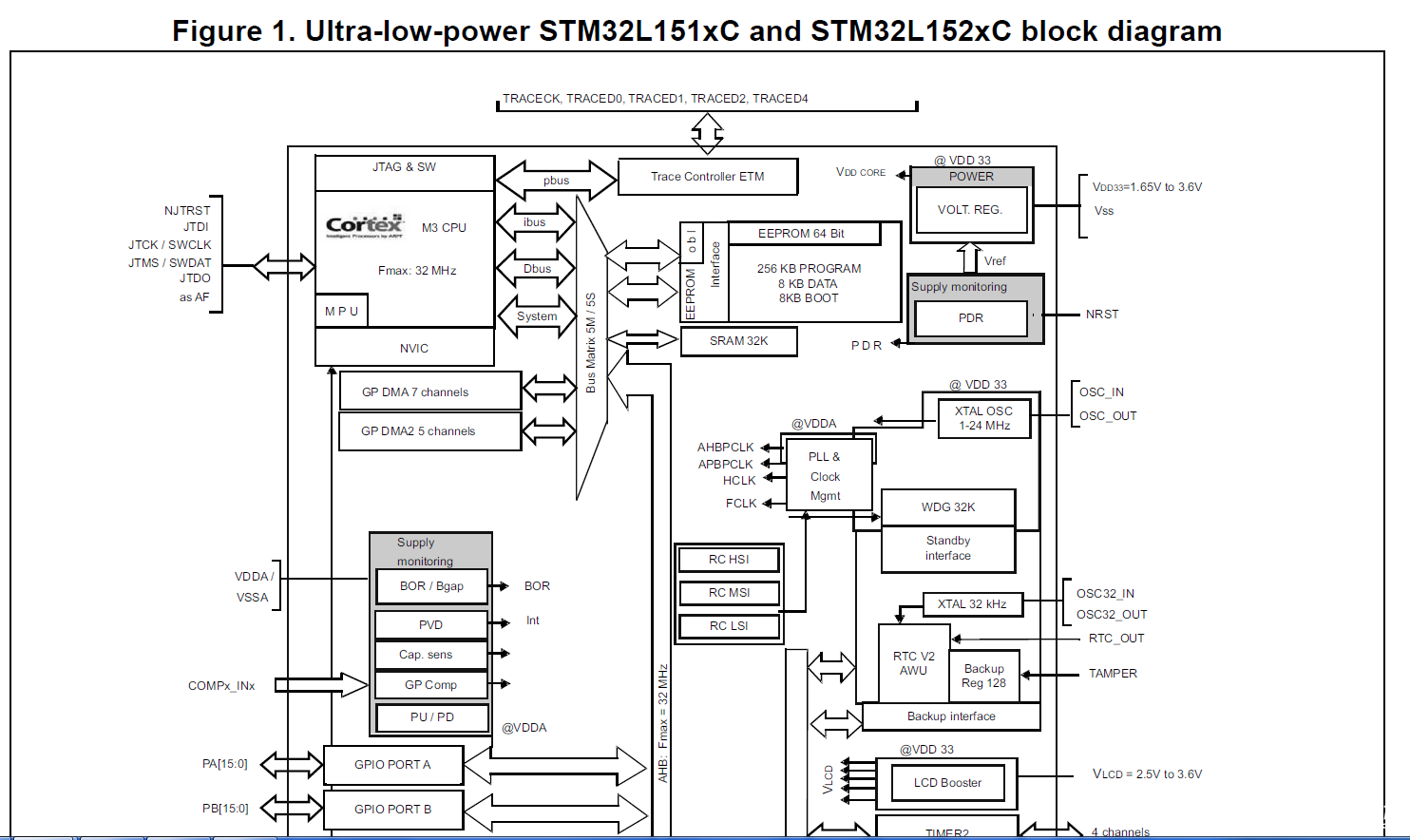

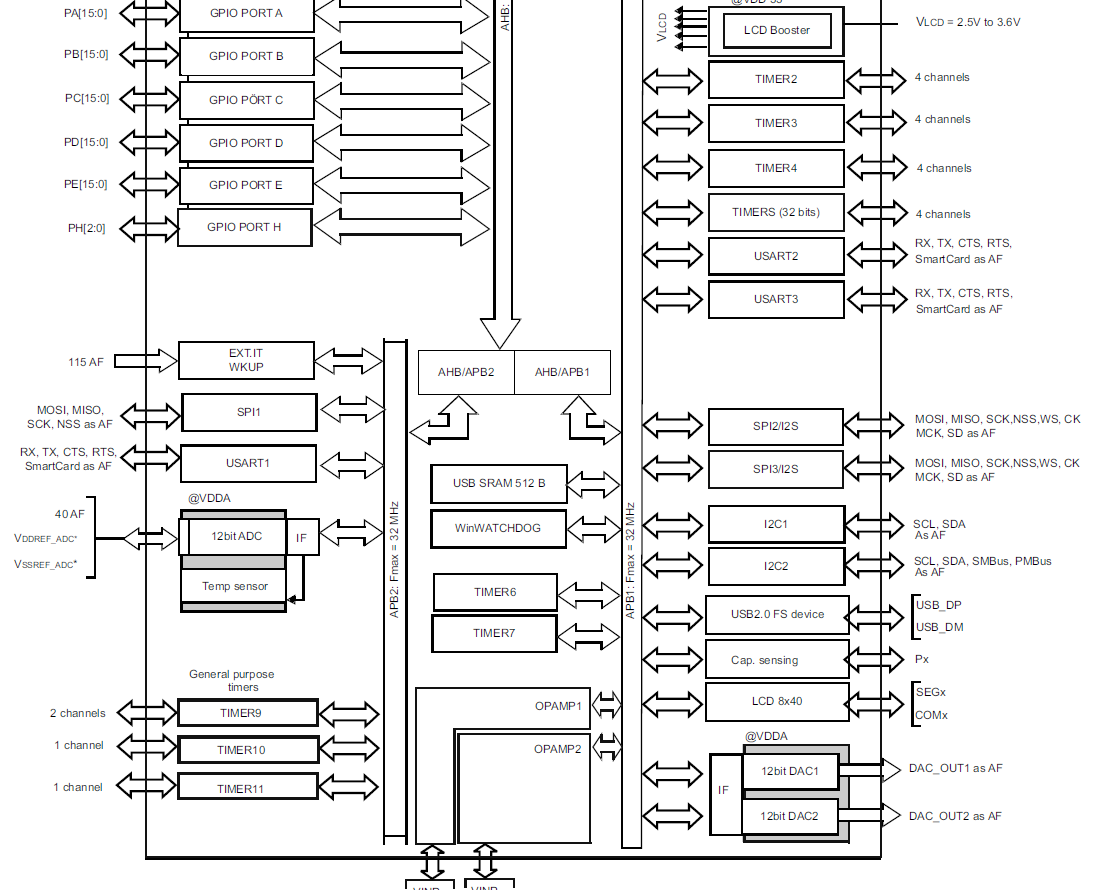

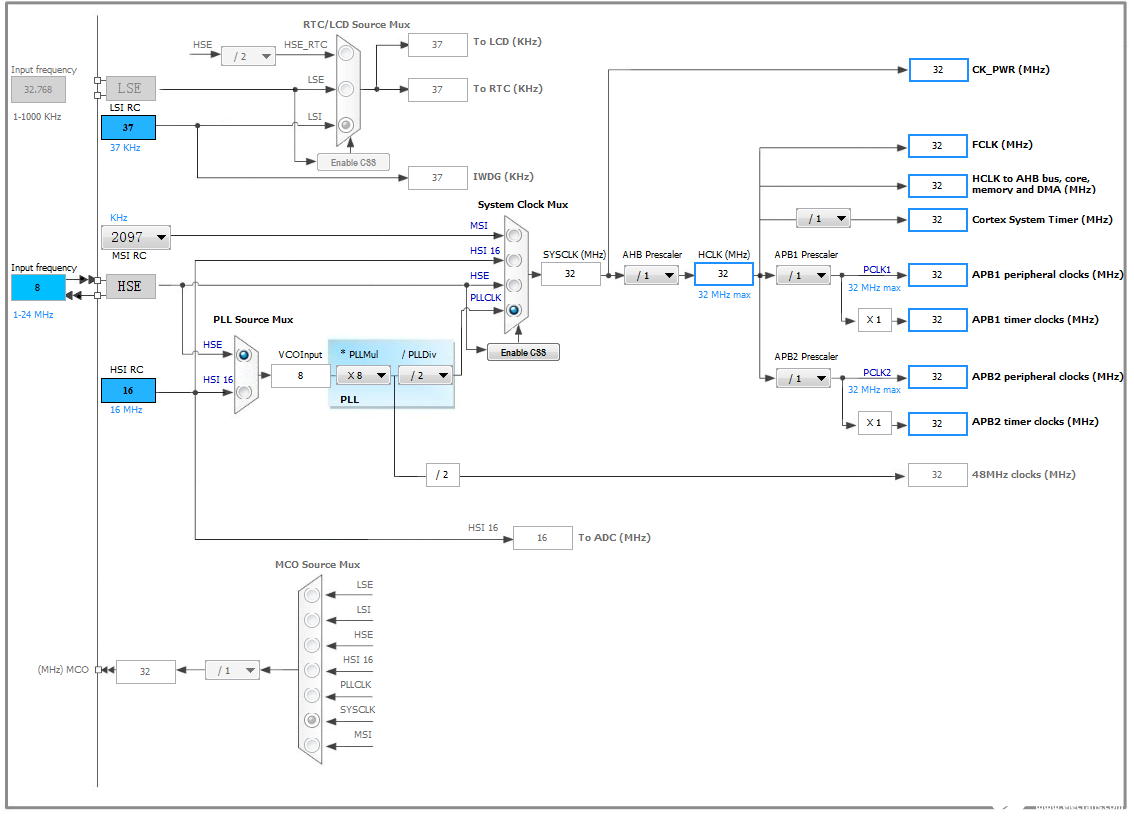

RCC:Reset and Clock Control,复位与时钟控制系统。系统复位有三种:系统复位、电源复位、RTC domain复位。本文重点详解Clock Control部分。下面看下STM32L152芯片的时钟框图和cubeMX软件中的时钟框图。

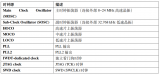

如上图所示,在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

①HSI:High Speed Internal,高速内部时钟,RC振荡器;

②HSE:High Speed External,高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源;

③LSI:Low Speed Internal,低速内部时钟,RC振荡器,频率为37kHz;

④LSE:Low Speed External,低速外部时钟,接频率为32.768kHz的石英晶体;

⑤PLL:Phase Locked Loop,锁相环倍频分频输出。

另外,STM32还具有双时钟机制,即时钟安全系统CSS(Clock Security System)。在外部晶振不工作时,转而使用内部RC振荡器作为自己时钟心跳保证系统正常运行。当外部晶振恢复正常后,重新使用外部晶振。

上图中也提到3种时钟,FCLK、HCLK和PCLK。简单介绍下三种时钟。

(1)FCLK:Free Running Clock,为CPU提供时钟信号,平时说的CPU主频,就是这个时钟信号,1/Fclk即为CPU时钟周期;

(2)HCLK:为AHB bus peripherals提供时钟信号,AHB:advanced high-performance bus;HCLK是高速外设时钟,一般给内存、flash提供时钟。

(3)PCLK:为APB bus peripherals供给时钟信号,APB:advanced peripherals bus;PCLK是低速外设时钟,一般给CAN、USB、I2C、USART、SPI、Timer、ADC和DAC提供时钟信号。下面结合Cubemx生成的系统时钟原程序进行分析。

void SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct;

RCC_ClkInitTypeDef RCC_ClkInitStruct;

RCC_PeriphCLKInitTypeDef PeriphClkInit;

/**Configure the main internal regulator output voltage

*/

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE1);//设置调压器输出电压级别1,用来设置调压器输出电压级别,器件未以最大频率工作,达到性能和功耗平衡

/**Initializes the CPU, AHB and APB busses clocks

*/

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSI|RCC_OSCILLATORTYPE_LSI

|RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_ON;

RCC_OscInitStruct.HSIState = RCC_HSI_ON;

RCC_OscInitStruct.HSICalibrationValue = 16;//HSI时钟16M

RCC_OscInitStruct.LSIState = RCC_LSI_ON;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;//PLL时钟源为HSE

RCC_OscInitStruct.PLL.PLLMUL = RCC_PLL_MUL8;//8倍频

RCC_OscInitStruct.PLL.PLLDIV = RCC_PLL_DIV2;//2分频

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)//初始化

{

_Error_Handler(__FILE__, __LINE__);

}

/**Initializes the CPU, AHB and APB busses clocks

*/

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_SYSCLK

|RCC_CLOCKTYPE_PCLK1|RCC_CLOCKTYPE_PCLK2;

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1;//AHB 1分频

RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV1;//APB1 1分频

RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV1;//APB2 1分频

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_1) != HAL_OK)//初始化

{

_Error_Handler(__FILE__, __LINE__);

}

PeriphClkInit.PeriphClockSelection = RCC_PERIPHCLK_RTC;

PeriphClkInit.RTCClockSelection = RCC_RTCCLKSOURCE_LSI;//RTC时钟选择LSI

if (HAL_RCCEx_PeriphCLKConfig(&PeriphClkInit) != HAL_OK)

{

_Error_Handler(__FILE__, __LINE__);

}

/**Configure the Systick interrupt time

*/

HAL_SYSTICK_Config(HAL_RCC_GetHCLKFreq()/1000);//滴答定时器配置

/**Configure the Systick

*/

HAL_SYSTICK_CLKSourceConfig(SYSTICK_CLKSOURCE_HCLK);//滴答定时器选择HCLK 不分频

/* SysTick_IRQn interrupt configuration */

HAL_NVIC_SetPriority(SysTick_IRQn, 0, 0);//滴答定时器中断优先级

责任编辑:gt

-

电源

+关注

关注

185文章

18979浏览量

264474 -

控制系统

+关注

关注

41文章

6987浏览量

114376 -

时钟

+关注

关注

11文章

1999浏览量

135226

发布评论请先 登录

SysClk系统时钟的切换

PLC控制系统应用的抗干扰问题分析及处理措施

瑞萨RA系列FSP库开发实战指南(29)CGC(时钟生成电路)时钟控制

RCC时钟控制系统组成及时钟原程序分析

RCC时钟控制系统组成及时钟原程序分析

评论