降低片上功耗已成为纳米技术时代的关键挑战。现在,性能和面积之间的传统权衡因此增加了权力。

与功耗相关的问题不仅适用于电池供电,手持和移动应用,还包括90nm及以上的所有产品,其功率不仅会影响设计上市时间,还会影响成本和可靠性。

为什么功耗低

在进入分析和降低功耗的细节之前,我们首先要看看为什么它如此关键在今天的设计中。

在SoC中不断增加的功能,性能和集成应用的持续趋势导致功耗在数百瓦的设计。这可以从英特尔的最新处理器变体中看出,例如,Itanium2接近130瓦[1]。这类器件需要昂贵的封装,散热片和冷却环境。

这导致了许多其他问题需要解决,以保持未来应用的可行性。与前几代产品相比,移动应用程序集成度的提高对产品的电池寿命提出了更高的要求。虽然CMOS技术的进步使晶体管密度大约每18个月翻一番,但电池技术的同等进步大于每五年。

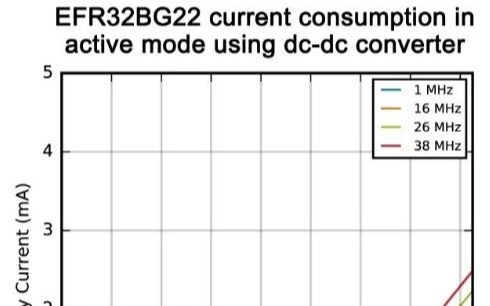

芯片上有大电流会缩短使用寿命和可靠性的产品。随着频率的增加,充电(和放电)总负载电容所需的平均片上电流也增加,而电流浪涌的时间导致器件的配电网络上的功率波动。

这些动态电压降是产生延迟不确定性的一个问题,导致可能的功能问题,并最终通过完整的器件故障缩短产品寿命[2]。最后,作为整体系统设计的一部分,如何解决器件耗散的功率问题变得越来越昂贵。

耗电的地方

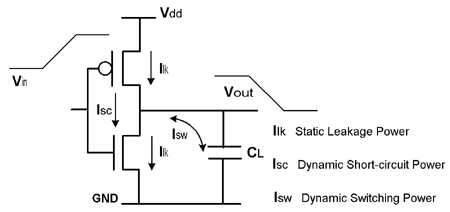

设备内的功耗可以分为两种基本类型 - 基于开关活动的动态功耗和基于泄漏的静态功耗。由于电路驱动的容性负载的充电和放电(包括净电容和输入负载),动态功耗可以分解为开关功率,并且当成对的PMOS和NMOS晶体管在切换期间瞬间发生短路功率。同时进行。

泄漏功率也可以分解为许多关键贡献者。一个是流过在扩散区和衬底之间形成的反向偏置二极管的电流(I 二极管)。另一种是流过不导通的晶体管的电流,隧道穿过栅极氧化物(I subthreshold )。请注意,设备的泄漏会受到工作温度的极大影响。因此,随着芯片升温,静态功耗呈指数增长。

图1 - CMOS功耗

泄漏在具有0.7V阈值的130nm工艺中,每个晶体管产生大约10-20pA的电流;在同一过程中将阈值降低至0.3V,并且每个晶体管的漏电流火箭升至10-20 nA,在较小的几何结构中呈指数增长。

因此可以看出,泄漏受Vth相对于Vdd,晶体管尺寸和温度的接近程度的影响。 David J. Frank [3]和Tadahiro Kuroda [4]在论文中深入讨论了变化和优化Vdd和Vth的影响。

以下等式定义了器件内的功率:

泄漏 =(I二极管 +I亚阈值)* V

A=开关活动

C=总负载电容

V=电源电压

F=目标频率

B=增益系数

T=上升/下降时间(门输入)

V th=电压阈值

P 总计 = P 动态 + P 短 + P 泄漏

P 开关 = A * C * V 2 * F P short = A(B/12)(V-2V th ) 3 * F * T

注意,消耗不是恒定的,即使平均功率消耗,峰值功率也是由于电迁移和电压下降引起的故障的一个重要问题离子很低。

我们可以做些什么来降低功耗

在针对低功耗应用的SoC架构中,我们必须首先完全理解将定义功率预算。这些可以源自某些形式的基于标准的要求,其限制在某些条件下的电流消耗,或者在移动应用的情况下可延长电池的寿命。针对目标应用的解决方案将在设备的控制和架构方面有所不同。

一旦明确定义了要求,我们就可以开始探索各种架构并确定潜在的权衡。从最高抽象层次开始,最大限度节省的潜力,并通过设计抽象层次进一步完善,我们可以不断将功率节省向下推向目标预算。

图2 - 通过抽象级别减少回报

在最终确定SoC架构时,需要在各个阶段做出一些考虑和决定。设计抽象以达到最佳解决方案。这些要求包括系统性能,处理器和其他IP选择,要设计的新模块,目标技术,要考虑的电源域数量,目标时钟频率,时钟分配和结构,I/O要求,内存要求,模拟功能和电压调节。所有这些都是功率预算的贡献者,因此可以针对功耗最小化来实现低功耗目标。

在将架构的所有部分组合在一起时,接下来我们需要了解可用于降低系统总体功耗的全局控制和时钟功能。对于各种应用需求,设计可能有许多操作模式,例如启动,活动,待机,空闲和断电。

在某些情况下,这些模式的多个级别将用于实现最佳的整体电源管理策略。这些模式通常通过软件和硬件功能的组合来控制,并且需要从设计过程的早期阶段计划到系统开发中。

从前面描述的等式中,它可以可以看出,尽可能节省功率的最佳方法是将电压调整到所需性能的最佳水平。然而,降低电压电平的影响是增加栅极延迟,并超出一定程度,这变得不可行。

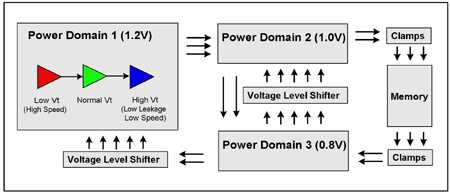

理想的解决方案是采用不同的工作模式,目标是尽可能减少给定应用的设计电流,从而降低动态和漏电功率。例如,在待机模式下,应在低电压域上维持所需的最小逻辑量,以便根据某些外部事件使设备退出此状态,然后通过操作模式转换到所需的性能级别。

虽然此解决方案提供了最大的节省,但它在复杂性方面也带来了最大的开销。这些考虑因素包括片内或片外开关调节,电源域隔离,与切换和恢复稳定电源相关的延迟的性能影响,以及触发器和需要保存和恢复例程的存储器的潜在状态损失,以及所有其他相关的测试和验证要求。

在开发此类实施时,需要考虑上述所有项目以及管理可实现这一目标的时间段的可行性。

图3 - 多域结构示例

包含多个域但没有切换或缩放的简单实现将从二次电压效应中获得一些相关的好处。在这些情况下,需要考虑将设计划分为高性能/高电压和低性能/低电压。

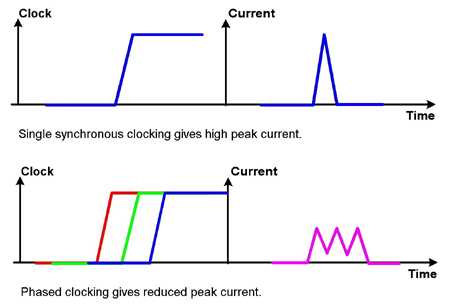

在定义电压分配和缩放后,下一级考虑应该是系统级时钟架构和控制频率和相关切换级别的方法。虽然它没有通过泄漏解决功耗问题,但这种方法在降低器件的动态功耗方面还有很长的路要走。

设计使时钟分配和时钟元素消耗超过设备总功耗的50%并不罕见[5]。注意,如果实现频率缩放可以与任何电压缩放成正比,以满足所需的系统级性能。

在给定的空闲或休眠模式下,所有非相关模块都可以完全从树的路径中关闭,从而消除了设计这些部分中时钟分布和逻辑的切换。使用多个时钟域,频率调整和频率相位来降低峰值功率都可以从中央分配管理。

图4 - 时钟定相

时钟架构的控制通常通过处理器提供的软件接口进行控制。然而,也可以实现用于按需激活的动态硬件控制切换 - 例如,在支持数据流量突发所需的某些解码器功能的情况下。这些类型的功能减少了总软件序列支持和系统延迟。

在定义的系统时钟架构的所有上述实现方面,需要详细考虑以避免所有形式的时钟故障,额外的开销在功能测试,偏斜控制,测试考虑设计和时序收敛影响方面与多个域相关联。

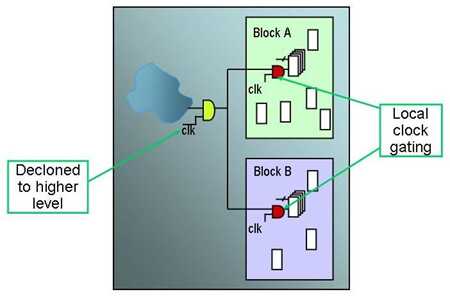

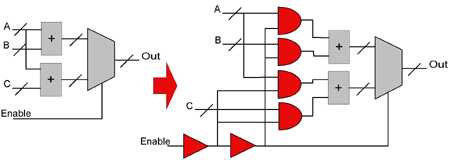

一旦捕获了设计架构,RTL代码现在可以针对低功耗合成流程,自动交易权力以及普遍接受的表现和区域限制。这些工具的主要特点包括多阈值泄漏优化,多电源电压域,基于本地锁存器的时钟门控,去克隆和重新克隆重构,操作数隔离和门级功率优化。

多阈值泄漏优化,通常使用多达三个版本的目标库:低V th (快速,高泄漏),标准V th 和高V th (慢,低泄漏)。该工具将尽可能多地使用高阈值单元,同时保持时序约束,仅将低阈值单元用于关键路径。显然,选择和定位适当的库和表征应用程序性能要求是一个关键考虑因素,应该在设计过程的早期解决。

图5 - 多电压阈值泄漏优化

为了支持多个电压域,需要针对目标电压的附加特征库。这些还可以包括其中的多个阈值变体。功率方面的成本节省显然与二次电压缩放效应有关。除了一致且支持的工具流程外,管理域分区还需要在开发的早期阶段仔细考虑设计,并在前端设计和布局处理之间进行紧密集成,以支持上述所有方法。

如果启用,基于本地锁存器的时钟门控通常会在关联触发器的组或组之前尽可能插入特定于库的时钟门控锁存器。这样做的效果是减少不必要的时钟切换到相关的触发器。

用户通常可以定义从单个时钟门驱动的触发器范围,以避免时钟分配网络中出现任何不必要的不平衡。每个时钟门控单元为时钟路径提供功能和测试激活使能,如果需要达到所需的目标ATPG覆盖范围,可选择添加可观察性。

关于时钟门控,可以使用物理数据添加额外的步骤来重构时钟门控,从而进一步降低功耗和面积。这是通过寄存器和门控单元的相对位置实现的,从而减少了碎片和复制。在可能的情况下,时钟门控单元到触发器的原始逻辑分区将被重构以提供更物理的布局友好结构。

图7—时钟门重组

完整的流程有很多步骤。在预布局设计中,本地时钟门控被去克隆到更高的公共级别,减少了区域并为时钟树合成(CTS)创建了更清晰的起点。然后在详细的放置/CTS阶段,可以重新克隆本地时钟门控单元以提供最佳的所需时钟树。

操作数隔离步骤自动识别和关闭数据路径元素和分层组合模块共同的控制信号。该工具仅部分承诺重组,以实现最佳时序和功率权衡。

图8—操作数隔离

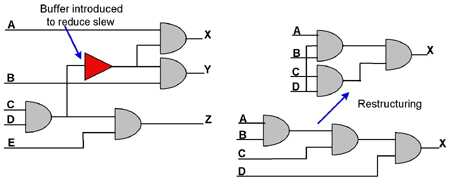

经典门级优化调整单元大小,执行引脚交换,删除不必要的缓冲,合并门,添加缓冲区以减少压摆,并重构逻辑以提供最佳的功耗优化。然而,这些步骤中的大多数也在具有实际布局和线长约束的物理域中重新进行。

图9—门级优化中心

基线流与采用上述技术的低功耗合成流之间的比较数表明采用90纳米技术的嵌入式处理器器件,大约650K门可以动态开关电源和漏电功率可节省大于40%[6]。

-

soc

+关注

关注

40文章

4624浏览量

230191 -

低功耗设计

+关注

关注

0文章

127浏览量

16792

发布评论请先 登录

Arm SoC芯片低功耗设计分享会在深圳成功举办

最新SOC低功耗带学习码接收方案

基于Foundation IP的低功耗IoT SoC实现

如何设计超低功耗的嵌入式应用?

【书籍评测活动NO.19】 SoC底层软件低功耗系统设计与实现

《SoC底层软件低功耗系统设计与实现》阅读笔记

如何选择低功耗蓝牙SoC

低功耗蓝牙模块备受欢迎的原因有哪些?

低功耗SoC设计的原因有哪些

低功耗SoC设计的原因有哪些

评论