很多刚接触阻抗的人都会有这个疑问,为什么常见的板内单端走线都是默认要求按照50欧姆来管控而不是40欧姆或者60欧姆?这是一个看似简单但又不好回答的问题。在写这篇文章前我们也查找了很多资料,其中最有知名度的是Howard Johnson, PhD关于此问题的答复,相信很多人都有看过。

为什么说不好回答呢?信号完整性问题本身就是一个权衡取舍的问题,所以在业内最著名的一句话也就是:“It depends……” 这就是没有标准答案,仁者见仁智者见智的一个问题。今天高速先生也就这个问题综合各种答复来简单总结下,在此也是抛砖引玉,希望更多的人可以从各自的角度出发总结出更多相关的因素。

首先,50欧姆是有一定历史渊源的,这得从标准线缆说起。我们都知道近代电子技术很大一部分是来源于军队,慢慢的军用转为民用,在微波应用的初期,二次世界大战期间,阻抗的选择完全依赖于使用的需要。随着技术的进步,需要给出阻抗标准,以便在经济性和方便性上取得平衡。在美国,最多使用的导管是由现有的标尺竿和水管连接成的,51.5欧姆十分常见,但看到和用到的适配器/转换器又是50欧姆到51.5欧姆;为联合陆军和海军解决这些问题,一个名为JAN的组织成立了,就是后来的DESC,由MIL特别发展的,综合考虑后最终选择了50欧姆,并且特别的导管被制造出来,并由此转化为各种线缆的标准。此时欧洲标准是60欧姆,不久以后,在象Hewlett-Packard这样在业界占统治地位的公司的影响下,欧洲人也被迫改变了,所以50欧姆最终成为业界的一个标准沿袭下来,也就变成约定俗成了,而和各种线缆连接的PCB,为了阻抗的匹配,最终也是按照50欧姆阻抗标准来要求了。

其次,从线路板制作可实现的角度出发,50欧姆实现起来比较方便。从前面阻抗计算公式可知,过低的阻抗需要较宽的线宽以及薄介质(或较大的介电常数),这对于目前高密板来说空间上比较难满足;过高的阻抗又需要较细的线宽及较厚的介质(或较小的介电常数),不利于EMI及串扰的抑制,同时对于多层板及从量产的角度来讲加工的可靠性会比较差;而50欧姆在常用材料的环境下普通的线宽和介质厚度(4~6mil)即符合设计要求(如下图一阻抗计算),又方便加工,慢慢的成为默认选择也就不足为奇了。

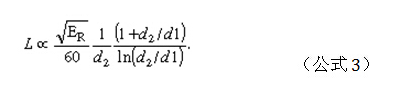

第三,从损耗的角度出发,根据基本的物理学可以证明50欧姆阻抗趋肤效应损耗最小(摘自Howard Johnson, PhD的回复)。通常电缆的趋肤效应损耗L(以分贝做单位)和总的趋肤效应电阻R(单位长度)除以特性阻抗Z0成正比。总的趋肤效应电阻R是屏蔽层和中间导体电阻之和。屏蔽层的趋肤效应电阻在高频时,和它的直径d2成反比。同轴电缆内部导体的趋肤效应电阻在高频时,和他的直径d1成反比。总共的串联电阻R,因此和(1/d2+1/d1)成正比。综合这些因素,给定d2和相应的隔离材料的介电常数Er,可以用以下公式来使得趋肤效应损耗最小。

在任何关于电磁场和微波的基础书中,都可以找到Z0是d2,d1和Er的函数。

把公式2代入公式1中,分子分母同时乘以d2,整理得到

从公式3分离出常数项( /60)*(1/d2),有效的项((1+d2/d1)/ln(d2/d1))来确定最小值点。仔细查看公式3的最小值点仅由d2/d1控制,和Er以及固定值d2无关。以d2/d1为参数,为L做图,显示d2/d1=3.5911时,取得最小值。假定固态聚乙烯的介电常数为2.25,d2/d1=3.5911 得出特性阻抗为51.1欧姆。很久之前,无线电工程师为了方便使用,把这个值近似为50欧姆作为同轴电缆最优值。这证明了在50欧姆附近,L是最小的。

最后,从电气性能的角度看,50欧姆的优势也是综合考虑之后的折中。单纯从PCB走线的性能来说,阻抗低比较好,对一个给定线宽的传输线,和平面距离越近,相应的EMI会减小,串扰也会因此减小,同时也不易受容性负载影响。但从全路径的角度看,还需要考虑最关键的一个因素,那就是芯片的驱动能力,早期大多数芯片驱动不了阻抗小于50欧姆的传输线,而更高阻抗的传输线由于实现起来不便,所以折中采用了50欧姆阻抗。

综上所述:50欧姆作为业界的默认值有其先天的优势,同时也是综合考虑后的折中方案,但并不是说就一定要用50欧姆阻抗了,很多时候还是取决于与之匹配的接口,如75欧姆仍然是远程通讯的标准,一些线缆和天线都是使用的75欧姆,此时就需要与之匹配的PCB线路阻抗。另外还有一些特殊的芯片通过改善芯片驱动能力,来降低传输线的阻抗,以此得到更好的抑制EMI和串扰的效果,如Intel的多数芯片要求阻抗控制在37欧姆、42欧姆甚至更低,在此不再赘述。

-

电路板

+关注

关注

140文章

5257浏览量

106518 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44394

发布评论请先 登录

KT148A语音芯片坏片原因分析 阻抗 供电脚异常及硬件改良方案

50 欧姆、高 IP3、低噪声宽带增益模块 skyworksinc

高压单端探头:高电压测量的基础与精要

高压单端探头设计时,地线处理方法的研究

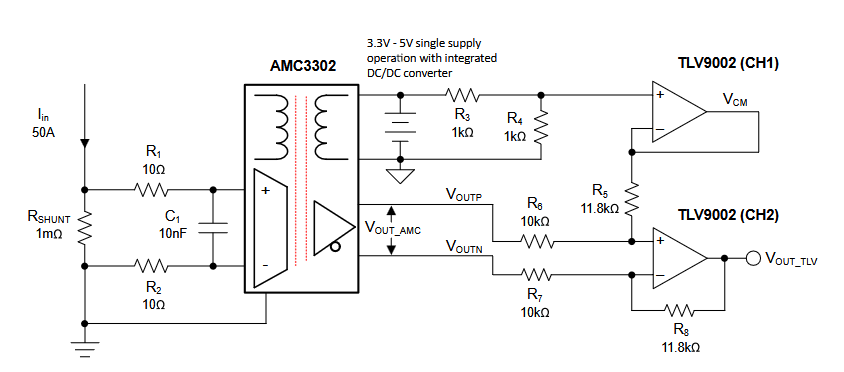

具有±50mV输入和单端输出的隔离式电流检测电路

PCB上的单端阻抗控制50欧姆的原因是什么

PCB上的单端阻抗控制50欧姆的原因是什么

评论