Kilopass Technology,Inc。宣布其XPM技术现在可用于ASIC和SoC,使用标准逻辑CMOS 90纳米硅工艺,以及目前使用0.18,0.15和0.13微米工艺的产品。

XPM,a独特的嵌入式一次性可编程(OTP)NVM技术,提供可扩展性与先进硅工艺的组合,例如90纳米,低标准逻辑CMOS制造成本,从几位到多兆位的存储密度以及高度安全的存储。凭借其完整的位尺寸范围和广泛的应用,XPM几乎可以增强任何芯片设计。

博士。 Kilopass Technology首席执行官Jack Peng指出,“我们已经将我们的专利XPM技术发送给了十几个客户,我们非常高兴地宣布,我们已经测试并验证了90纳米的硅,1000小时的老化,我们的客户希望在未来几个月内从硅原型转向大批量生产。“

作为外部存储芯片的替代品,XPM技术可用于高密度嵌入式存储器应用,用于发布游戏,电影和其他多媒体内容,以及嵌入式MCU和基于DSP的系统中的安全固件存储。 XPM还可用于智能卡的安全ID和数据存储,嵌入式ID和参数存储,存储加密密钥,模拟微调和校准参数存储,存储唯一配置代码和嵌入式存储器修复。

有关XPM技术的更多信息

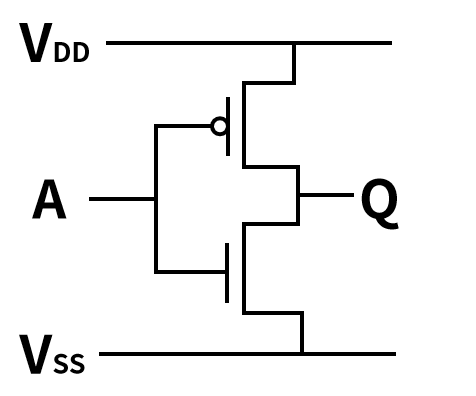

XPM专利的熔丝可编程技术每个存储器单元使用1.5个晶体管,可通过外部或内部电压源以低编程电流进行编程,并提供快速读取访问时间40nsec - 70nsec(1Mbit,0.18微米工艺)。需要多次编程的应用可以使用多扇区方法,最小的芯片面积损失。例如,从1K位基于XPM的存储器到8K位的大小调整提供了8个扇区,用于有限时间的可重新编程,并且它增加了可忽略不计的裸片面积。

XPM内存技术可靠性&安全性

XPM技术非常安全。数据在大多数系统(超过20年)的使用寿命期间永久保留,并且不受逆向工程的影响,因为无法通过显微镜或电压对比测试来检测存储的数据。

可用性

现在可以获得XPM内存技术的许可证,包括GDSII布局以及模拟和时序模型。

-

CMOS

+关注

关注

58文章

6186浏览量

241582 -

asic

+关注

关注

34文章

1269浏览量

124057 -

XPM

+关注

关注

0文章

12浏览量

8889

发布评论请先 登录

单片机TTL和CMOS电平知识

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

CMOS的逻辑门如何应用在电路中

实用电子电路设计(全6本)——数字逻辑电路的ASIC设计

使用BCU和标准逻辑分析仪Saleae进行功率测量时不匹配怎么解决?

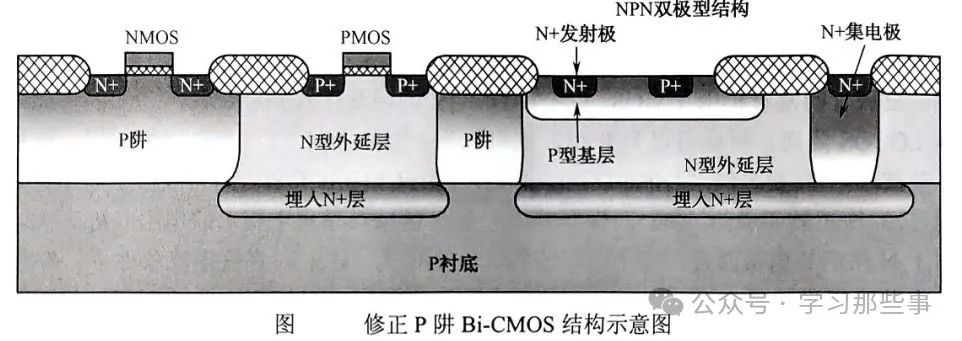

CMOS,Bipolar,FET这三种工艺的优缺点是什么?

IEDM 2024先进工艺探讨(三):2D材料技术的进展及所遇挑战

XPM技术使用标准逻辑CMOS 90纳米硅工艺 现在可用于ASIC和SoC

XPM技术使用标准逻辑CMOS 90纳米硅工艺 现在可用于ASIC和SoC

评论