EDA行业的历史不断受到技术周期性动荡以及权力平衡的影响。随着电子设计自动化(EDA)解决方案的创建,半导体工艺技术的进步和不断增加的上市时间需求成为必然。诸如综合等关键技术正在成为商品,传统的逻辑和物理设计流程所依赖的基础不再适用。当前的多供应商,多工具设计流程无法充分解决时序收敛问题,也无法解决数百万门设计问题。设计人员真正需要的是单一的集成系统,它可以将设计直接从RTL流向GDSII,并保证性能良好。

这一突破性解决方案将从何而来?从最新起点,。以综合为例。 Synopsys Design Compiler在12年前取得了突破,但直到Ambit的BuildGates来到它之前,它几乎停滞不前。 BuildGates为逻辑综合带来了三项重大改进:更大容量(高达100K门),在时序相关优化期间获得更好的结果,以及为大型设计提供分布式综合的时间预算。 Synopsys通过对DC进行略微改进,回应了其首个再合成竞争对手Ambit。但是,用户仍然坚持使用已有12年历史的DC技术。

地方和路线并没有停滞不前,因为每走一步都需要两步。这主要是由于Cadence习惯于获得体面的技术,然后将其用于老化的设计流程而不是整合它。这为他们创造了一个有利可图的设计服务业务,因为它需要专家们弄清楚如何将所有点工具有效地组合在一起。但是,Cadence最后一次开发出更好的,新的布局布线工具是什么时候?

由于他们需要保持Wallstreet的快乐,Cadence和Synopsys声称他们拥有或接近拥有RTL GDSIIflow可减少迭代次数并解决信号完整性和时序收敛问题。毫不奇怪,消除迭代,大型设计的容量和保证时序收敛不是他们的功能列表。我赞扬他们的诚实,因为他们无法提供这些信息。

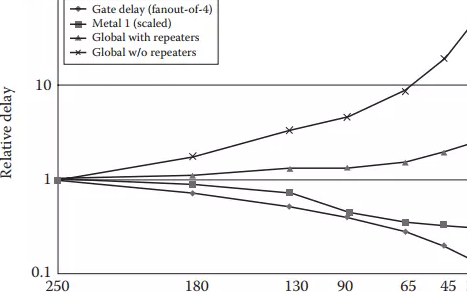

半导体工艺技术的特征尺寸的不断减少为这些传统的合成,布局和布线系统带来了难以克服的问题。大多数这些工具是在10 - 15年前开发的,当时10K门设计是最后的,面积是最严峻的挑战,互连延迟是不可忽视的。那时候合成与布局和布线之间的差距不是问题。

在今天的DSM设计中,互连布线代表了电路中延迟的绝大部分。与门延迟不同,互连延迟在逻辑设计期间难以预测,因为它取决于硅的最终物理布局。因此,对于传统的EDA解决方案,硅设计团队必须在逻辑和物理设计之间进行多次迭代,以满足时序要求,通常会延迟产品发布数月。

虽然Synopsys和Cadence已经发布了关于物理编译器和PKS的重大声明 - 他们目前对RTL toGDSII流问题的回答 - 他们实际上只是在“综合”产品中重新包装存在的合成,放置和全局路由引擎。如果这些公司了解如何解决设计师的问题和需求,他们就会知道设计师需要处理1M到10M门设计的工具,而仅仅是减少工作是不够的。

为了满足这些解决方案的时间安排,当通过优化使布局估计无效并且必须以与技术无关的方式显着重构设计的某些部分时,仍需要迭代。此外,新解决方案还需要在详细布局和布线之间进行迭代,因为它们不提供详细的布局规划。如果没有详细的布局规划,这些方法必须使用guesstimates formacro和pad placement。由两个宏组成的关键路径的时序仅由几个逻辑级别组成,高度依赖于精确的宏位置。

由于这些方法无法保证芯片性能,因此设计人员对这些工具进行基准测试需要通过整个芯片设计流向GDSII。只有使用无DRC的GDSII,才能知道他的芯片是否符合时序要求。

这些新的解决方案也受到100K门综合容量限制的阻碍。布局和布线算法通过扁平设计产生最佳结果。为了利用这些胶溶液,物理块现在被限制在合成的极限,并且需要基于极限的限制来定义层次边界。时序收敛的严重问题发生在1M +门设计中,并且是长线,宏和焊盘放置的直接结果。

为GDSII解决方案提供完整的集成RTL,可以减少迭代次数,保证时序,并且处理大型设计平板,逻辑和物理设计技术的能力必须完全重新设计。综合必须不再依赖于随机线载模型或初始布局的估计来管理互连延迟。合成必须与使用时序作为主要约束的完整物理设计解决方案紧密集成。为了实现必要的集成级别,此解决方案必须在单个统一的数据架构上运行,以允许工具同时工作。由于Cadence和Synopsys显然无法提供这样的解决方案,它将从何而来?无一例外,创业公司推动了技术的进步,改变了行业的力量平衡。如果EDA历史记录是任何指标,那么只有创业公司可以通过这种革命性的解决方案。

-

RTL

+关注

关注

1文章

395浏览量

62865 -

GDSII

+关注

关注

0文章

6浏览量

9195 -

PCB打样

+关注

关注

17文章

2982浏览量

23672 -

华强PCB

+关注

关注

8文章

1831浏览量

29323 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44706

发布评论请先 登录

MAX1969EUI的电流方向从始终从OS1流向OS2?

[求助]GDSII和ASCII格式互换!!!

GDSII是什么?什么是GDSII文件

信号流向问题

pcb如何规划信号流向图

三星使用Cadence统一数字流程实现20nm芯片流片

Cadence提供新一代Encounter RTL-to-GDSII流程

RTL8139C RTL8139C-LF RTL8139CL RTL8139CL-LF

我们处于EDA融合时代 更多的算法工具涌现

从RTL追踪到Scala

Vivado中对RTL源文件如何进行加密

直接在网表中插入RTL来快速做芯片功能ECO

设计直接从RTL流向GDSII

设计直接从RTL流向GDSII

评论