作为商业上最成功的on-chip ESD 公司,从2002成立之初到现在经历了15年,员工也从1-2个人发展到目前的17个人。回顾这家从IMEC SPIN OFF的小而美的公司,总结起来有几点是值得国内公司借鉴的。

正确的切入点:

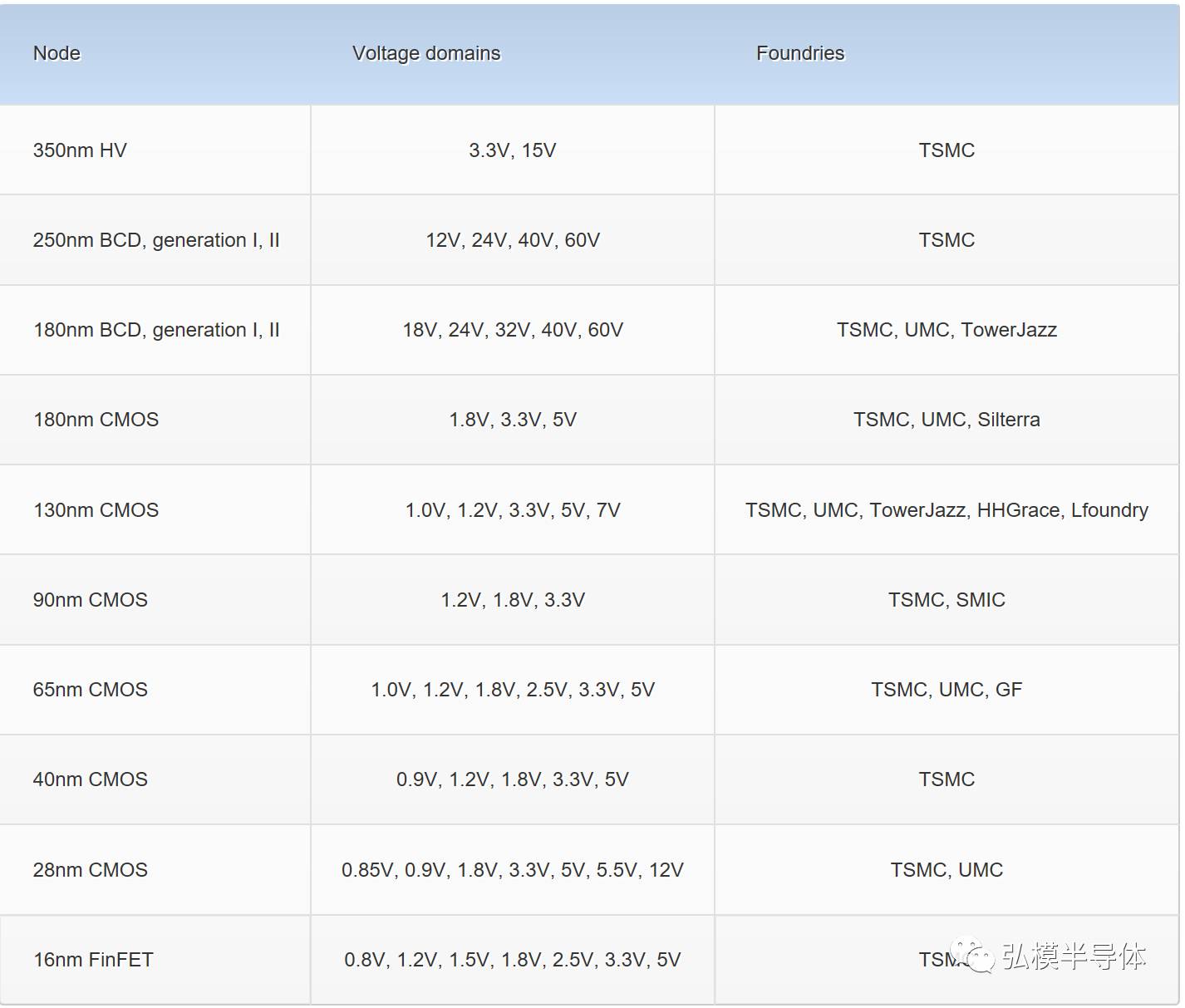

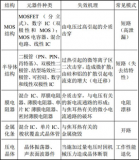

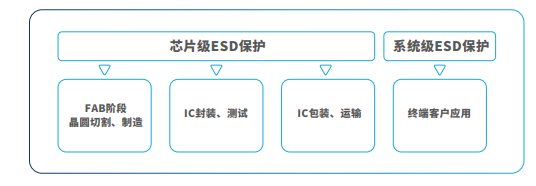

作为半导体厂,本身也有自身的ESD部门,Sofics很好的避开了和半导体厂的冲突,寻找更有特色的ESD解决方案,比如超低功耗,高速,超高压方面的产品应用,同时也选择对ESD有特别要求的BCD工艺的设计下手,通过省MASK, 省ESD面积,提高性能和TIME TO MAREKT,YIELD让客户得益的同时,自己在这个市场也获得一席之地。经过长时间的客户积累,on-Chip ESD 解决方案覆盖了TSMC主流工艺, 也使得ESD IP转移到任何T-LIKE的FAB非常迅速,成功率非常高(>95%). 如果看不清下面的图片,请点击放大

除了以上工艺,对于SOI, 3DIC,RAD-HARD 抗辐射等,Sofics 都有完整解决方案。 Sofics 也有ESD设计的EDA工具TAKE CHARGE 和 POWER QUBICS,分别覆盖标准IO界面0-5V和5-100V的on-chip ESD 解决方案,让设计公司对ESD设计兴手拈来。 同时,对于客户的私人定制的高性能IO和特殊要求IO, Sofics也有自己的应对方案,尽量满足客户需求,总的来说,在Sofics这边,总能找到一款适合你的on-Chip ESD方案。

2. 核心技术:

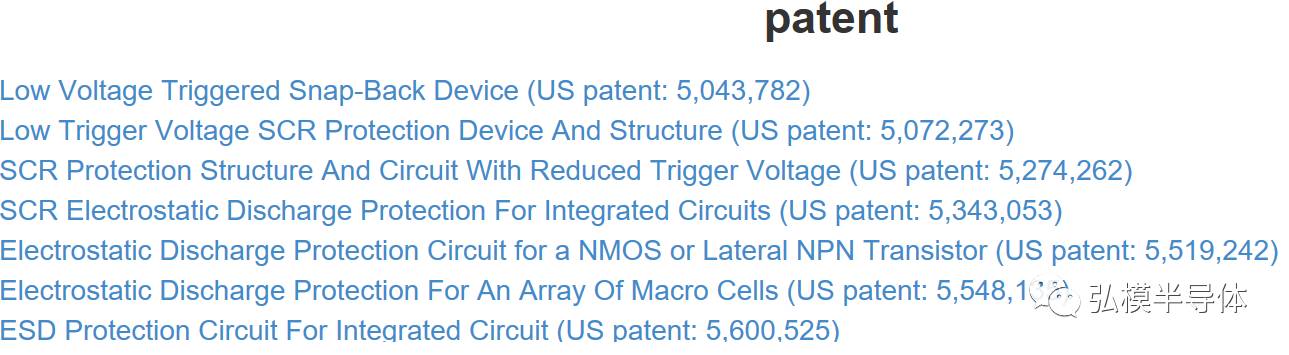

俗话说,打铁还需自身硬,在这个方面,Sofics 是个典型的例子。 他们从不吝啬用每年收入的10%左右来进行技术开发,目前拥有在ESD方面的专利有75个之多,下面只是一些例子,这些专利成为了支持Sofics 快速成长的坚实基础。

3. 商业模式:

Sofics 主要采用ESD IP,EDA SOFTWARE的授权模式。合作伙伴主要是半导体厂和设计公司。回顾半导体业界的高通,很多营业收入也来自于IP的收入。这个在相当长的时间内,对公司的总体收入来说是非常健康的模式,如果单纯靠项目,或者服务,自身成本会很高,同时受外来影响比较大。而IP一但在某个半导体厂被某个客户成功应用,接下来就可以给很多客户应用,属于一段时间内一劳永逸的事情。当然,在国内商业环境下,IP公司经常碰到很多壁垒,因为行业方面不是在市场选择对的,而是更多偏向于选择内部自己圈子的资源。所以,打造健康商业环境,短期来看对国外的IP公司有利,长期来看对国内更多设计公司是件好事情,因为他们有更多收入来支持科研开发,而不是面对抄袭,盗版让公司面临迅速衰落,生存的问题。

4. 质量体系和口碑:

在半导体产业界,口碑是一个企业的生命。Sofics 的客户遍布世界各地,服务于各大半导体厂和设计公司,覆盖了模拟设计,数字设计,汽车电子设计,硅光电,高频,高压等各个方面。

我们来看看来自客户们的评价,也许这个很好解释了Sofics 取得成功的真正原因:

eSiliconSofics: “delivered it in just two weeks” Sofics' PowerQubic technology offered a great solutionPowerQubic protects a 15V interface on a 0.18um high-voltage LDMOS chip2012: Sofics PowerQubic Technology Used by eSilicon to Protect High-Voltage Solar Panel IC from Electrical Overstress

Nvidia:Interface with legacy components in smartphones and tablets, such as SIM cards and memory cards.Sofics and ICsense came up with a solution that works at high voltages and provides good ESD protection.Enables off-chip interfaces (in 40nm and 28nm) of up to 3.6 volts.2012 press release with Nvidia and ICsense

RUAGESD: doctor gives clients access to our full range of expertise in identifying, diagnosing, and solving ESD and EOS (electrical overstress) problems quickly and definitively2012: Sofics ESDdoctor Debugging Improves ESD Protection on Rad-Hard Ics

ZMDI (now IDT):PowerQubic clamps were superior in the EMC test, as well as in parameters such as meeting flexible clamping voltage specifications.We selected Sofics to provide ESD/EOS protection for a new line of 0.18um devicesmeet our specifications, at a lower cost than building the clamps from scratch 2013: ZMDI Licenses Sofics PowerQubic ESD Clamps to Meet Automotive EMC Requirements on 0.18um 24V Chips

中国半导体产业如火如荼,每年都有很多新的企业加入,也许Sofics 的成功之路能给你带来一些提示,公司不在于大,在于有自己的核心价值,在于健康的商业模式,在于合适的切入点,那么你的公司离成功不远了。

-

半导体

+关注

关注

336文章

30051浏览量

259003 -

模拟设计

+关注

关注

1文章

57浏览量

18785 -

数字设计

+关注

关注

0文章

50浏览量

22750

发布评论请先 登录

ESD测试的详细解释

ESD和EOS失效模式介绍

传感器走向“AI on-chip”与低功耗集成化

Abrupt Junction Varactor Diode Chip skyworksinc

概伦电子芯片级HBM静电防护分析平台ESDi介绍

Diodes公司PCIe 6.0时钟缓冲器介绍

燕麦科技成功收购AxisTec公司67%股权

ESD二极管不导电原因分析及解决方案

集成电路电磁兼容性及应对措施相关分析(三)集成电路ESD 测试与分析

关于On-chip ESD 公司的成功之路分析和介绍

关于On-chip ESD 公司的成功之路分析和介绍

评论