SystemVerilog通用验证方法(UVM)是一种生成测试和检查结果以进行功能验证的有效方法,最适合用于块级IC或FPGA或其他“小型”系统。在UVM测试台中,大多数活动是通过编写序列来生

2021-04-09 16:09:11 3584

3584

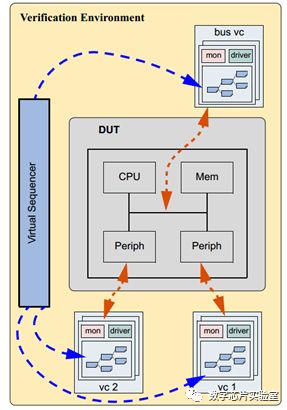

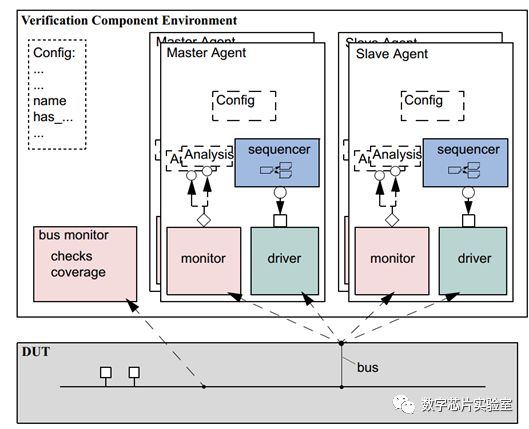

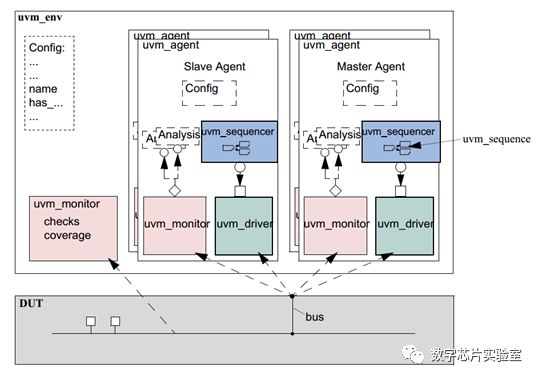

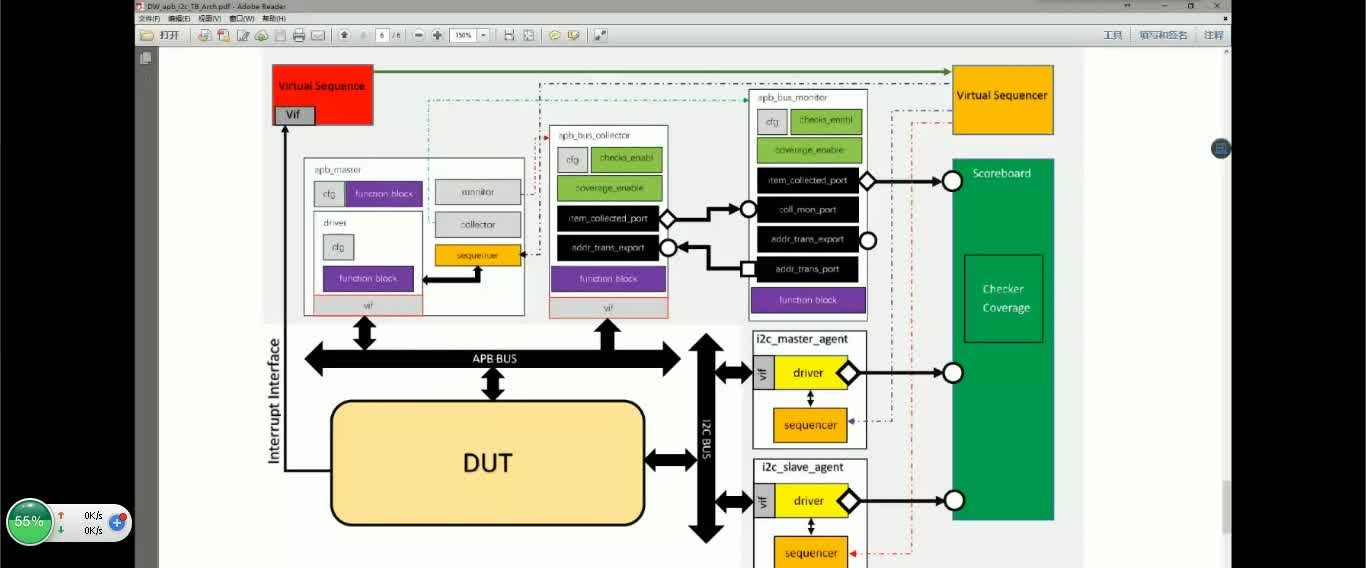

model)。一个简单的验证平台框图:在UVM中,引入了agent和sequence的概念,因此UVM中验证平台的典型框图长这样:通知:本章更新后在更新一篇《IC验证之UVM常用宏汇总(四)》将不

2020-12-02 15:21:34

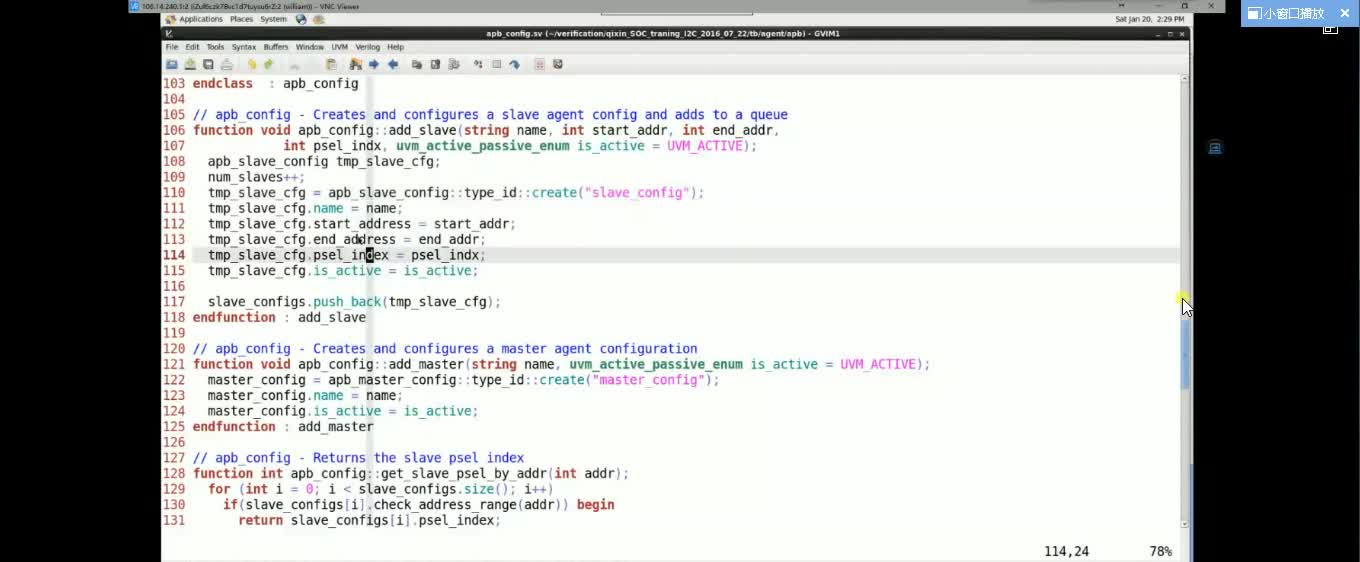

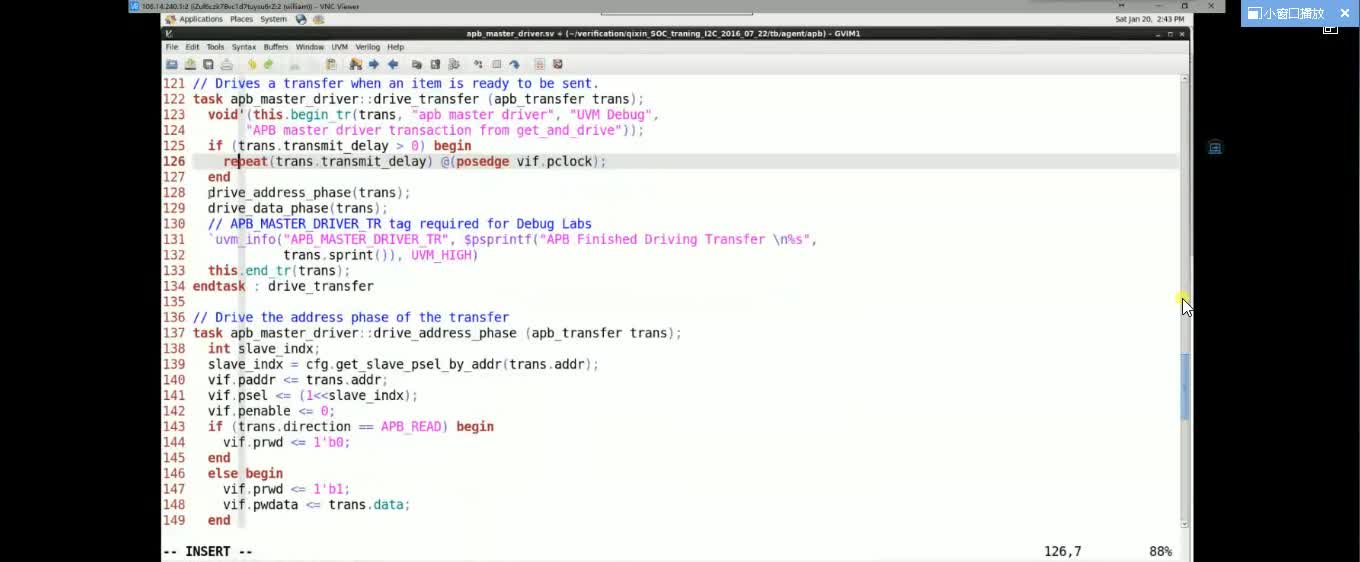

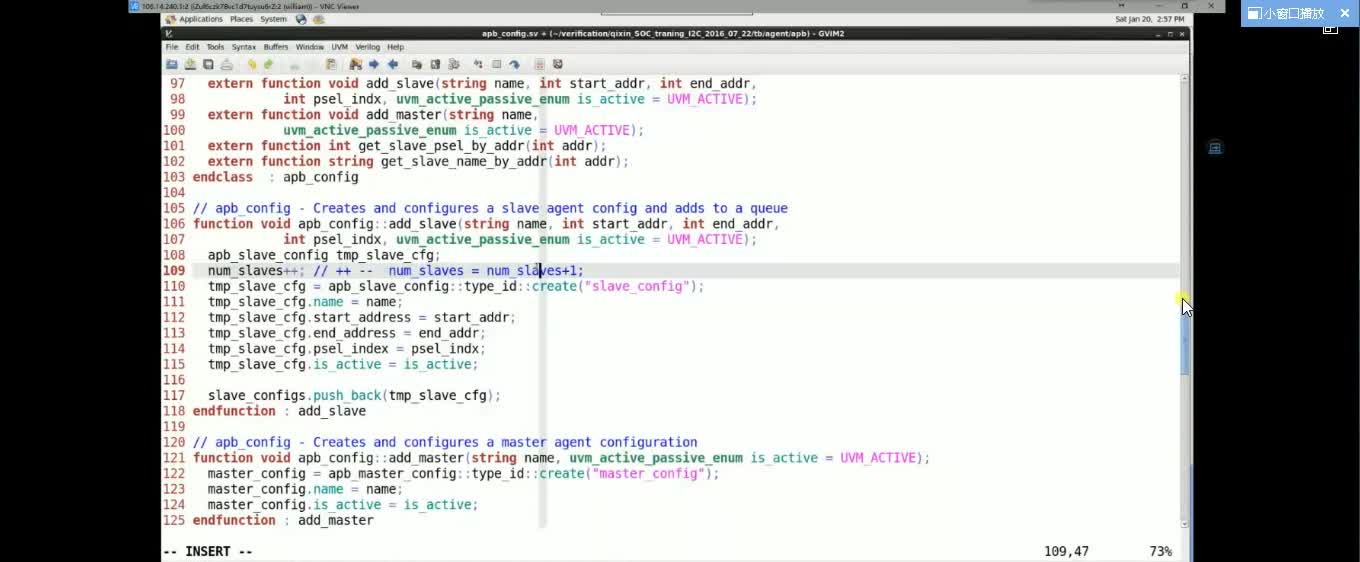

加入factory机制 上一节《IC验证"一个简单的UVM验证平台"是如何搭建的(五)》给出了一个只有driver、使用UVM搭建的验证平台。严格来说这根本就不算是UVM验证

2020-12-08 12:07:21

本帖最后由 IC那些事儿 于 2020-12-4 15:50 编辑

上次更新完《IC验证"UVM验证平台"组成》后本打算不再更新......但有人反映要继续更新...继续

2020-12-04 15:48:19

验证的基本常识,将会散落在各个章节之间。UVM的一些高级功能,如何灵活地使用sequence机制、factory机制等。如何编写代码才能保证可重用性。可重用性是目前IC界提及最多的几个词汇之一,它包含

2020-12-01 15:09:14

: +define+MACRO 或者: +define+MACRO=100扩展寄存器模型中的数据位宽:`define UVM_REG_DATA_WIDTH 128扩展寄存器模型中的地址位宽:`define

2020-12-02 15:24:35

在上一节中,**《IC验证"UVM验证平台加入factory机制"(六)》**虽然输出了“main_phase is called”,但是“data is drived”并没有

2020-12-09 18:28:15

有条理,我们要在验证计划当中明确要搭建什么样的验证平台,目前主流的验证平台有基于verilog的印证平台,基于systemverilog的验证平台,以及适用uvm方法学建立的验证平台,据uvm验证方法

2021-01-21 15:59:03

原文链接:https://zhuanlan.zhihu.com/p/345775995大家好,我是一哥,上章内容主要讲述两个内容,芯片验证以及验证计划。那本章我们主要讲述的内容有介绍什么是uvm

2021-01-21 16:00:16

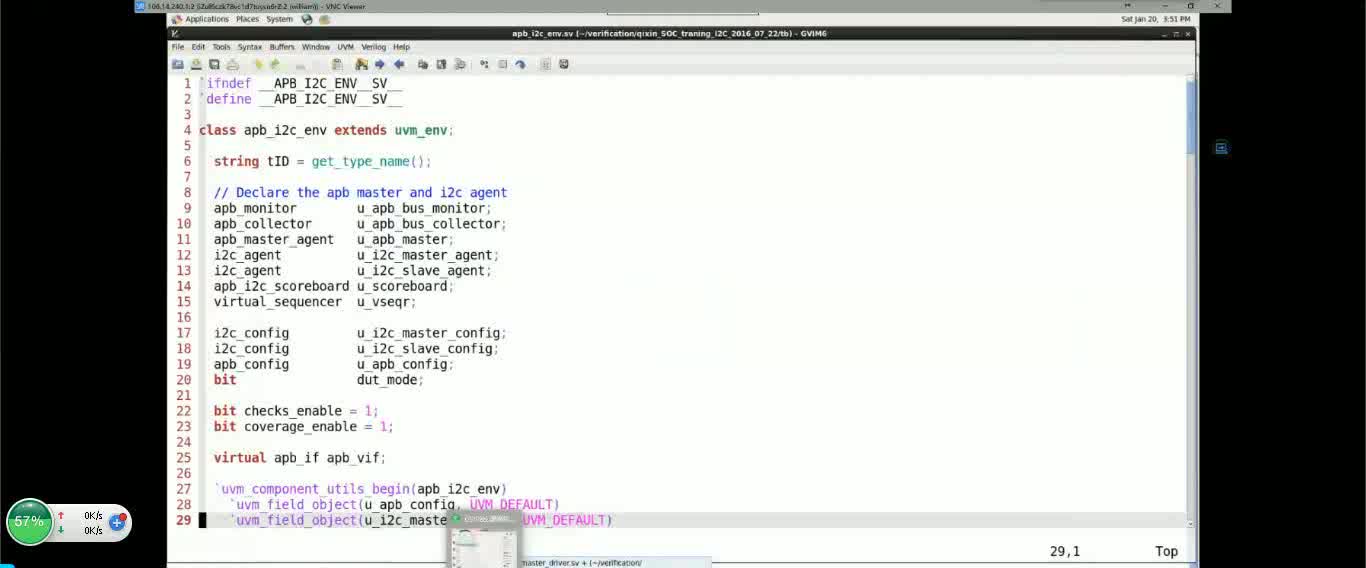

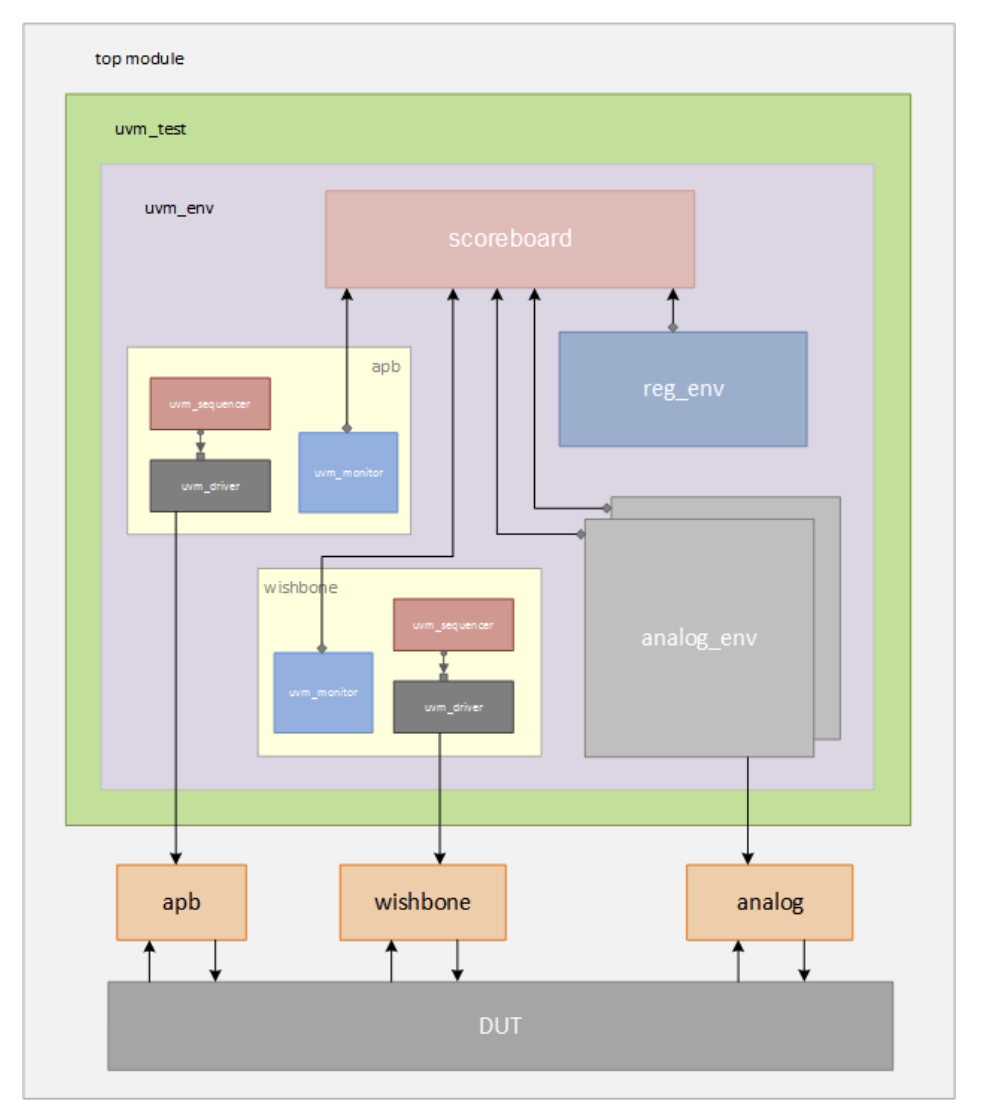

大家好,我是一哥,上章内容我们介绍什么是uvm?uvm的特点以及uvm为用户提供了哪些资源? 本章内容我们来看一看一个典型的uvm验证平台应该是什么样子的,来看一个典型的uvm测试平台的结构

2021-01-22 15:32:04

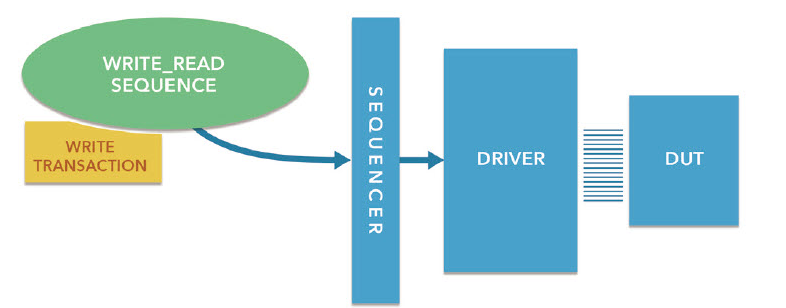

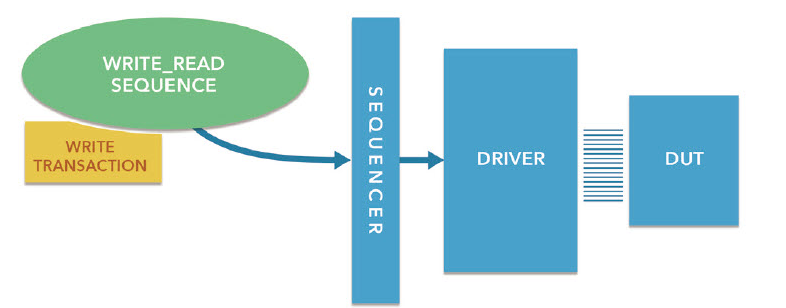

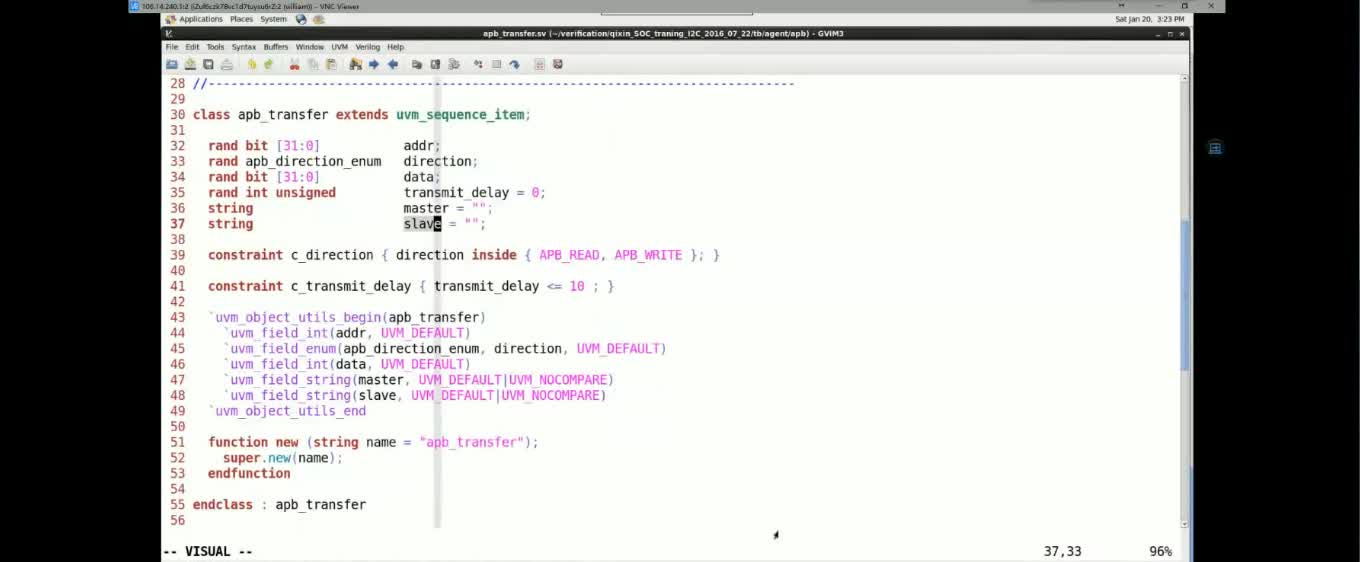

的transaction,以及创建用于产生事物的事物发生器sequence。 在uvm验证平台中穿梭各个组件之间的基本信息单元是一个被称为transaction的数据对象,也就是我们前面所说的事物

2021-01-26 10:05:37

大家好,我是一哥,上章一个典型的uvm验证平台应该是什么样子的?从本章开始就正式进入uvm知识的学习。先一步一步搭建一个简单的可运行的测试平台。 本章首先来介绍一下构成uvm测试平台的主要组件

2021-01-22 15:33:26

数字IC是什么意思?数字IC前端设计流程有哪些?数字IC后端设计流程有哪些?

2021-10-20 06:24:49

到非常高的位置。 那么哪里可以学习数字ic设计呢,可以参考了解(IC修真院),我学习过这个课程,包含数字前端设计、验证、后端设计等,从基础知识,理论知识,技术原理,架构设计,分析问题能力,从应用到知识点,应有全有,实战部分完全还原真实企业项目,是真正能提高实战应用能力的。

2020-12-04 14:31:30

验证方法简介 设计验证是用于证明设计正确性的过程,要求和规格。 在数字设计流程中,验证可确保芯片按照设计意图正确运行,然后再将设计送去制造。 具体来说,验证方法是验证集成电路设计的标准化方法。 验证

2022-02-13 17:03:49

& IP Core Verification)”卷。 本章介绍了 IC 和 IP 核设计过程验证中涉及的一些关键 Python 方法、工具、包和库,包括以下章节: 纯 Python

2022-11-03 13:07:24

海思成研无线部门高薪招聘数字IC设计/验证高级工程师,在这里您可以近距离接触业界最前沿的技术、最先进的工艺、最牛的设计和验证水平;在这里您跟FELLOW一起共事,享受浓厚的技术氛围;在这里您可感受到

2020-02-29 11:06:28

现阶段的IC行业,数字IC验证工程师非常紧缺,尤其是会UVM的验证工程师那更是奇货可居。但是最近和一些在校学生和刚入行的朋友们交流的时候,发现大多数人对数字IC验证工程师的具体工作不甚了解,甚至还

2017-05-17 12:50:39

UVM Report机制概述

2020-12-21 06:55:05

大家好,我是一哥,上章内容我们介绍什么是uvm?uvm的特点以及uvm为用户提供了哪些资源?本章内容我们来看一看一个典型的uvm验证平台应该是什么样子的,来看一个典型的uvm测试平台的结构。我们一个

2022-02-14 06:46:33

招聘岗位:芯片设计数字,验证工程师岗位要求:1.本科及以上学历,2年半以上工作经验2.精通verilog,SV等语言3.有端到端项目的交付经验4.精通VMM/UVM验证方法学5.具备团队合作意识,责任心强联系方式:***简历投递邮箱:lzdnewmail@163.com

2017-10-09 19:47:57

Systemverilog [1]和 UVM [2]为验证团队提供结构和规则。它使得在许多测试中能获得一致的结果,并可以在团队之间共享验证。许多验证团队都在使用由C代码编写的验证套件。本文将讨论将基于C的测试和验证套件集成到常规UVM测试平台的各种方法。

2020-12-11 07:59:44

Systemverilog [1]和 UVM [2]为验证团队提供结构和规则。它使得在许多测试中能获得一致的结果,并可以在团队之间共享验证。许多验证团队都在使用由C代码编写的验证套件。本文将讨论将基于C的测试和验证套件集成到常规UVM测试平台的各种方法。

2020-12-15 07:38:34

请教各位大佬,UVM是基于sv的验证方法学,如果采用systemc语言编程,如何实现?

2019-11-07 15:30:16

),通常也叫寄存器模型,顾名思义就是对寄存器这个部件的建模。本文要介绍的内容,包括对UVM寄存器模型的概述,如何构建寄存器模型,以及如何将寄存器模型集成到验证环境中。篇幅原因,将在下一篇文章再给出寄存器

2022-09-23 14:29:03

的物理验证工作;3、按时汇报和推进项目进度。数字IC设计-深圳 上海 成都 杭州 苏州 武汉 岗位要求:1、精通数字电路设计,熟练掌握Verilog,具有良好的编程风格;2、熟悉ARM Cortex-M

2018-08-02 16:18:53

新手学习SystemVerilog & UVM指南 从刚接触System Verilog以及后来的VMM,OVM,UVM已经有很多年了,随着电子工业的逐步发展,国内对验证人才的需求也会急剧

2015-03-11 16:24:35

也买了一个大衣柜,专门用来放她的成堆的衣服、鞋包。” Chapter5. virtual\_sequencer/virtual\_sequence 曾经有位验证者说过,UVM定义的virtual

2023-04-04 17:20:51

硬件验证方法简明介绍本书“硬件验证方法简明介绍”是“半导体 IP 核——不仅仅是设计”系列丛书中“验证 IP 和 IP 核验证”的一部分。本书调查、处理和介绍了 IC 验证中涉及的一些关键方法、工具

2022-11-26 20:43:20

猎头职位:IC验证工程师【北京】岗位职责:1.根据芯片架构文档和设计要点,制定验证方案,拟定验证计划;2.根据验证方案和计划,实施验证,包括编写参考模型、搭建仿真验证平台与迭代改进、编写完备的验证

2017-02-15 13:39:33

。往往我们在书写测试用例或者sequences的时候会有查询验证平台组件uvm_component的需求,比如env/driver/monitor。由于sequences不是测试平台层次结构的一部分,实现

2022-04-11 16:43:42

下uvm_info的三个参数。 ID是作为message的标记(tag)。 MSG就是真正要打印的message文本。 VERBOSITY用于传递uvm\_verbosity枚举类型的数字。当

2023-03-17 16:41:28

全球电子设计创新领先企业Cadence设计系统公司,今天宣布了业界最全面的用于系统级芯片(SoC)验证的通用验证方法学(UVM)开源参考流程。为了配合Cadence EDA360中SoC实现能力的策略,

2010-06-28 08:29:14 2240

2240 基于UVM的CPU卡芯片验证平台_钱一文

2017-01-07 19:00:39 4

4 基于UVM的验证平台设计研究_王国军

2017-01-07 19:00:39 4

4 基于UVM的CAN模块自验证方法_熊涛

2017-01-08 14:47:53 3

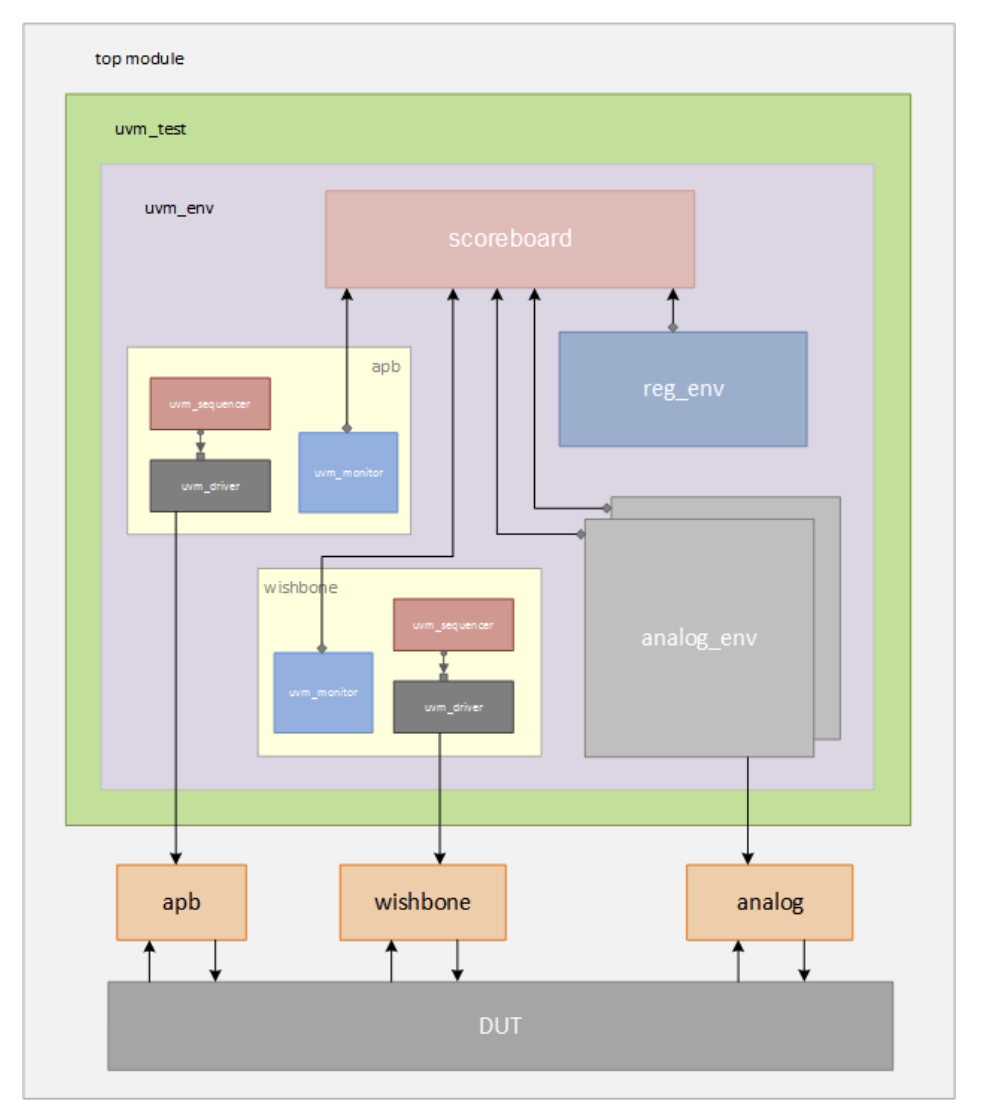

3 一种基于UVM的混合信号验证环境_耿睿

2017-01-07 21:39:44 1

1 UVM使得验证测试平台的结构得以标准化,各种复用策略及标准对于提高验证质量、缩短项目周期都非常有效。垂直重用是常见的复用策略之一,即同一项目测试平台复用于不同验证层次。验证中常将最底层的IP级验证平台向更高的集成层复用,而UVM寄存器模型则是验证平台复用的一个关键部分。

2017-09-15 11:49:08 15

15 的连接、驱动器、监视器、仿真序列以及功能覆盖率的建立。 本文呈现出了一种使用UVM验证方法学构建基于高可配置性的高级微处理器总线架构(AMBA)的IP验证环境,其中会使用到Synopsys公司的AMBA VIP和Ruby脚本。该验证环境可以支持通过使用AMBA设计参数进行自

2017-09-15 14:37:34 6

6 UVM已经成为了一种高效率的、从模块级到系统级完整验证环境开发标准,其中一个关键的原则是UVM可以开发出可重用的验证组件。获得重用动力的一个方面表现为标准的仿真器和硬件加速之间的验证组件和环境的复用

2017-09-15 17:08:11 14

14 毋庸置疑,UVM大大提高了我们开发验证平台的效率。但同时,熟练掌握UVM搭建验证平台也并不是一件容易的事情。同时由于不同验证工程师搭建环境的风格不太一致,所以在一个项目中常会出现不好管理,甚至前后

2017-09-15 17:18:01 22

22 当我们验证片上系统(SoC)嵌入了具有多个数字外设的微处理器以及可能的模拟模块时,我们希望检查所有实现的功能和可能的极端情况,以最大限度地缩短验证时间。多种技术和方法的混合用于改进功能验证并提取覆盖

2019-08-09 15:25:34 6862

6862

近几十年来,集成电路事业发展迅速,设计与工艺技术不断发展,更多和更复杂的功能被集成到一块芯片上。SoC的集成度和复杂度大大提高,在IC设计中就容易引入错误,所以验证工作将变得艰巨。随着IC设计规模

2020-01-27 17:21:00 6132

6132

Wilson Research Group 的一项最近研究发现,48% 的 FPGA 设计项目和 71% 的 ASIC设计项目依赖 UVM 进行设计验证。

2020-03-02 18:12:24 1019

1019 本章第一节将大体介绍一下感性意义上的UVM,这里不会讲的很详细,因为关于UVM的历史在网上已经有太多的资料第二节讲述验证平台的组成,这里也只是介绍一个轮廓。第三节开始则会教我们一步一步搭建一个UVM

2020-07-01 08:00:00 69

69 尽管本指南提供了一组说明,以执行一个或多个特定的验证任务,但应 以教育,经验和专业判断为补充。 并非本指南的所有方面都可能 适用于所有情况。 《 UVM 1.1用户指南》不一定代表标准 必须谨慎判断给定的专业服务是否足够,也不应以此文件为依据 应用时无需考虑项目的独特方面。

2021-03-29 10:41:32 21

21 数字IC就是传递、加工、处理数字信号的IC,是近年来应用最广、发展最快的IC品种,可分为通用数字IC和专用数字IC。数字前端以设计架构为起点,以生成可以布局布线的网表为终点;是用设计的电路实现想法

2021-11-06 16:51:05 26

26 大家好,我是一哥,上章内容我们介绍什么是uvm?uvm的特点以及uvm为用户提供了哪些资源?本章内容我们来看一看一个典型的uvm验证平台应该是什么样子的,来看一个典型的uvm测试平台的结构。我们

2021-12-09 13:36:13 7

7 利用Systemverilog+UVM搭建soc验证环境

2022-08-08 14:35:05 5

5 百度百科对UVM的释义如下:通用验证方法学(Universal Verification Methodology, UVM)是一个以SystemVerilog类库为主体的验证平台开发框架,验证工程师可以利用其可重用组件构建具有标准化层次结构和接口的功能验证环境。

2022-11-30 12:47:00 1060

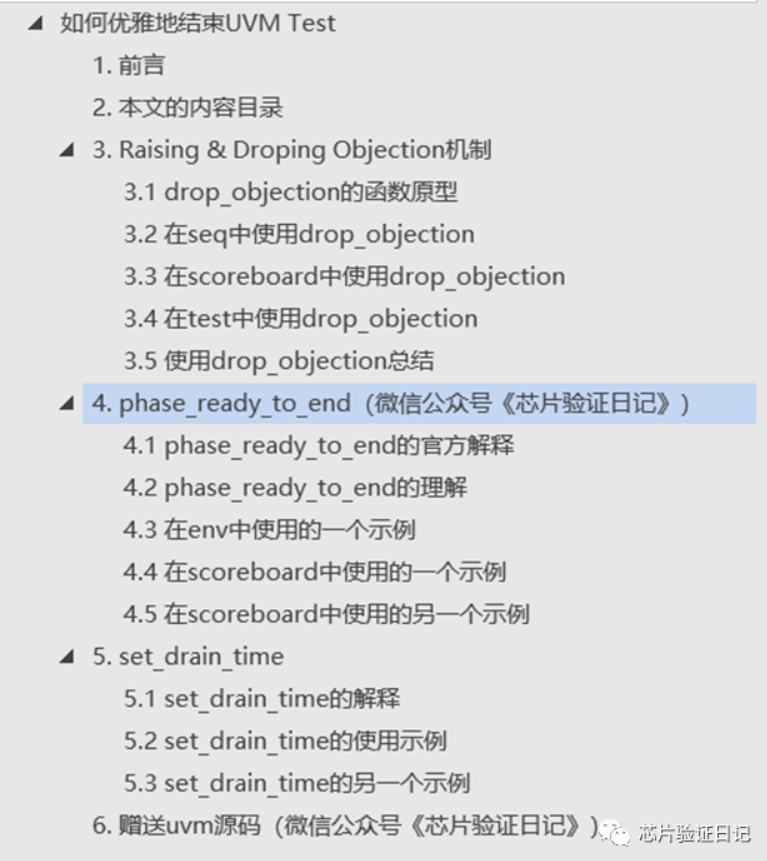

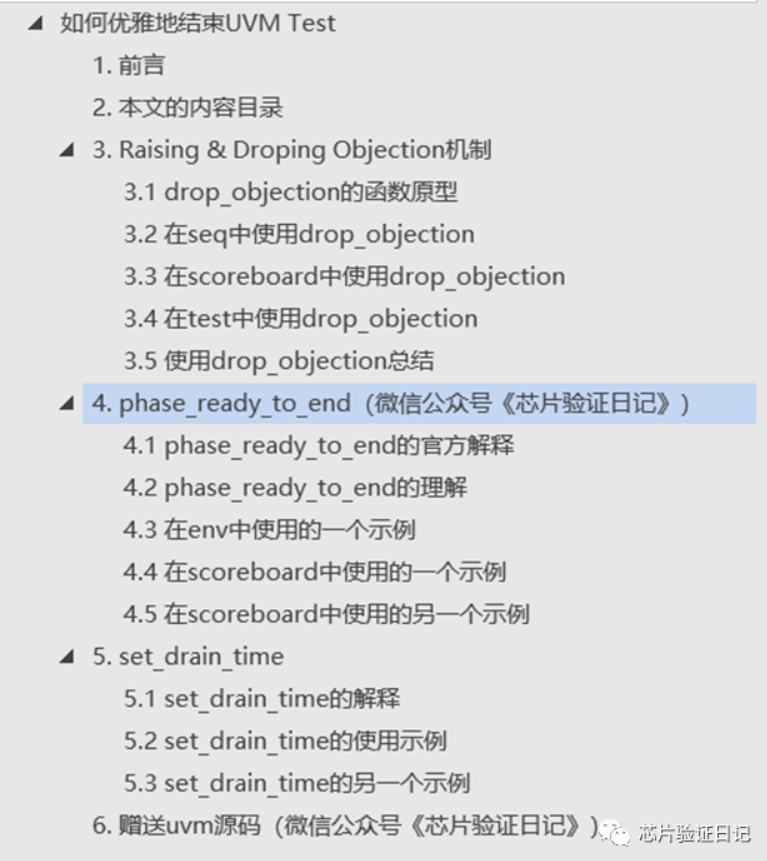

1060 分享一下在UVM验证环境中,结束仿真的几种方式,不同结束仿真的方式适合不同的应用场景。

2022-12-17 11:23:54 1702

1702

因为DUT是一个静态的内容,所以testbench理应也是静态的,其作为uvm验证环境和DUT的全局根结点。

2023-03-21 11:33:02 982

982 UVM environment**包含多个可重用的验证组件,并根据test case的需求进行相应的配置。例如,UVM environment可能具有多个agent(对应不同的interface)、scoreboard、functional coverage collector和一些checker

2023-03-21 11:35:25 744

744

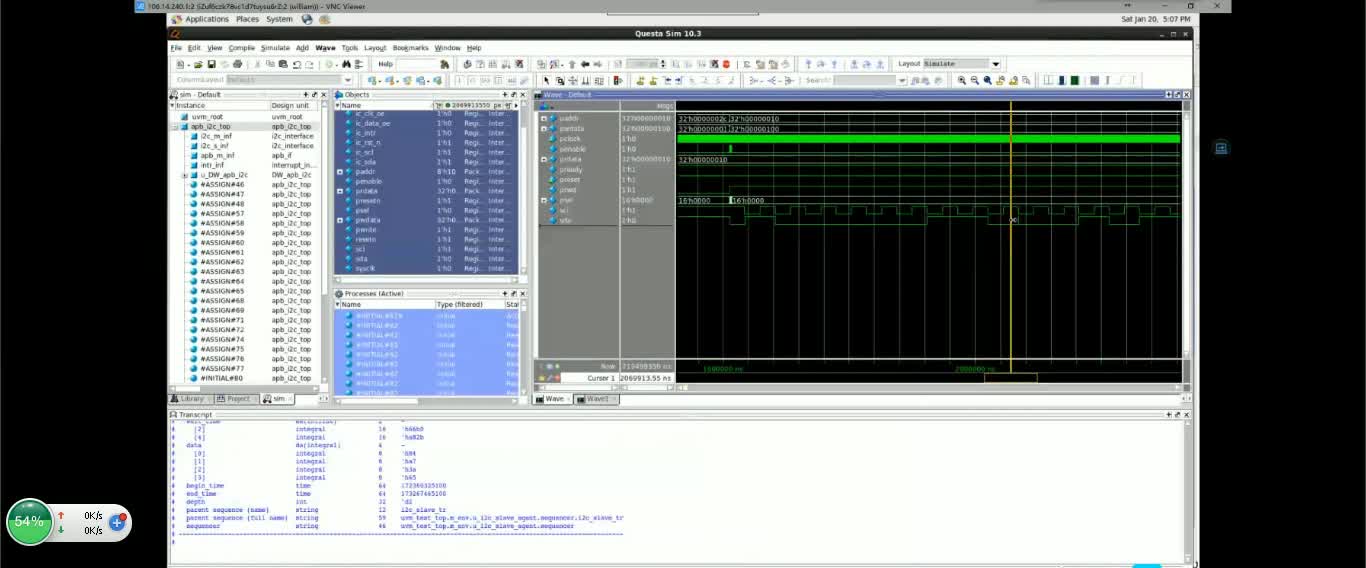

基于UVM搭建验证环境和构造验证激励,调试的工作总是绕不开的。实际上,对验证环境和激励的调试,往往伴随着验证阶段的前半程,并且会花掉验证工程师很多时间和精力。

2023-04-06 09:36:03 428

428 IC设计和IC验证都是非常重要的环节,一个好的IC产品需要二者的配合。IC设计是在满足产品规格书的前提下,实现电路性能、功耗、面积等方面的优化,从而满足设计需求的过程。而IC验证是在设计完成后,必须对所设计的芯片进行正确性、可靠性、功耗等方面的验证。

2023-04-12 14:01:33 2603

2603 IC设计和IC验证都是非常重要的环节,一个好的IC产品需要二者的配合。IC设计是在满足产品规格书的前提下,实现电路性能、功耗、面积等方面的优化,从而满足设计需求的过程。而IC验证是在设计完成后,必须对所设计的芯片进行正确性、可靠性、功耗等方面的验证。

2023-04-13 17:50:50 4535

4535 话说螺蛳壳里做道场,UVM推出这么多年以来每年DVCon会议上总还是有人分享他们基于UVM package做的一些改动,使其能够更适合项目的要求。

2023-04-13 18:13:09 1207

1207 在UVM中,transaction 是一个类对象,它包含了建模两个验证组件之间的通信所需的任何信息。

2023-05-24 09:17:32 1165

1165

driver应该派生自uvm_driver,而uvm_driver派生自uvm_component。

2023-05-26 14:38:46 823

823

如下图所示,UVM中的TLM接口为组件之间Transaction的发送和接收提供了一套统一的通信方法。

2023-05-29 09:31:44 340

340

本文使用Easier UVM Code Generator生成包含多个agent和interface的uvm验证环境。

2023-06-06 09:13:02 584

584 有的认为验证业务方向很重要,有的认为验证思维更重要,有的认为验证的通用代码能力SV+UVM更重要。

2023-06-25 09:47:12 279

279 提高验证生产力的关键之一就是在合适的**抽象层次**思考问题和完成验证工作,为此UVM提供了 **事务级别(transaction level)** 的通信接口 **(Transaction-Level Modeling,TLM)** 。

2023-06-25 11:42:11 288

288

IC验证,即集成电路验证(Integrated Circuit Verification),是指针对硬件设计中的集成电路(IC)进行的一系列功能验证、性能验证和正确性验证的过程。它是电子设计自动化(EDA)领域中非常重要的环节,用于确保设计的集成电路在实际生产中能够正常运行。

2023-07-24 15:45:18 2094

2094 本篇是对UVM设计模式 ( 二 ) 参数化类、静态变量/方法/类、单例模式、UVM_ROOT、工厂模式、UVM_FACTORY[1]中单例模式的补充,分析静态类的使用,UVM中资源池的实现,uvm_config_db的使用。

2023-08-06 10:38:41 825

825

FPGA验证和UVM验证在芯片设计和验证过程中都扮演着重要的角色,但它们之间存在明显的区别。

2024-03-15 15:00:41 94

94

电子发烧友App

电子发烧友App

评论