1. 前言

众所周知,在传统的测试平台中,通常在完成复位、配置、数据传输和自动检查等所有步骤后,通过调用verilog的系统函数$finish来结束仿真。

但相对于传统的测试平台,UVM在Testbench架构的几乎每个方面都做了创新,当然结束仿真的控制也发生了很大变化。在UVM验证环境中结束仿真最常用的就是drop_objection机制,当然所有phase都结束后,还是调用系统函数$finish来结束仿真。

下面,分享一下在UVM验证环境中,结束仿真的几种方式,这些结束方式,适用于不同的应用场景。我的表达能力不强,大家重点看代码。

2. 本文的内容目录

3. Raising & Droping Objection机制

3.1 drop_objection的函数原型

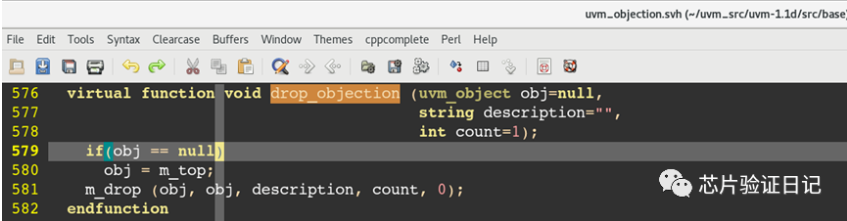

下图是uvm1.1d源码中关于drop_objection函数的定义,如下图所示。

3.2 在seq中使用drop_objection

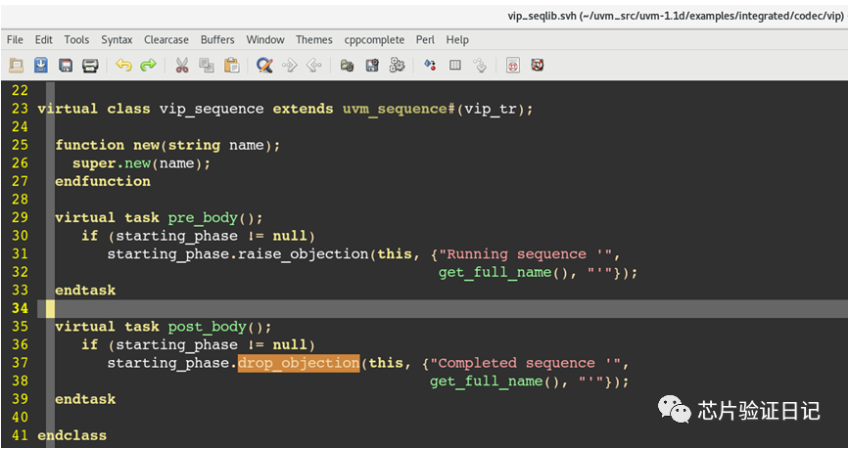

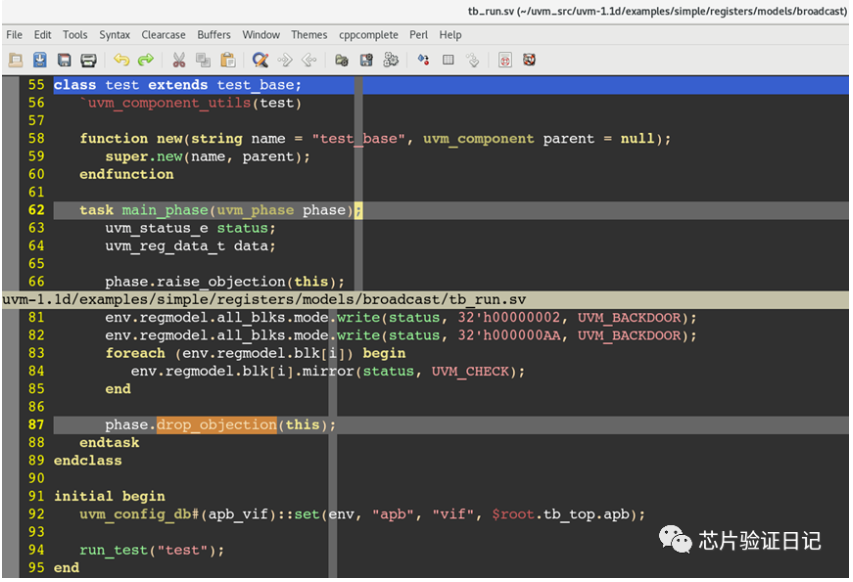

下图是在sequence中调用drop_objection的示例,如下图所示,同样来自于uvm源码。

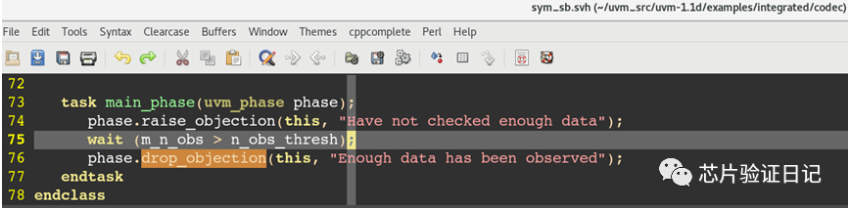

3.3 在scoreboard中使用drop_objection

3.4 在test中使用drop_objection

3.5 使用drop_objection总结

结合上面的例子,强调两点:

一是:drop_objection可以用在任何一个component中;当然也可以用在sequence中,但不可以用在其他uvm_object类里面,因为uvm_object里面没有phase的概念,那sequence其实也没有phase的概念,为什么可以?这也是一个小知识点,有的面试官问的仔细了,也可能问到,我就不展开了。

二是:在实际项目中的整个验证环境中,最好只用一对raise_objection/drop_objection,不要在很多组件中都使用它,否则很容易造成死锁,而且很难debug,尽管uvm的语法也允许这么做。

4. phase_ready_to_end(微信公众号《芯片验证日记》)

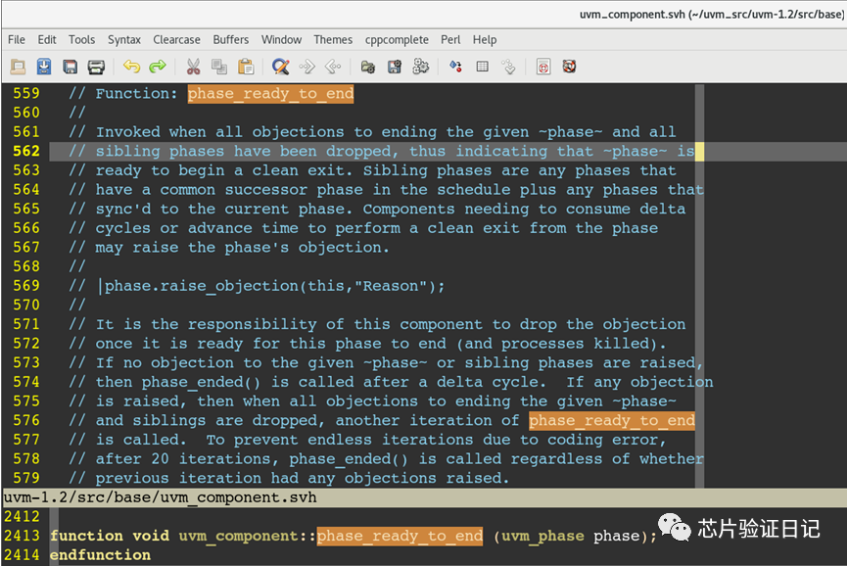

4.1 phase_ready_to_end的官方解释

4.2 phase_ready_to_end的理解

phase_ready_to_end(uvm_phase phase)是组件类的回调方法(函数),当相应phase的所有objection均被放下并且该phase将要结束时,会调用该方法。组件类可以使用此回调方法来定义phase即将结束时需要执行的任何功能。例如,如果某个组件希望将phase结束延迟到某个条件,甚至在所有objections均被放下之后,也可以使用此回调方法来完成。再比如,如果一个激励或应答sequence正在运行,在主sequence结束之前,则可以使用main_phase()中的phase_ready_to_end()回调方法来停止那些激励或应答sequence。再比如一个component想要延迟某个run-time phase的生命周期,那么可以在所有的objection都被dropped之后使用这个回调方法。

对于sequences, tests和许多完整的测试平台,在phase的正常寿命期间phase objections的提起和撤销是足够的。但是,有时某个组件不希望在phase的正常生命周期内主动提起和撤销objections,但确实希望延迟从一个phase到下一类phase的过渡。这在事务中经常出现这种情况,出于性能原因,不能针对每笔事务提出objection,并且通常情况下是端到端的记分板。为了在所有其他组件同意该phase应该结束之后延迟phase结束,该组件应该在phase_ready_to_end方法中提出objections。然后它负责在组件的主体中或在phase_ready_end_method的任务fork / join none中撤销这些objections。

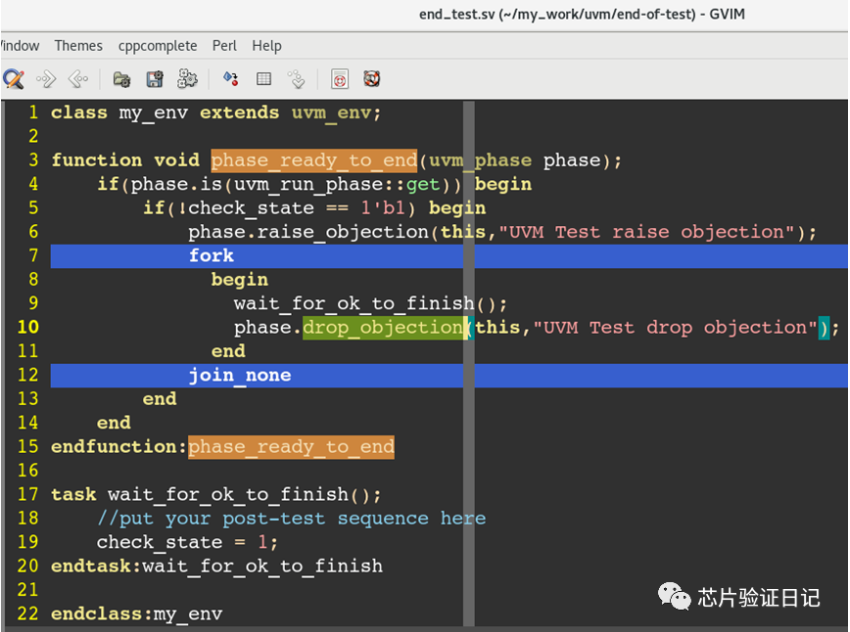

4.3 在env中使用的一个示例

注意,phase_ready_to_end是一个function,但用fork/join_none将wait_for_ok_to_finish和drop_objection进行了处理,这允许function立即返回。

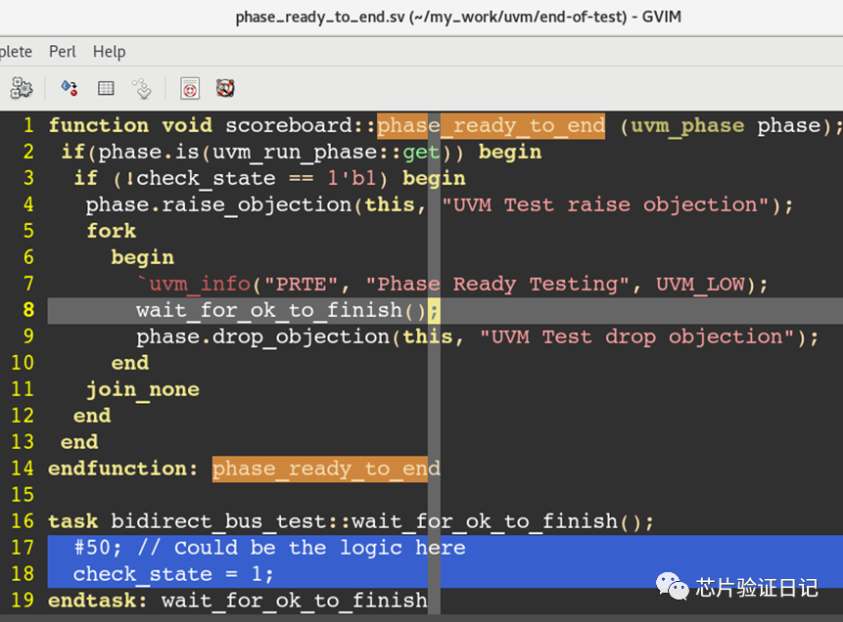

4.4 在scoreboard中使用的一个示例

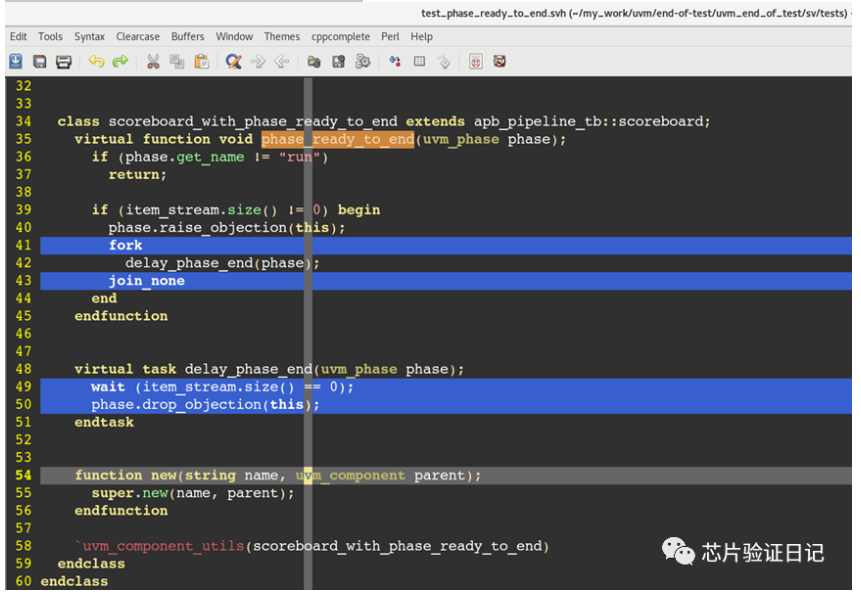

4.5 在scoreboard中使用的另一个示例

5. set_drain_time

5.1 set_drain_time的解释

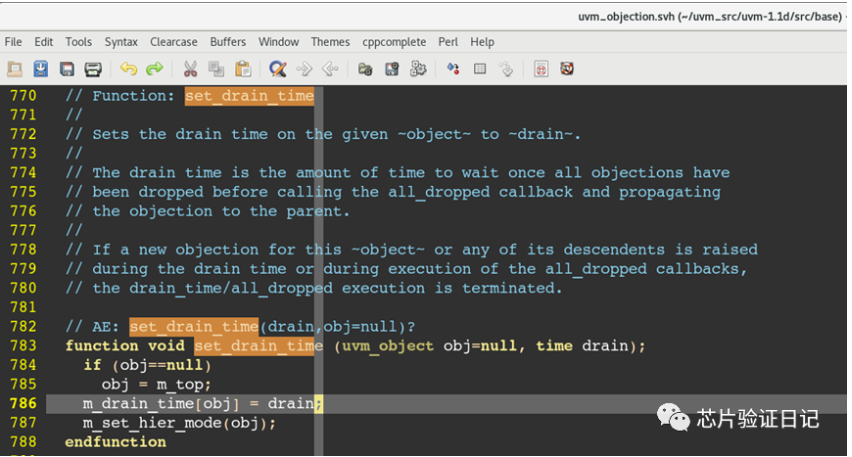

下图是官方对set_drain_time的解释,以及函数原型的定义。

5.2 set_drain_time的使用示例

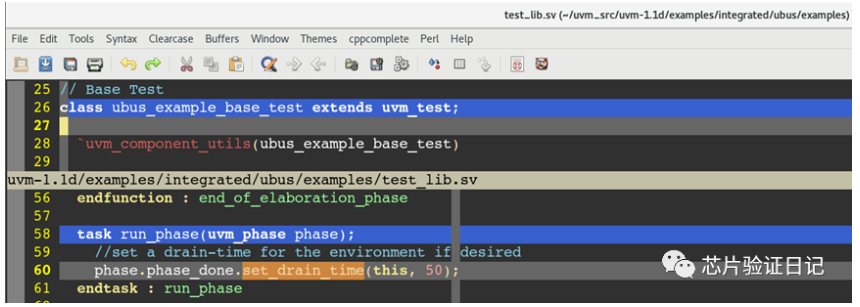

set_drain_time的使用方法,同样来自最权威的source code.

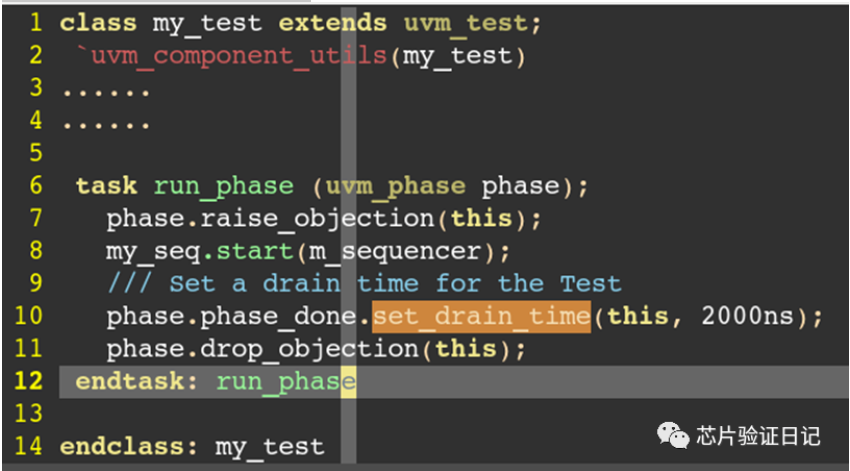

5.3 set_drain_time的另一个示例

写文章不易,如果觉得对您有帮助,麻烦一键三连,或者赏个鸡腿也行!

审核编辑 黄昊宇

-

UVM

+关注

关注

0文章

183浏览量

19942

发布评论请先 登录

IC验证“UVM验证平台加入objection机制和virtual interface机制“(七)

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

什么是uvm?uvm的特点有哪些呢

谈谈UVM中的uvm_info打印

UVM中seq.start()和default_sequence执行顺序

我的第一个UVM代码——Hello world

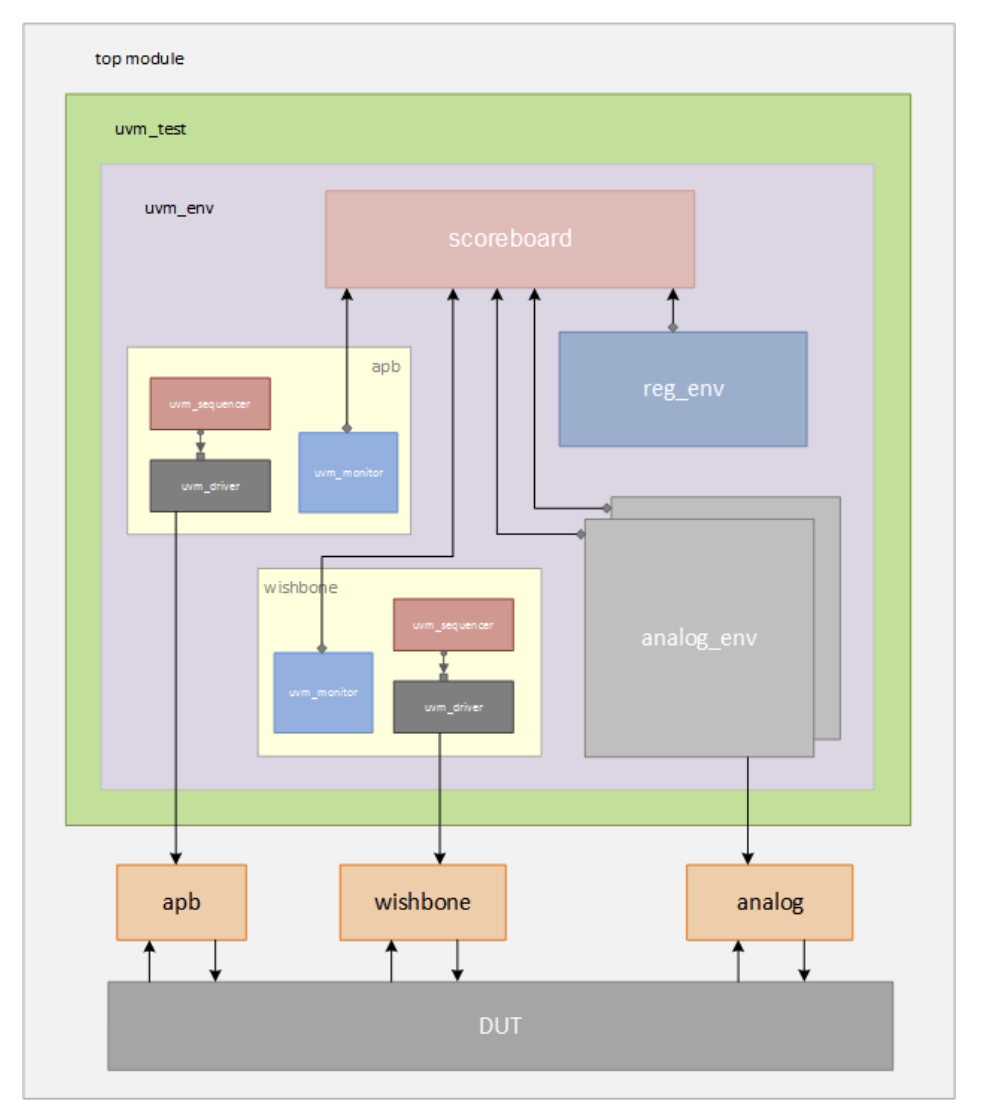

什么是UVM environment?

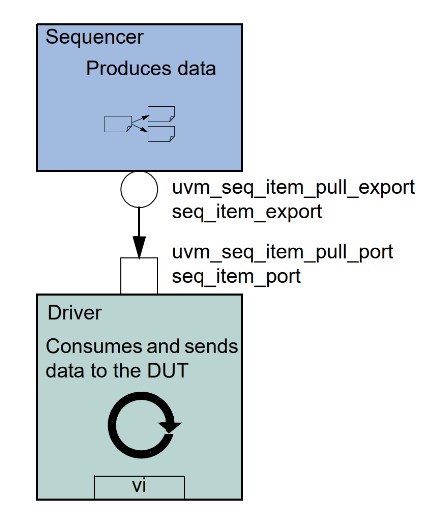

UVM driver和sequencer的通信

聊一聊所谓的Objection机制

管理test case结束机制介绍

UVM中uvm_config_db机制背后的大功臣

UVM中uvm_config_db机制背后的大功臣

一文详解UVM设计模式

如何优雅地结束UVM Test

如何优雅地结束UVM Test

评论