report_cdc 可以报告设计中所有的 cdc 路径并将其分类(前提是时钟被约束好),我们可以基于该报告来检查设计中是否有不安全的 cdc 路径。

2022-11-28 10:53:13 1000

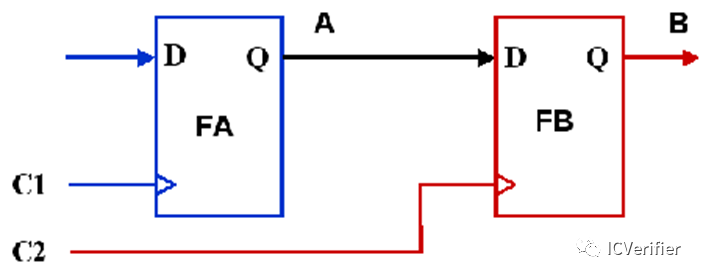

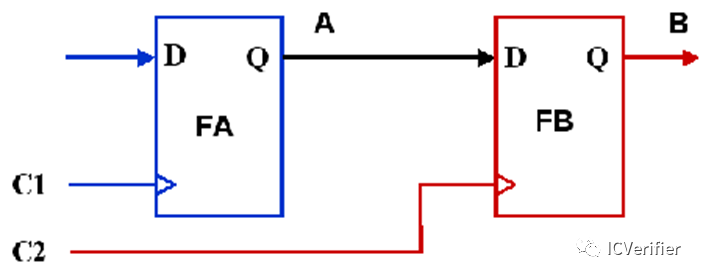

1000 跨时钟域( **Clock Domain Crossing,CDC** )通俗地讲,就是 **模块之间数据交互时用的不是同一个时钟进行驱动** ,如下图所示:左边的模块FA由C1驱动,属于C1时钟域;右边的模块FB由C2驱动,属于C2时钟域。

2023-09-20 11:24:37 1407

1407

嗨,我有一个4时钟域的原始设计。在添加第5个时钟域并将设计加载到芯片中后,该设计在硬件中不再起作用。我正在使用斯巴达3E 1600这是一个很大的设计,但作为一个例子,我有一个简单的计数器,如下所示

2019-06-17 14:32:33

CDC典型错误案例一、主要概念**同步逻辑和异步逻辑:**时钟域为由单个时钟或具有固定相位关系的时钟驱动的设计部分。也就是说,在一个模块中一个时钟和他的翻转或者分频时钟认为是相同的时钟域,其所驱动

2021-07-26 07:03:57

throughFIFO,它正在写入550 MHz的信号,而这个信号我正在150 MHz clk上读取。我已经定义了时序约束,当我进行综合时,时序失败,路径显示在CDC fifo中。任何人都可以提出建议,以便我的时间不会

2019-03-11 11:05:55

文章目录前言时钟及时钟域时钟,时序逻辑的心跳时钟信...

2021-07-29 07:43:44

bq1_dat稳定在1,bq2_dat也输出稳定的1。最后,从特权同学的经验和实践的角度聊一下。跨时钟域的信号同步到底需要1级还是2级,完全取决于具体的应用。如果设计中这类跨时钟域信号特别多,增加1级

2020-08-20 11:32:06

解释了什么时候要用到FALSE PATH: 1.从逻辑上考虑,与电路正常工作不相关的那些路径,比如测试逻辑,静态或准静态逻辑。 2. 从时序上考虑,我们在综合时不需要分析的那些路径,比如跨越异步时钟域

2018-07-03 11:59:59

(10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 07:47:50

的数据(多bit)。在这种类似的场景中,我们便可以使用异步双口RAM来做跨时钟域处理。先利用ADC芯片提供的60MHz时钟将ADC 输出的数据写入异步双口RAM,然后使用100MHz的时钟从RAM中读出

2021-03-04 09:22:51

FPGA设计中有多个时钟域时如何处理?跨时钟域的基本设计方法是:(1)对于单个信号,使用双D触发器在不同时钟域间同步。来源于时钟域1的信号对于时钟域2来说是一个异步信号。异步信号进入时钟域2后,首先

2012-02-24 15:47:57

[size=11.818181991577148px]FPGA开发中,遇到的最多的就是异步时钟域了。[size=11.818181991577148px]检查初学者的代码,发现最多的就是这类

2014-08-13 15:36:55

时钟,并且需要处理跨时钟域问题(在视频应用中尤其常见)。这意味着我们有一个复杂的时钟环境——一个很容易出现时钟错误的环境。这将导致时序很难收敛或更产生糟糕的情况,例如引入无意的时钟域交叉错误,从而导致

2022-10-08 15:28:35

评论一些或所有问题。策略1:CDC使用异步FIFO基本上整个串行接收系统(FSM +串行移位寄存器)在“外部时钟域”中实现。双域FIFO负责时钟域交叉。Q1:在我的应用程序中,EXT_CLK可以以

2019-04-28 12:39:33

1、IC设计中的多时钟域处理方法简析我们在ASIC或FPGA系统设计中,常常会遇到需要在多个时钟域下交互传输的问题,时序问题也随着系统越复杂而变得更为严重。跨时钟域处理技术是IC设计中非常重要的一个

2022-06-24 16:54:26

本人小菜鸟,刚开始接触Labview,想知道Labview用在通信物理层可以做那些事,可以实现那些功能,还望各位大神不吝赐教!

2012-10-31 15:35:41

的特色之一,但MDO4000 绝不是以上罗列的五种测试工具的简单组合,这五种功能工作在同一时钟、同一触发机制下,使得MDO4000 具有创新的时域、频域、调制域时间相关的跨域分析功能。为此,我们将

2019-07-19 07:02:07

用文章着重介绍MDO4000 在以上应用中的调制域分析,但应时刻牢记MDO4000 本质的特色—跨域分析,即MDO4000在进行调制域分析的同时可以进行跨域分析,解决传统手段难以发现的问题。

2019-07-19 06:43:08

在 PCB 设计过程中,由于平面的分割,可能会导致信号参考平面不连续,对于低低频信号,可能没什么关系,而在高频数字系统中,高频信号以参考平面作返回路径,即回流路径,如果参考ᒣ面不连续,信号跨分割

2016-10-09 13:10:37

中,很久没有听到有人提起一个关键的组件——检波器,作为在业界无线系统中的RF和IF信号检测应用广泛的高性能RF检波器提供商,ADI专家最近的一场技术讲座对这个无线设计中“原始”而重要的器件的一场分享,让笔者有机会明白对RF检波器那些事到底知道多少?

2019-07-31 07:14:15

为什么MCU会具有看门狗呢?带着这个疑问,来了解看门狗的那些事。就连51单片机都带有看门狗,说明这条狗对我们来说有着不一般的意义。看门狗的目的一句话说:防止程序乱跑。MCU在不同的环境下程序的运行

2021-08-02 06:18:41

嗨,我试图使用Harmony 1_06_02中的应用程序示例cdc_com_port_.(pic32mz_ec_sk_int_.),其时钟低于200Mhz。我使用的是PIC32 MZ EC启动器套件

2019-09-11 14:16:30

如何克服ajax跨域

2020-04-30 13:25:07

于pH计和电导率仪那些事,好资料一起分享,问题向咱们的专家发问一起探讨哦,,俺们会第一时间将问题抛给最资深的专家滴。。。哈哈~~~

2018-11-05 09:14:54

双口RAM如何实现跨时钟域通信啊?怎么在quartus ii仿真???

2017-05-02 21:51:39

`“工业品那些事”征稿啦! 您可以是采购、工程师、销售、老师、学生,只要你有足够的热情,极客的关注,专业的知识,那么欢迎您和我们说说工业品那些事儿! 我们需要:介绍“工业品”相关文章,题材不限

2015-02-09 17:37:25

`“工业品那些事”征稿啦! 您可以是采购、工程师、销售、老师、学生,只要你有足够的热情,极客的关注,专业的知识,那么欢迎您和我们说说工业品那些事儿! 我们需要:介绍“工业品”相关文章,题材不限

2015-02-10 10:52:14

跨越时钟域FPGA设计中可以使用多个时钟。每个时钟形成一个FPGA内部时钟域“,如果需要在另一个时钟域的时钟域产生一个信号,需要特别小心。隧道四部分第1部分:过路处。第2部分:道口标志第3部分:穿越

2012-03-19 15:16:20

60MHz的时钟上升沿变化,而FPGA内部需要使用100MHz的时钟来处理ADC采集到的数据(多bit)。在这种类似的场景中,我们便可以使用异步双口RAM来做跨时钟域处理。 先利用ADC芯片提供的60MHz

2021-01-08 16:55:23

的数据(多bit)。在这种类似的场景中,我们便可以使用异步双口RAM来做跨时钟域处理。先利用ADC芯片提供的60MHz时钟将ADC 输出的数据写入异步双口RAM,然后使用100MHz的时钟从RAM中读出

2021-02-21 07:00:00

异步bus交互(一)— 两级DFF同步器跨时钟域处理 & 亚稳态处理1.问题产生现在的芯片(比如SOC,片上系统)集成度和复杂度越来越高,通常一颗芯片上会有许多不同的信号工作在不同的时钟频率

2022-02-17 06:34:09

如何测量系统中时间相关的时域和频域信号?以RFID读写器系统为例,介绍MDO4000的跨域调试应用

2021-04-09 06:18:12

关于cdc跨时钟域处理的知识点,不看肯定后悔

2021-06-21 07:44:12

嵌入式开发之CPU的那些事...

2021-03-08 07:57:52

关于GPS定位的那些事不看肯定后悔

2021-09-26 07:11:20

我们在笔记本主板维修中见到的MOS管几乎都是绝缘栅增强型,这里也就只说说它的那些事儿吧。 而且,我们不谈原理,只谈应用。我们分“电路符号”和“实物”两部分来看

2014-10-08 15:21:00

关于iFrame特性总计和iFrame跨域解决办法

2020-05-15 14:26:43

关于异步时钟域的理解的问题: 这里面的count[25]、和count[14]和count[1]算是多时钟域吧?大侠帮解决下我的心结呀,我这样的理解对吗?

2012-02-27 15:50:12

好像***最近去英国还专程看了华为英国公司的石墨烯研究,搞得国内好多石墨烯材料的股票大涨,连石墨烯内裤都跟着炒作起来了~~小编也顺应潮流聊聊半导体材料那些事吧。

2019-07-29 06:40:11

你好,我在Viv 2016.4上使用AC701板。我需要同步从一个时钟域到另一个时钟域的多位信号(33位)。对我来说,这个多位信号的3阶段流水线应该足够了。如果将所有触发器放在同一个相同的切片

2020-08-17 07:48:54

CDC典型错误案例是什么?在芯片设计过程中,CDC有哪几种典型的错误场景?

2021-09-15 07:15:03

在main函数运行之前,不得不知的那些事在c_int00函数中完成的功能有哪些?

2021-04-20 06:03:06

采用FPGA来设计一款广泛应用于计算机、Modem、数据终端以及许多其他数字设备之间的数据传输的专用异步并行通信接口芯片,实现了某一时钟域(如66 MHz)的8位并行数据到另一低时钟域(如40 MHz)16

2011-09-07 09:16:40

时钟)的逻辑。在真正的ASIC设计领域,单时钟设计非常少。2、控制信号从快时钟域同步到慢时钟域与同步器相关的一个问题是来自发送时钟域的信号可能在被慢时钟域采样之前变化。将慢时钟域的控制信号同步到快时钟域

2022-04-11 17:06:57

跨时钟域处理是什么意思?如何处理好跨时钟域间的数据呢?有哪几种跨时钟域处理的方法呢?

2021-11-01 07:44:59

第二级寄存器的延拍,所以意义是不大的。02方法二:异步双口 RAM处理多 bit 数据的跨时钟域,一般采用异步双口 RAM。假设我们现在有一个信号采集平台,ADC 芯片提供源同步时钟 60MHz,ADC

2020-09-22 10:24:55

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。在本篇文章中,主要

2021-07-29 06:19:11

大家好。当我处理我的项目时,我发现了一个问题如下。我的DDR3应用程序端口为200 MHz,另一个内存控制器为100 MHz。 DDR3和控制器之间有一个DMA。我曾经认为我可以使用200 MHz进行DMA设计。但是DMA和控制器之间的接口并不容易。特别是发送和接收数据和cmd的时间。我在论坛上搜索相同的帖子但未找到。有什么建议吗?谢谢。以上来自于谷歌翻译以下为原文Hi, all. When I work on my project, I find a problem as follow.My DDR3 app port is 200 MHz and another memory controller is 100 MHz. There is a DMA between the DDR3 and the controller. I once think that I can use 200 MHz for the DMA design. But the interface between DMA and the controller is not that easy to be done. Especially the timing when sending and receive data and cmd.I've search the forum for the same thread but not found.Is there any advice?Thanks.

2019-02-25 10:11:15

嵌入式开发之CPU的那些事

2021-04-02 07:03:18

本帖最后由 lee_st 于 2018-4-3 09:43 编辑

嵌入式网络那些事LwIP协议深度剖析与实战演练

2018-04-02 10:44:08

我自己写了一个FIFO,但是我总是不理解Paper中讲的要把读写指针同步,如果我将两个不同时钟产生的读写地址直接比较,产生读写,请问这个亚稳态是怎么产生的,不要复制网上的那些东西,我都看了买就是不太

2016-04-11 23:13:45

亲爱的朋友们, 我有一个多锁设计。时钟为50MHz,200MHz和400Mhz。如果仅使用400MHz时钟并使用时钟使能产生200Mhz和50Mhz时钟域。现在我需要将信号从一个时钟域传递到另一个

2019-03-11 08:55:24

由于 ES_LPC5411x 中的勘误表 USB.1,需要 TN00031 中的解决方法才能跨多个 USB 集线器实现无晶体 USB。我正在研究从单个设备支持多个串行端口。但是,SDK 中的示例

2023-05-06 07:03:28

第二级寄存器的延拍,所以意义是不大的。02方法二:异步双口 RAM处理多 bit 数据的跨时钟域,一般采用异步双口 RAM。假设我们现在有一个信号采集平台,ADC 芯片提供源同步时钟 60MHz,ADC

2020-10-20 09:27:37

、状态逻辑、模 拟信号和RF信号的时间相关显示,大大缩短获得信息所需 的时间,降低跨域事件之间的测量不确定度。了解嵌入式RF设计内部微处理器命令与RF事件之间的时间 延迟简化了测试设置,可以在工作台

2017-08-31 08:55:59

看到很多芯片的数据手册有这种类似的框图,包括时钟RTC网络那些图,怎么理解这种图?

2020-06-18 11:46:06

逻辑出身的农民工兄弟在面试时总难以避免“跨时钟域”的拷问,在诸多跨时钟域的方法里,握手是一种常见的方式,而Stream作为一种天然的握手信号,不妨看看它里面是如做跨时钟域的握手

2022-07-07 17:25:02

知识转移策略的跨域故障诊断背景转移学习概述转移学习方法研究动机和问题设置跨域方法在故障诊断中的应用开源故障数据集背景数据驱动诊断方法的常用验证方式为通过将一个数据集分为训练集和测试集来保证这两个

2021-07-12 07:37:58

自动焊锡机那些你不知道的事

2021-05-11 06:08:45

型的问题,并且这些问题的解决方案也有所不同。本文讨论了不同类型的跨时钟域,以及每种类型中可能遇到的问题及其解决方案。在接下来的所有部分中,都直接使用了上图所示的信号名称。例如,C1和C2分别表示源时钟

2022-06-23 15:34:45

和发送数据,处理异步信号,以及为带门控时钟的低功耗ASIC进行原型验证。 这里以及后面章节提到的时钟域,是指一组逻辑,这组逻辑中的所有同步单元(触发器、同步RAM块以及流水乘法器等)都使用同一个网络

2022-10-14 15:43:00

在我们的设计开发过程中,经常会遇到的问题是:接口,而接口是外围芯片与MCU大脑连接的通关口。芯片的接口有很多种,选择合适的接口至关重要。我们来看看一些通常的接口,可能搜集不全,欢迎大家回帖补充!大家

2014-02-18 17:37:03

Vue加入withCredentials后无法进行跨域请求

2020-11-06 06:39:42

1、跨时钟域信号的约束写法 问题一:没有对设计进行全面的约束导致综合结果异常,比如没有设置异步时钟分组,综合器对异步时钟路径进行静态时序分析导致误报时序违例。 约束文件包括三类,建议用户应该将

2022-11-15 14:47:59

嵌入式网络那些事LwIP协议深度剖析与实战演练

2016-06-12 13:43:17

40Nginx的反向代理功能解决跨域问题

2019-10-10 10:58:03

提高设计的组织架构

l处理ASIC验证原型里的门控时钟

n建立一个单时钟模块

n自动门控移除

图2:通过门控时钟创建的时钟域

一、跨时钟域

设计中包含多时钟域,首先要解决的是在不同时钟域之间传输信号

2023-06-02 14:26:23

这一章介绍一下CDC也就是跨时钟域可能存在的一些问题以及基本的跨时钟域处理方法。跨时钟域的问题主要存在于异步

2017-11-30 06:29:00 6603

6603

了解如何使用命令report_cdc分析,调试和修复设计中的CDC问题。

命令report_cdc是一个仅限TCL的命令,用于分析您的设计并识别设计中潜在的CDC结构问题并将其标记为安全或

2018-11-21 06:05:00 4254

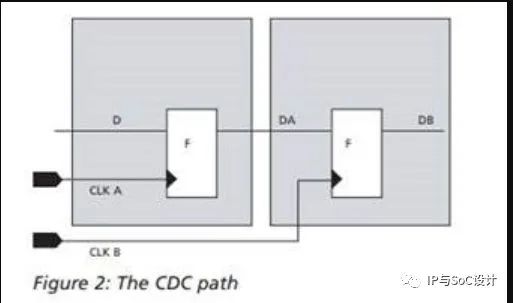

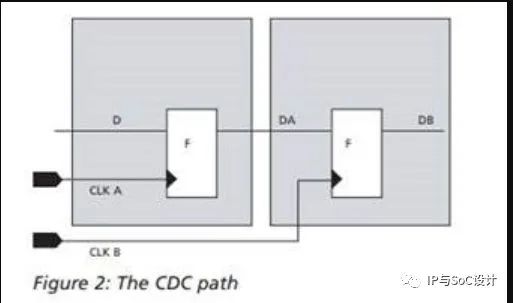

4254 一个系统中往往会存在多个时钟,这些时钟之间有可能是同步的,也有可能是异步的。如果一个系统中,异步时钟之间存在信号通道,则就会存在CDC(clock domain crossing)问题。在下面的文章里,我们将会讨论CDC的一些技术细节。

2019-01-04 16:59:30 14089

14089

关于STM32时钟配置的那些坑

2020-03-08 12:06:08 5419

5419 title: STM32 USB如何配置多个CDC设备—5个CDC设备,date: 2021/1/18 20:10:25 +8,STM32 USB如何配置多个CDC设备—5个CDC设备1. 背景由于

2021-12-28 19:43:45 30

30 CDC(不同时钟之间传数据)问题是ASIC/FPGA设计中最头疼的问题。CDC本身又分为同步时钟域和异步时钟域。这里要注意,同步时钟域是指时钟频率和相位具有一定关系的时钟域,并非一定只有频率和相位相同的时钟才是同步时钟域。异步时钟域的两个时钟则没有任何关系。这里假设数据由clk1传向clk2。

2022-05-12 15:29:59 1334

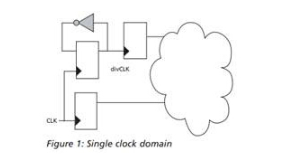

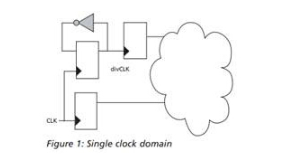

1334 时钟域clock domain:以寄存器捕获的时钟来划分时钟域。

单时钟域single clock domain,数据发送和接收是同一个时钟

多时钟域multiple clock domain,数据发送和接收是不是同一个时钟

2022-08-29 15:11:21 1898

1898 时钟域clock domain:以寄存器捕获的时钟来划分时钟域。单时钟域single clock domain,数据发送和接收是同一个时钟。

2022-12-26 15:21:04 1224

1224 在一些较为简单的数字电路中,只有一个时钟,即所有的触发器都使用同一个时钟,那么我们说这个电路中只有一个时钟域。

2023-03-15 13:58:28 1596

1596 CDC 验证不仅在 RTL 有必要,在门级也必不可少。在 RTL,重点是通过识别 CDC 结构和方案来确定时钟域和 CDC 路径。

2023-03-30 11:03:38 846

846 上一篇《XDC 约束技巧之时钟篇》介绍了 XDC 的优势以及基本语法,详细说明了如何根据时钟结构和设计要求来创建合适的时钟约束。我们知道 XDC 与 UCF 的根本区别之一就是对跨时钟域路径(CDC

2023-04-03 11:41:42 1135

1135 随着技术的发展,数字电路的集成度越来越高,设计也越来越复杂。很少有系统会只工作在同一个时钟频率。一个系统中往往会存在多个时钟,这些时钟之间有可能是同步的,也有可能是异步的。如果一个系统中,异步时钟之间存在信号通道,则就会存在CDC(clock domain crossing)问题。

2023-06-21 10:54:38 8574

8574

CDC(Clock Domain Conversion)跨时钟域分单bit和多bit传输

2023-06-21 14:59:32 1001

1001 在数字系统级别的时钟域交叉(CDC)中,亚稳态传播问题是一个重要的挑战。在这个问题中,由于时序差异,信号在触发器之间的传输可能会导致亚稳态值的产生和传播。让我们来看一下模型,如图1所示。

2023-08-14 11:48:11 541

541

电子发烧友App

电子发烧友App

评论