摘要:为了调节两路相同频率正弦信号之间的相位差,采用DDS技术设计了相位关系可调的双通道信号发生器。该信号发生器的输出频率范围为0Hz~150MHz,频率分辨率为1μHz,相位调节范围为0°~360°,分辨率为0.022°。它不仅可输出两路相同频率、相位差可调的正弦信号,而且可分别作为两路独立的可调频、调幅、调相的信号发生器使用。

正弦信号发生器作为电子技术领域中最基本的电子仪器,广泛应用于航空航天测控、通信系统、电子对抗、电子测量、科研等各个领域中[1~2]。随着电子信息技术的发展,对其性能的要求也越来越高,如要求频率稳定性高、转换速度快,具有调幅、调频、调相等功能,另外还经常需要两路正弦信号不仅具有相同的频率,同时要有确定的相位差。

要实现两路信号具有确定的相位差,通常有两种实现方法:—‘种是采用移相器实现,如阻容移相网络、电感移相器、感应分压器移相器等。这种方法有许多不足之处,如移相精度受元件特性的影响大、移相精度差、移相操作不方便、移相角受负载和时间等因素的影响而漂移等;另一种是采用数字移相技术,这是目前移相技术的潮流[3]。数字移相技术的核心是先将模拟信号或移相角数字化,移相后再还原成模拟信号。本文采用直接数字频率合成技术设计了双通道正弦信号发生器,可以输出两路频率相同、相位差可调的正弦信号。两通道还可以独立使用,分别进行调频、调幅及调相。该信号发生器具有频率稳定度高及调频、调相迅速的优点。

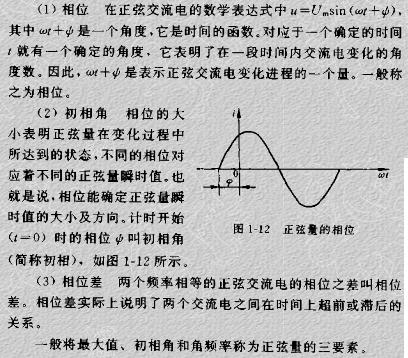

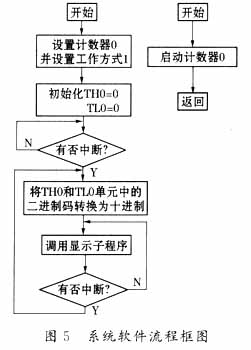

1 直接数字频率合成器的基本原理

频率合成是指对一个标准信号频率经过一系列算术运算,产生具有相同精度和稳定度的大量离散频率的技术。频率合成有多种实现方法,其中直接数字频率合成技术与传统频率合成技术相比具有难以比拟的优点,如频率切换速度快、分辨率高、频率和相位易于控制等[4~5]因此得到越来越广泛的应用,成为当今现代电子系统及设备中频率源设计的首选。

直接数字频率合成器由参考时钟、相位累加器、正弦查询表和D/A转换器组成,如图1所示。

直接数字频率合成技术是根据相位间隔对正弦信号进行取样、量化、编码,然后储存在EPROM中构成一个正弦查询表。频率合成时,相位累加器在参考时钟的作用下对时钟脉冲进行计数,同时将累加器输出的累加相位与频率控制字K预置的相位增量相加,以相加后的吉果形成正弦查询表的地址;取出表中与该相位对应的单元中的幅度量化正弦函数值,经D/A转换器输出模拟信号,再经低通滤波器平滑得到符合要求的模拟信号。相位累加器的最大计数长度与正弦查询表中所存储的相位分隔点数相同,由于相位累加器的相位增量不同,将导致一周期内的取样点数不同,在取样频率(由参考时钟频率决定)不变的情况下,输出信号的频率也相应变化。如果设定累加器的初始相位,则可以对输出信号进行相位控制。 由采样原理可知,如果使用两个相同的频率合成器,并使其参考时钟相同,同时设定相同的频率控制字、不同的初始相位,那么在原理上就具备了实现输出两路具有一定相位差的同频信号的可能性。

AD9852是ADI公司生产的高集成度的频率、相位、幅度可调的直接数字频率合成器,内部集成了高性能D/A转换器、高速比较器、程序寄存器、参考时钟倍频器及可实现各种运算的高性能的数字控制单元,并且可以实现全数字编程控制。AD9852的输出信号频率控制字为48位,使输出频率调节分辨率达到1μHz,输出信号的频率范围可从直流到150MHz,相位调节控制字为14位,相调节分辨率为0.022°,幅值调节控制字为12位。本文所设计的信号发生器以两片AD9852为核心。

图2

2 信号发生器的硬件设计

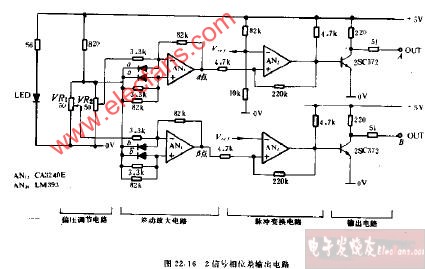

信号发生器由计算机、接口电路、CPLD、频率合成芯片、低通滤波器组成,其组成框图如图2所示。计算机通过接口电路和CPLD分别给两片频率合成芯片AD9852送人频率控制字、相位控制字和幅值控制字,使其输出一定频率、相位和幅值的正弦波信号,经过低通滤波器后形成平滑的正弦波。

要使两路输出信号A和B的相位差可调,必须保证两路信号同步,为此要满足以下条件:

(1)输入到两个AD9852的参考时钟之间要有足够小的相位偏移。这个相移会导致输出信号之间产生与之成比例的相移。因此必须精心进行布线设计,使从CPLD输出参考时钟的引脚到两个AD9852的参考时钟输入引脚的引线距离相等,以保证系统时钟同步。另外,参考时钟上升/下降沿的抖动应尽可能小,并且上升/下降时间应尽可能短,因为不同AD9852输入电路的触发电压不同,因此参考时钟的上升/下降沿时间长会增加输出信号的相位误差。

(2)频率控制字送到AD9852的数据缓冲区后,还必须通过一个更新时钟才能将数据缓冲区中的数据送到相位累加器,成为有效数据后进行输出。AD9852有两种更新时钟产生方式,一种由芯片内部自动产生,另一种由外部提供。要使两路输出信号同步,必须使用外部I/O更新时钟,同时必须使参考时钟信号(REFCLK)与外部I/O更新时钟(UPDATE CLK)上升沿之间满足图3所示的时序关系。

更新时钟的上升沿必须在参考时钟的下降沿0.3ns之后与下一个下降沿1.5ns之前之间(图3中深色区间为有效区域)产生,这样可以使两个AD9852工作在相同的系统时钟(参考时钟乘以一定倍数)下,且它们的系统时钟脉冲数相差不能超过1个脉冲。

(3)在第一次传送数据之前必须先使AD9852复位,以保证AD9852的输出相位可知。因为AD9852的相位输出是连续的,所示复位信号可使两个AD9852的相位累加器复位到COS(0)状态。新的数据送到相位累加器时,它们之间的相位关系可以得到保持,也可以通过相位控制字来调节两片AD9852之间的相位差。

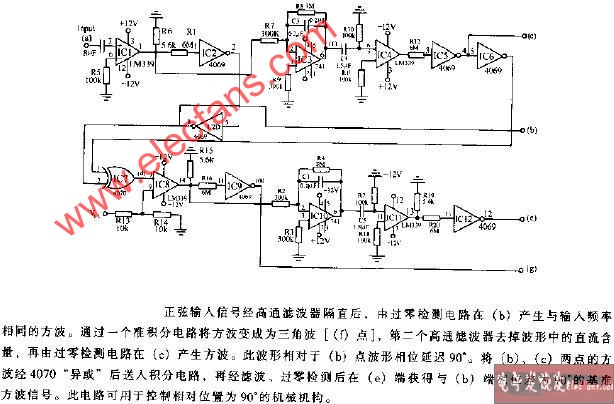

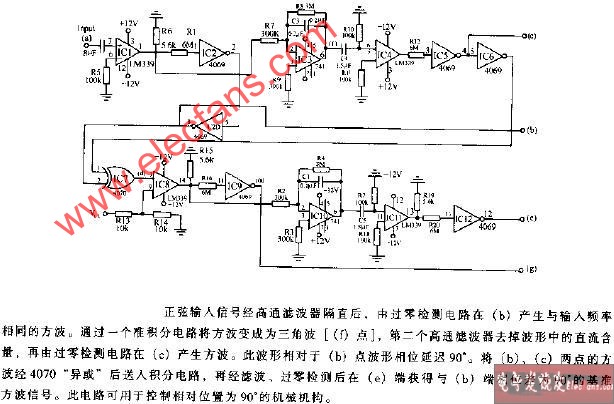

CPLD(大规模可编程逻辑器件)具有静态可重编程或在线动态重构的特性,使得硬件功能可以像软件一样通过编程来修改,不仅使设计修改变得十分方便,而且大大提高了电子系统的灵活性和通用能力,因此成为当今实现电子系统集成化的重要手段。本文用CPLD实现计算机与两片AD9852的输入接口。CPLD内部电路如图4所示。

图4

AD9852的接口部分主要由三个锁存器、一个D触发器、三个或门、一个非门组成。图中D10~D17为计算机接口电路的数据总线,用于给AD9852传送数据、地址和控制信号;A10~A12为地址信号,分别用来选通数据锁存器(U1)、地址锁存器(U2)和控制信号锁存器(U3);WR为锁存器的写控制信号;CLKIN为参考时钟输入,由一个恒温晶振提供,以保证尽可能小的相位抖动。输出信号WR1为第一片AD9852的写控制信号,WR2为另一片AD9852的写控制信号,RESET、UPDATE CLK、REFCLK分别为两片AD9852的复位信号、I/O更新时钟信号和参考时钟。其中,D触发器用来实现图2所示的参考时钟与I/O更新时钟之间的时序关系。

本文采用直接数字频率合成技术设计了双通道相位关系可调的信号发生器,输出信号频率范围为直流到120MHz,频率分辨率高于0.01μHz,相位调节分辨率为0.22°。两个通道不仅可以输出相同频率的信号,还可以输出不同频率、不同相位、不同幅值的正弦信号。经在石英晶体测试系统中使用表明,本设计达到了设计要求,应用方便灵活。

- 相位差可(5536)

相关推荐

相位差如何测量

AD7606采集数据有相位差是怎么回事?

AD9361 2R2T时本振频率相位差问题

OP2177的两个通道的相位差超过0.4度

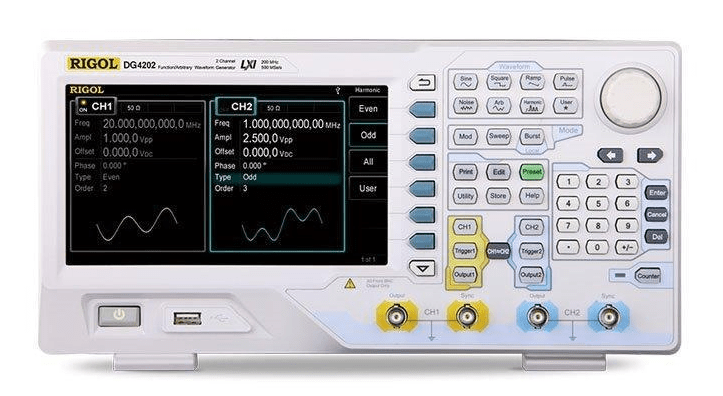

RIGOL DG4000系列双通道 函数/任意波形发生器性能特点

【小梅哥FPGA】带上位机的高速双通道DDS信号发生器

【干货】如何使用示波器测量相位差

使用owon AG 1012信号发生器产生一个余弦波形

函数信号发生器哪家强

单片机相位差测量方法研究

基于AD8302的相位差测量系统的改进和设计

如何使用FPGA芯片实现相位差计的设计?

如何实现同频信号相位差测量算法?

怎么测量移相器输出和输入的相位差?怎么去仿真相位差?

扫频时两个通道之间的随机相位差?

方波 相位差

求助,关于OP2177的两个通道的相位差问题

求助,用AD8302 测量信号增益 相位差

用示波器测量相位差

请问AD7606采集数据有相位差可能是哪里出现问题了?

请问THS1209两个通道同时采样同一个信号为什么会有相位差?

请问labview双通道虚拟信号发生器如何设计?

输出3路相位差为120°的正弦波信号的信号发生器,求大家推荐一款比较好用的DDS芯片

高精度相位差计的设计

双通道多普勒测向机研究

29

29相位差测量方法的研究与应用

125

125正弦信号的直接FFT参数估计与相位差分法对比研究

29

29数字式工频电压相位差测量仪的设计

64

64干涉仪相位差抖动分析

10

10G简易双相信号发生器

45

45多通道零相位差数据采集系统设计与实现

689

689

数字化宽带测向系统中的相位差测量及误差

2688

2688

相位差与相位关系、相位差的数字测量

46714

46714电流相位差动保护的仿真

1

1对于电容、电感产生的相位差该如何理解

6053

6053

简易数显式工频信号相位差测量仪的详细资料说明

6

6四通道幅频相可调DDS信号发生器

29

29从4个方面来详解电容、电感的相位差是如何产生的

14694

14694

详解电容、电感的相位差是如何产生的

1888

1888电容电感的相位差是如何产生的

14

144个方面!详解电容、电感的相位差是如何产生的?

8

8发射信号与接收信号之间的相位差如何计算

2298

2298FFT相位差

7

7普源函数信号发生器DG4202

291

291

如何理解电容、电感产生的相位差

594

594

正弦信号的电流和其两端的电压它们的相位差是如何产生的呢?

480

480RC电路中相位差是如何引起的?电路中的相位差与哪些因素有关?

1376

1376差分信号如何用单端探头测量相位差?

204

204

如何减小电流互感器的相位差

317

317差分信号如何用单端探头测量相位差?

179

179移相电路引起相位差的原因是什么

221

221 电子发烧友App

电子发烧友App

评论