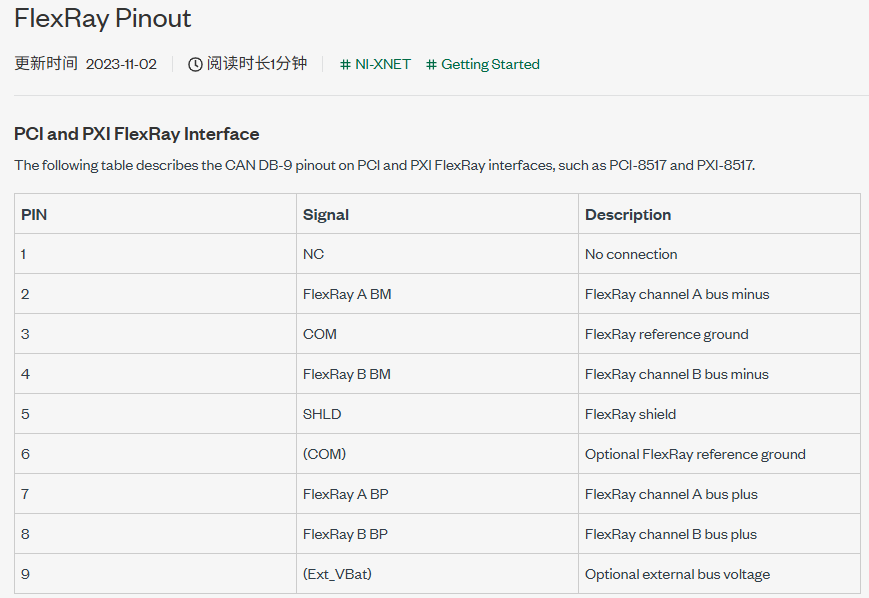

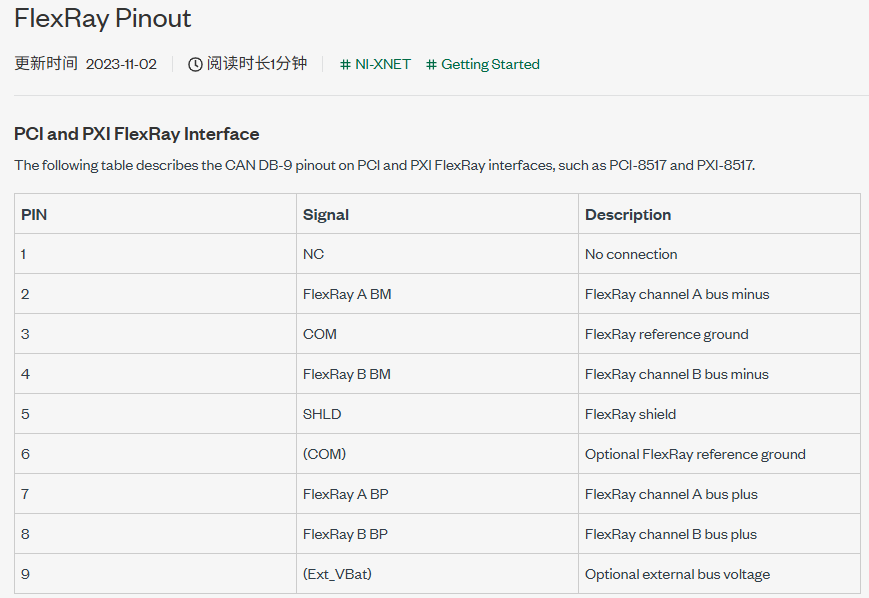

本篇教程源于一位客户的真实需求,想将Flexray信号通过软件转为Can信号,硬件设备有PXI-8517、cDAQ-9188、NI-9862。经过小编验证是可行的,

2025-07-03 09:16:29 1144

1144

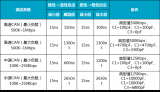

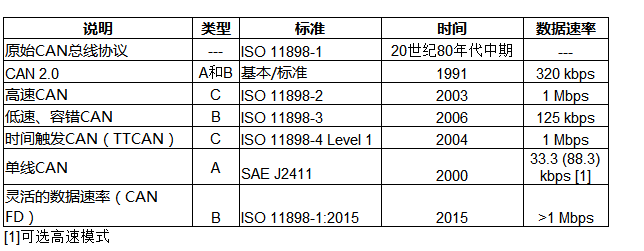

CAN总线设计规范对于CAN节点的差分电平位信号特征着严格的规定,如果节点的差分电平位信号特征不符合规范,则在现场组网后容易出现不正常的工作状态,各节点间出现通信故障

2015-10-07 19:00:09 13802

13802

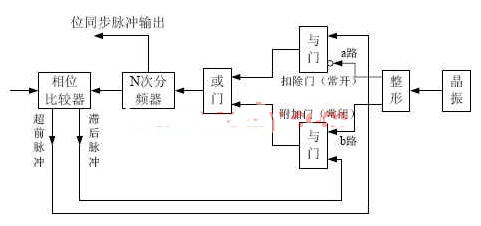

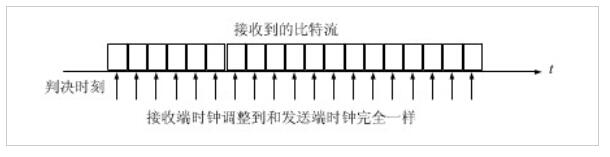

在时分复接通信系统中,位同步是收、发两端的时钟频率必须同频、同相,这样在接收端才能正确地判决发送端送来的每一个码元。为了达到收、发端频率同频、同相,在设计传输码型时,一般要考虑传输的码型中应含有发送

2020-07-30 18:02:44 1747

1747

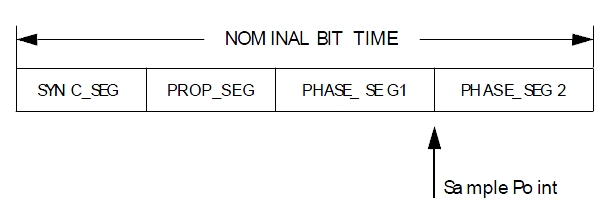

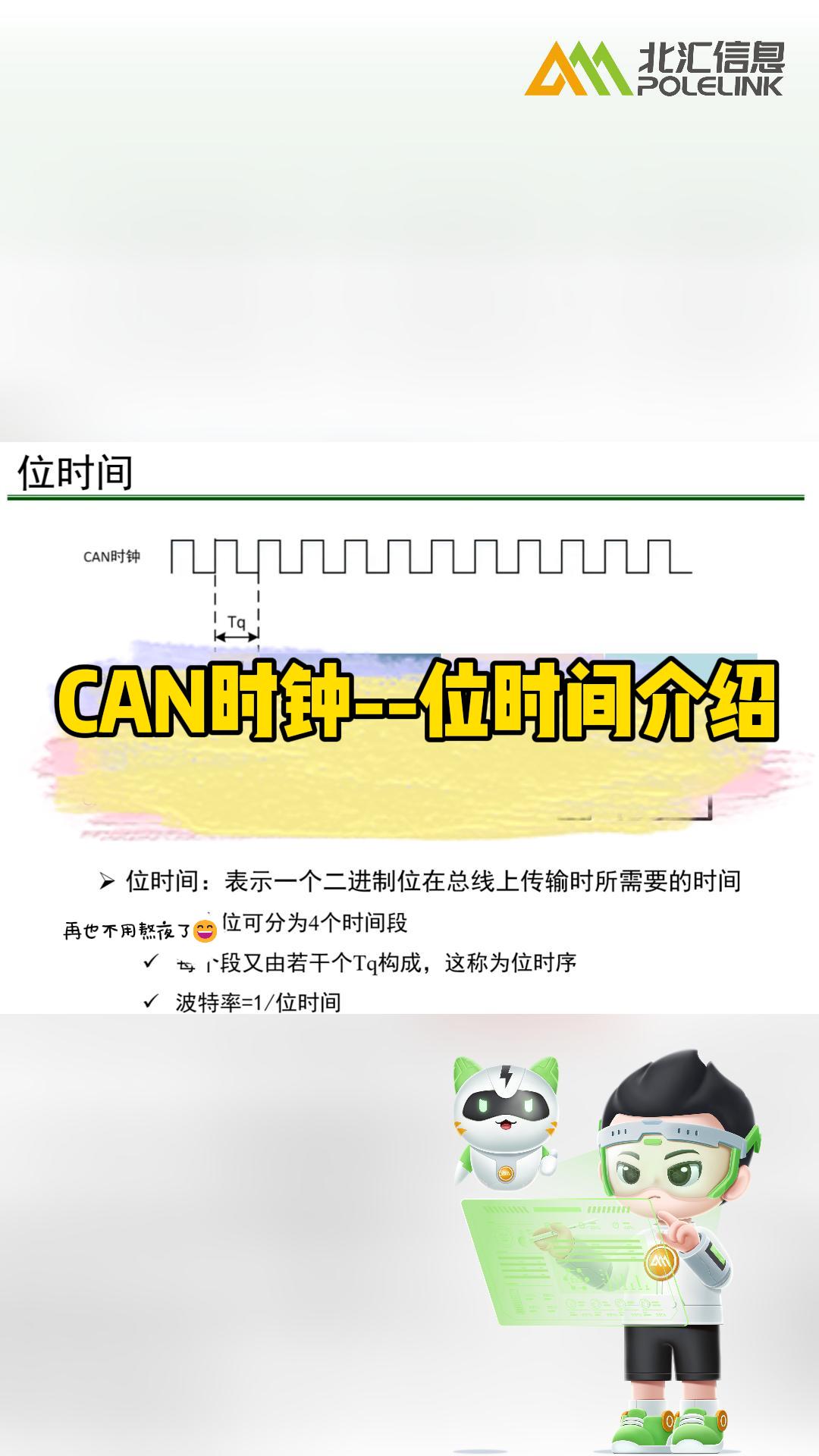

对一般的开发者来说,CAN总线的位定时概念并不常见。不过,如果给整车厂做过零部件,经受过他们的CAN通信测试考验,您可能就知道,这也是比较重要的一个知识点。

2022-08-26 17:15:19 4866

4866

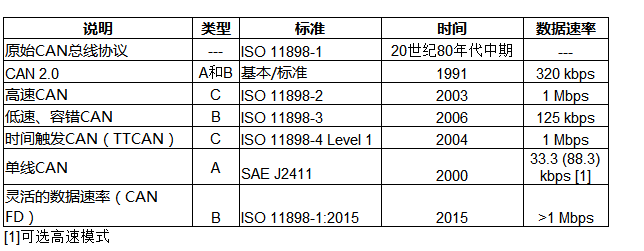

CAN协议与其它现场总线协议的区别中有一个是:它使用同步数据传输而不是异步传输(面向字符)。这意味着传输性能得到更有效的发挥,但是另一方面,这需要更加复杂的位同步方法。如何确保位同步?在面向字符

2024-07-17 08:25:36 2489

2489

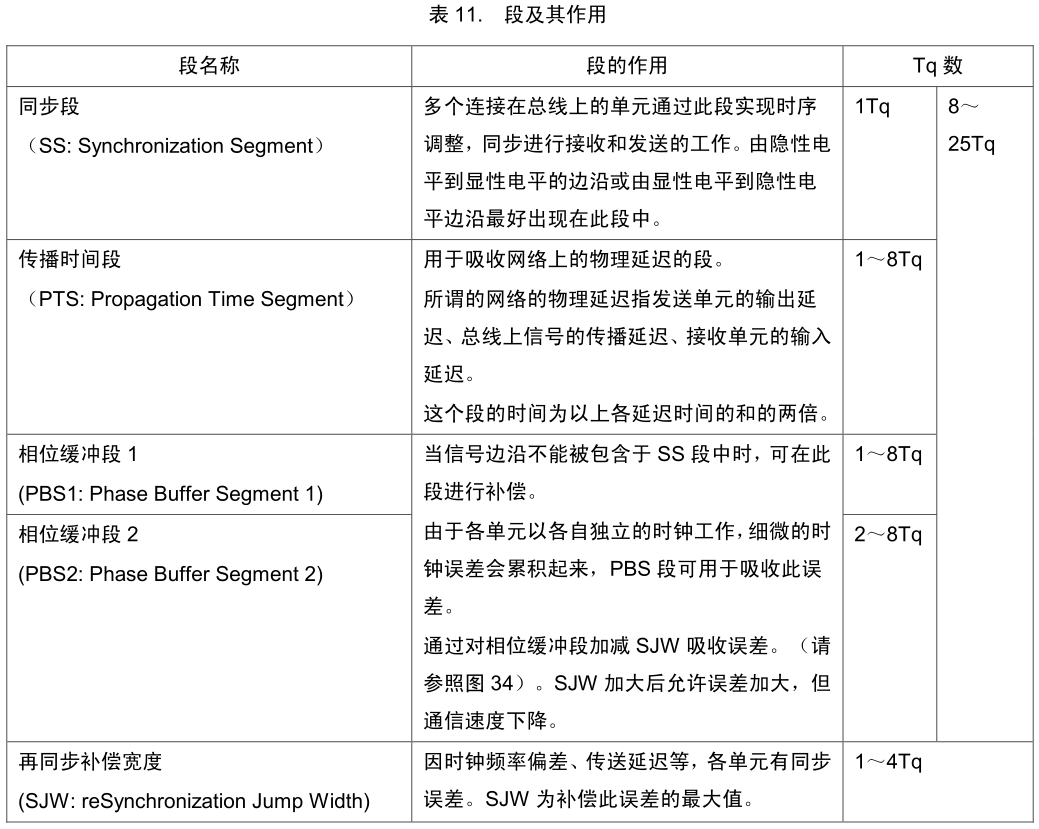

位定时规格的确定需要考虑总线的物理特性和网络的通信要求,包括晶振频率总线长度、传输延迟等。通过合理的配置这些参数,可以保证网络上不同节点之间的数据传输同步,从而确保通信的可靠性。位定时段的规格是根据

2024-08-14 08:25:38 1478

1478

什么是CAN总线信号传输的位定时?什么是CAN总线信号传输的位同步?

2021-05-18 06:52:14

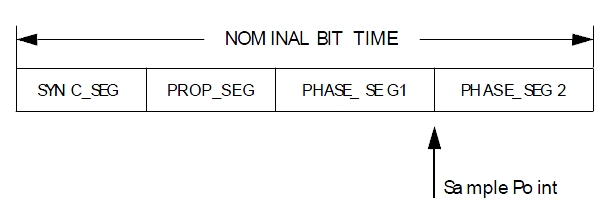

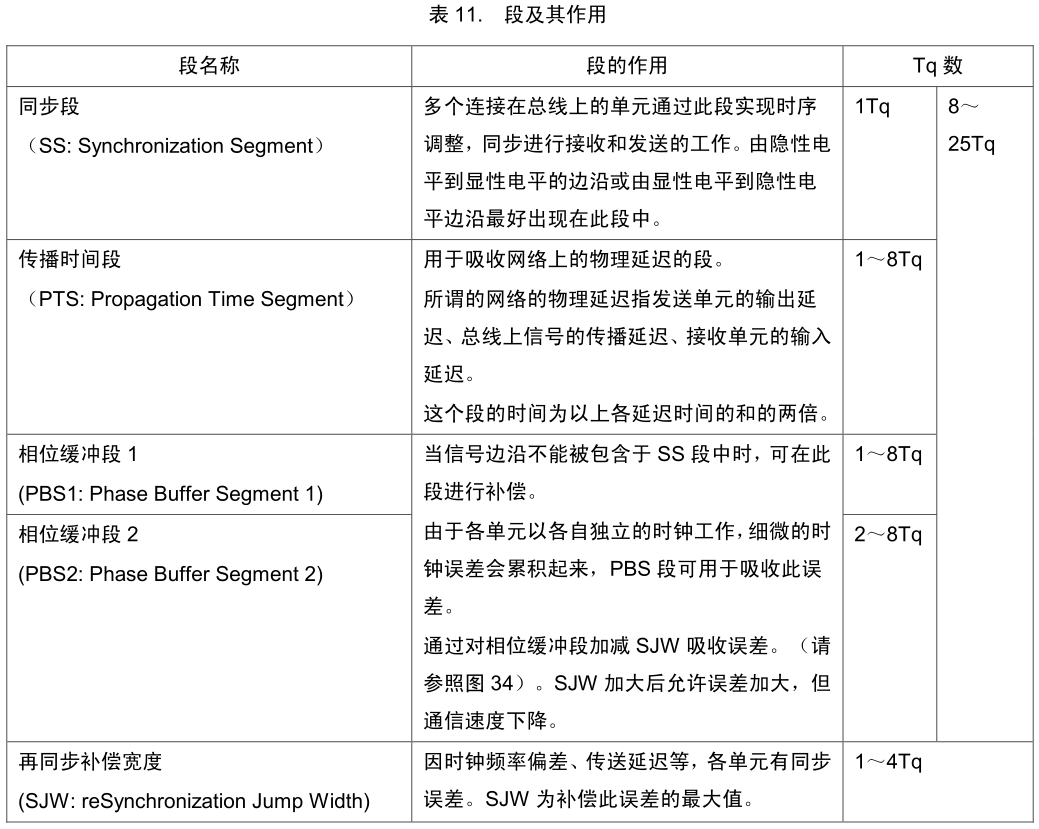

CAN总线通讯协议的每一帧可以看作一连串的电平信号,每一个电平信号代表一位(一个字节8位的位),所以一帧中包含了很多个位,由发送单元在非同步的情况下发送的每秒钟的位数称为位速率。一位又分为4段,同步段(SS)、传播时间段(PTS)、相位缓冲段 1(PBS1)、相位缓冲段 2(PB...

2021-08-20 07:43:39

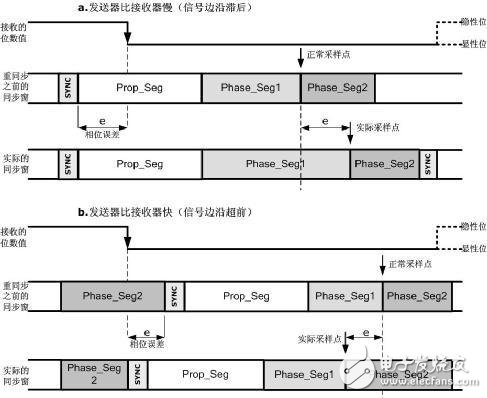

和相位缓冲段2开始处。(2)传播时间段用于补偿总线上信号传播时间和电子控制设备内部的延迟时间。因此,要实现与位流发送节点的同步,接收节点必须移相。CAN总线非破坏性仲裁规定,发送位流的总线节点必须能够收到

2012-10-11 17:19:06

接收器不断进行重新同步。重新同步表示在位流中每个有效的信号边沿都可对接收信号的时钟周期进行检测。在信号边沿间的最大时间周期内,发送和接受振荡器之间最大可能的时间差必须在一个位间隔内的标称采样点之前和之后

2016-08-15 15:59:45

1.硬同步(Hard Synchronization)硬同步后,内部位时间从同步段(SYNC_SEG)重新开始,它迫使触发该硬同步的跳变沿处于新的位时间的同步段(SYNC_SEG)之内。2.重同步

2018-12-18 14:51:33

采样点不一致是CAN总线网络中常见的配置错误,可能导致位错误、同步问题、错误帧增加、节点总线关闭、仲裁失败和确认错误等严重后果。

CAN总线的位时间由四个非重叠的时间段组成,每个段由时间

2025-06-07 08:55:26

采样点为位的50%处就不可,设置为90%即可。但是波形整段就是全高或者全低,50%处和90%处信号不是都一样吗?为什么读其他地方就不行呢?还有,如何通过波形,或者其他工具可以判断出这几个段所占的时间长度。谢谢

2022-10-25 15:02:10

位时序逻辑实现 CAN 总线协议中对位同步的有关控制。位时序逻辑监视串行 CAN 总线并处理与总线相关的位时序。它在报文开始发送、总线电平从隐性值跳变到显性值时同步于 CAN总线上的位数据流(硬同步

2018-12-20 11:40:50

位时序包括正常位速率和正常位时间两个参数。• 正常位速率(Nominal Bit Rate):在非重同步情况下,借助理想发送器每秒发送的位数。• 正常位时间(Nominal Bit Time):正常

2018-12-17 11:13:33

位同步时钟的提取原理是什么?位同步时钟的提取电路该怎样去设计?

2021-05-07 06:51:36

位,硬件强制为0。[/tr][tr=transparent]位25:24SJW[1:0]: 重新同步跳跃宽度为了重新同步,该位域定义了CAN硬件在每位中可以延长或缩短多少个时间单元的上限。tRJW

2018-03-21 14:16:46

MCU是野火的STM32H743挑战者,例程基于野火的《CAN双机通信》;位时序分解STM32 的 CAN 外设位时序中只包含 3 段,分别是同步段 SYNC_SEG、位段 BS1 及位段 BS2

2021-08-11 09:10:55

决定。重新同步可通过应用“位填充”的方法实现。这种方法是在一定数量的恒定位电平之后将一个反码插入到位流中。 图1NRZ和曼彻斯特编码的位表示 CAN协议中应用的是带位填充(填充宽度为5位)的NRZ信号

2016-07-21 16:49:03

什么是位时间?如何去划分它?什么是位同步?位同步的规则有哪些?

2021-05-13 06:01:45

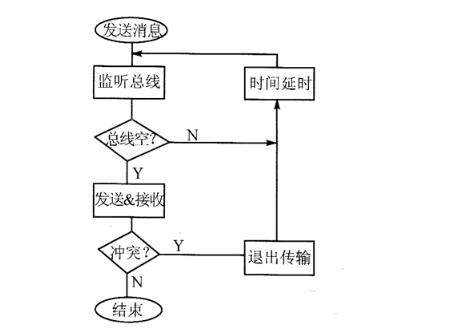

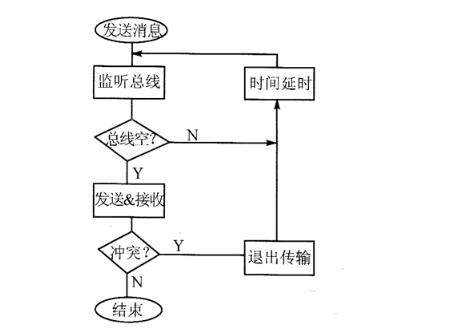

延迟可能会影响并发传输和节点间的仲裁。冲裁依赖于CAN信号;逻辑0表示“主动”(总线间存在差分电压),逻辑1表示“被动”(全部输出变为高阻抗),意味着主动位将覆盖被动位。发射期间,所有节点均会监控总线

2018-10-22 16:40:46

是定义位段,并将采样点设得尽可能晚。对于表1中的每个有效选项,SYNC段必须允许有一个TQ,并且TSEG2 (PS2)段必须适应CAN控制器处理时间(只要BRP大于4,BF548就要低于1 TQ

2018-10-16 17:00:07

CAN里有一个位同步的概念,我以前用STM32时,还有专门用于做位同步的结构体请问我现在用FPGA作CAN,需不需要设计位同步?还是外接的独立CAN控制器自己本身就有位同步

2018-10-10 09:35:45

关于CAN总线位定时和同步机制的简要分析

2021-05-28 06:05:24

基于32位ARM7的CAN节点设计

2013-03-31 10:48:13

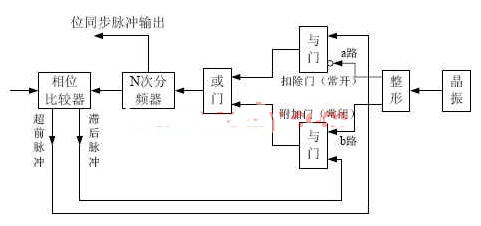

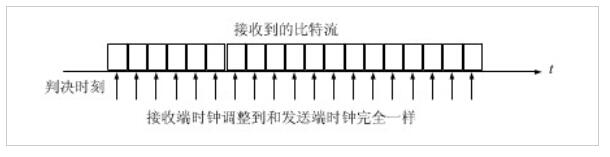

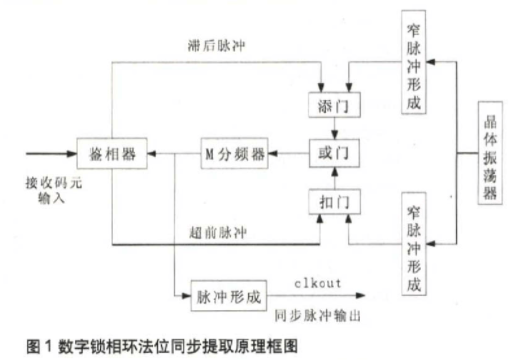

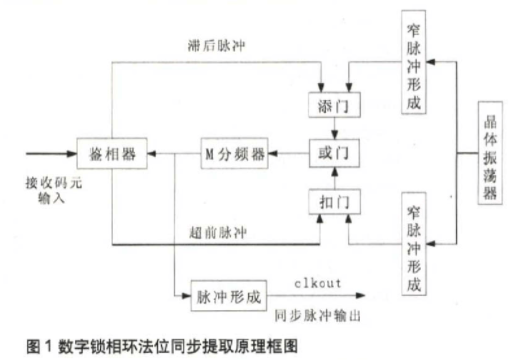

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发同步,而且在获取帧同步及对接收的数字码元进行各种处理的过程中也为系统提供了一个基准

2019-08-05 06:43:01

络中,数据通过双绞线上的差分信号传输。信号质量直接影响节点正确解读数据的能力。信号质量差可能表现为:

位错误 :由于噪声或信号失真导致的位误判。 帧错误 :CAN帧结构错误,导致接收节点拒绝。 总线

2025-06-07 08:46:40

但我们无法在代码中配置 RTR 位,能否请你解释一下如何配置 RTR 位以在生成的 CAN_NODE_0 中接收远程帧。

2024-01-19 06:38:58

帧同步通常采用的方法有逐位调整法和置位调整法,对比分析哪个好?采用置位调整法设计帧同步系统

2021-04-14 06:34:56

我使用PSoC 5LP覆盖8位并行(BT.665)视频流上的像素。我需要同步我的DMA与嵌入在视频流中的垂直同步信号。我使用的是一个四TD的DMA通道,什么是重整整个链的正确方法?目前,我有一个垂直

2019-09-18 08:36:09

CAN总线的位时序与参数设置@ [TOC]CAN的位时序构成CAN总线的每个位(Bit)的周期 Tbit = 1 / Baudrate。根据CAN规范,每个位的时间内又可细分成4段:同步段

2021-08-20 06:38:55

[/td][td]CAN总线物理层1. 物理层1.1.1 位定时1.时间份额(Time Quantum),时间份额来源于对系统时钟可编程的分频。时间份额原理如图4.11.1。1.波特率l波特率由编程

2015-06-25 13:48:54

预备问题:比特率与波特率区别我查阅了相关资料,知道比特率指每秒发送多少二进制位,波特率指每秒发送多少码元,请问这个码元指的是什么?请结合can数据报文解释一下。位时间的问题:位时间是位速率的倒数

2018-08-06 19:51:31

基于CAN总线的智能寻位制造系统

智能寻位制造系统的组成网络化智能寻位制造系统的概念是将智能寻位,工艺规划# 加工信息生成# 加工设备控制等分布于制造系统中

2008-10-21 01:54:20 22

22 针对位同步问题,提出了一种基于基函数分解的开环位定时估计算法。该算法首先利用基函数分解的结果进行相关运算,将本地参考信号波形和接收信号波形的定时偏差缩小到T/4

2008-12-16 01:12:00 13

13 CAN 通信中, 波特率、位周期内取样点数和位置可以编程设置, 这些设置为用户根据其应用优化网络通信性能提供了方便。优化位定时参数,能够保证信息同步,保证传输延迟和时

2009-05-15 15:08:40 6

6 在设计数字控制的信号发生电路中8位DA转换器的运用:

2009-06-13 10:42:41 29

29 关键词 LM3S2016、CTM系列隔离CAN收发器摘 要 基于32位Luminary ARM的CAN节点设计

2009-11-07 14:16:41 13

13 位定时参数对CAN 总线网络性能有着显著影响,如果位定时有一点小错误都会导致总线性能严重下降。针对这一问题,本文通过对CAN 总线位定时控制方法的分析,提出了一种有效

2010-01-25 15:06:15 9

9 从时分复接系统对位同步系统的性能要求出发,提出了一种基于FPGA的快速位同步系统的设计方案,给出了位同步系统的实验仿真,结果表明该系统有较快的位同步建立时间,节省了F

2010-07-28 18:13:40 22

22 数字同步的基本概念

同步是指通信双方的定时信号符合一定的时间关系,它又可以分为位同步、帧同步和网同步:

位同步是指通信双方的位定时脉冲信

2010-11-13 16:38:04 36

36

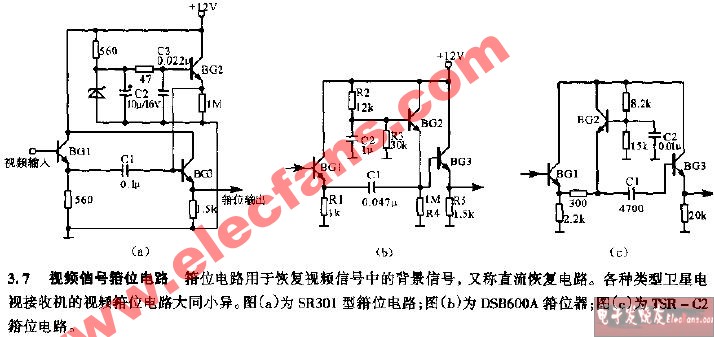

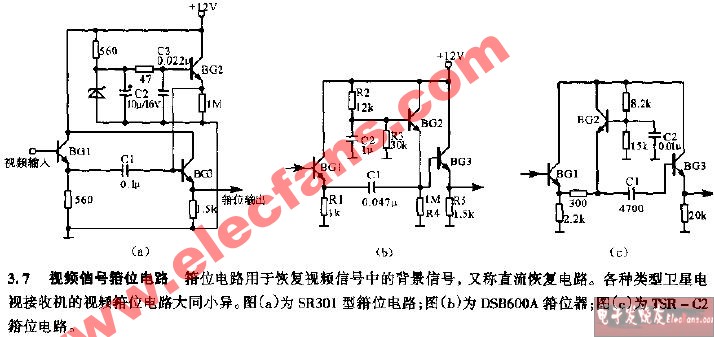

视频信号箱位电路

2009-03-13 19:38:16 550

550

实验五 数字锁相环与位同步

一、 实验目的

1. 掌握数字锁相环工作原理以及触发式数字锁

2009-04-01 09:27:45 6242

6242

基于FPGA的提取位同步时钟DPLL设计

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发

2010-01-25 09:36:18 3700

3700

位同步,位同步是什么意思

在数字通信系统中,发端按照确定的时间顺序,逐个传输数码脉冲序列中的每个码元。而在接收端必须有准确的抽样判决

2010-03-17 17:31:54 17171

17171 位同步提取实验的实验报告,位同步提取实验的实验报告,位同步提取实验的实验报告

2016-05-26 10:58:41 0

0 表示一个位。而曼彻斯特编码的信号在一个位时间内发生变化,因此需要两个时隙来表示一个位。曼彻斯特编码的优点是每个位都有一个信号边沿用来实现位同步(Self-clocking code)。

2016-07-20 17:19:35 3594

3594

CAN协议与其它现场总线协议的区别中有一个是:它使用同步数据传输而不是异步传输(面向字符)。这意味着传输性能得到更有效的发挥,但是另一方面,这需要更加复杂的位同步方法。

2016-08-16 16:56:39 2412

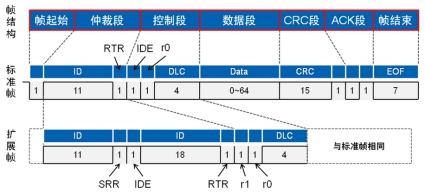

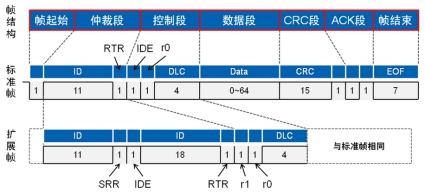

2412 CAN-bus总线是应用最广泛的现场总线之一,而很多非常熟练的CAN工程师,面对一条CAN报文到底有多少位的问题时,却不能非常准确地回答。今天我们就从最基本的帧格式来解惑一条CAN报文的到底有多少位。

2017-06-06 16:36:29 36411

36411

在数字通信系统中,为了实现正确的数据通信任务,需要实现多种同步功能。位同步是同步系统的关键,其质量的好坏直接影响整个通信系统的性能。因此,关于位同步的研究和算法层出不穷,其中Cardner算法具有

2017-11-02 15:22:01 1

1 在FPGA中,随着信号处理的层次加深,对信号进行乘、累加、滤波等运算后,可能输入时仅为8位位宽的信号会扩展成几十位位宽,位宽越宽,占用的硬件资源就越多,但位宽超过一定范围后,位宽的增宽并不会对处理

2017-11-18 12:37:12 2300

2300

钳位电路经常用于各种显示设备中。在示波器和雷达显示器中用钳位电路使扫描信号的直流分量得到恢复,以解决扫描速度改变时所引起的屏幕上图像位置移动问题。在电视系统中用钳位电路使全电视信号的同步脉冲顶端保持在固定的电压上,以克服由于失去直流分量或干扰等原因造成的电平波动,从而实现电视同步信号的分离。

2018-01-20 09:21:24 35174

35174

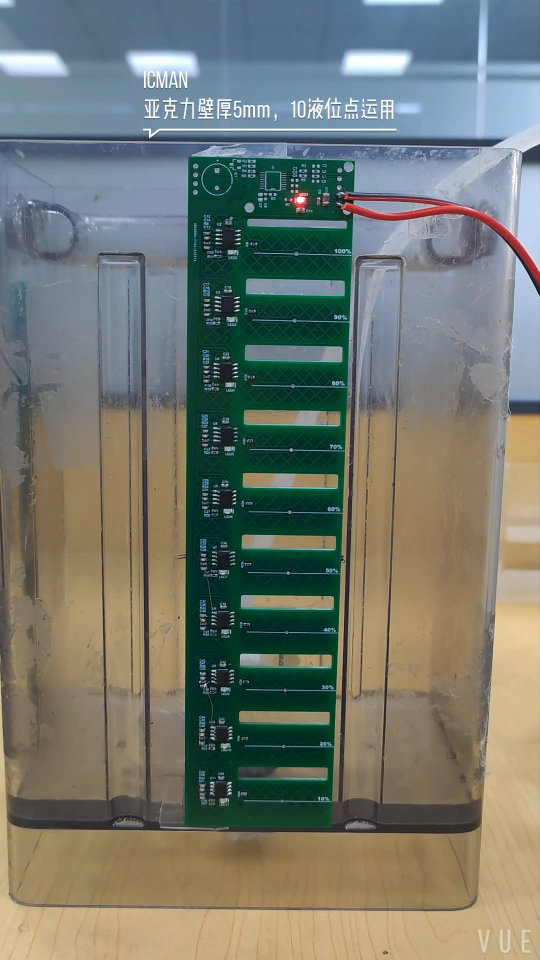

压力敏感传感器,将静压转换为电信号,再经过温度补偿和线性修正,转化成标准电信号(一般为4~20mA/1~5VDC)。其中液位传感器可将各种物位参数的变化转换成标准电流信号,远传至操作控制室,供二次仪表

2018-03-09 10:21:43 8766

8766 表示一个位。而曼彻斯特编码的信号在一个位时间内发生变化,因此需要两个时隙来表示一个位。曼彻斯特编码的优点是每个位都有一个信号边沿用来实现位同步(Self-clocking code)。但是曼彻斯特编码和非归零编码相比,在相同的位时间(位频率)时,位速率只能达到非归零码一半。

2018-03-13 12:30:00 1736

1736

CAN通讯中使用的是同步数据传输,CAN控制器在其通讯过程中会不停出现位同步的操作,但不同的数据通讯系统对位同步的要求是不同,为了满足其要求,我们必须更加深入的来探讨另一个概念叫位定时段的规格。位

2018-03-13 14:09:00 1750

1750

SRR 位应为隐性,以允许正在发送标准CAN 远程帧的节点发出显性RTR 位。SRR和lDE位之后是标识符的其余18位(扩展lD)及一个远程发送请求位。为使标准帧和扩展帧都能在共享网络上发送,应将29位扩展报文标识符拆成高11 位和低18 位两部分。

2018-03-15 14:27:30 8825

8825 基于CAN总线的液位控制装置的设计课程设计论文

2018-04-24 11:16:13 24

24 本文首先介绍了CAN总线仲裁是什么,其次介绍了CAN总线仲裁的示意图,最后详细的阐述了CAN总线位仲裁技术,具体的跟随小编一起来了解一下吧。

2018-05-07 14:27:26 17615

17615

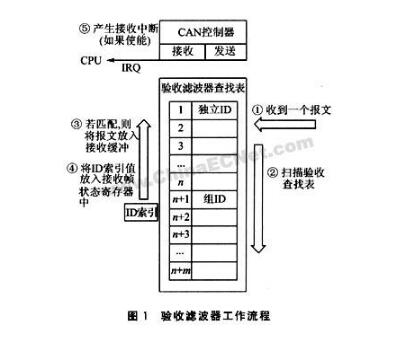

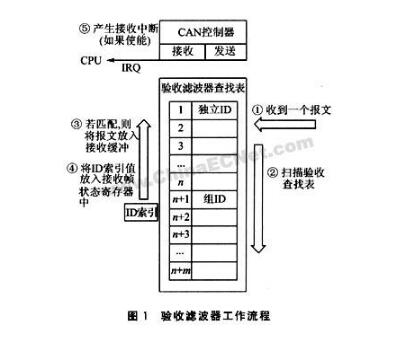

用来实现CAN总线协议。本文主要对CAN总线通信报文验收滤波、位定时与同步做了详细介绍,具体的跟随小编一起来了解一下。

2018-05-07 16:16:12 12146

12146

规定时间,会造成波形位宽增加,采样点取值不准确,波特率异常,出现大量错误帧,一直重发数据帧也会造成CAN总线通信瘫痪。

2018-09-22 08:51:00 21396

21396

因此,使用CAN总线的时候,发现位宽度有偏差,则需要对其程序中的位定时寄存器或者晶振进行修正。比如不要使用带小数点的晶振,如11.0592HZ。这样算出来的波特率肯定不准。不要使用陶瓷晶振,会有偏差超过1%的概率,即使重同步也会失败。

2019-03-14 16:33:12 28938

28938 8位MCU的编程方式非常简单,与CAN和CIP结合使用时甚至更加容易。当这些8位MCU能够提供足够的处理能力时,特别是针对远程节点的处理能力,便能够替代更昂贵且更难编程的16位MCU。

2019-12-16 17:55:49 3198

3198

CANOpen系列教程05_CAN总线同步与位填充、优先级的决定

2020-03-06 16:13:14 6880

6880 由于CAN协议使用非破坏性的位总线仲裁和显性应答位,信号从发送器传输到接收器再返回到接收器必须在一个位时间内完成。

2020-03-21 11:23:39 2992

2992 同步段是CAN总线位周期中每一位的起始部分。不管是发送节点发送一位还是接收节点接收一位都是从同步段开始的。但是由于发送节点和接收节点之间存在网络传输延迟以及物理接口延迟,发送节点发送一位之后,接收节点延迟一段时间才能接收到,因此,发送节点和接收节点对应同一位的同步段起始时刻就有一定的时延,记为。

2020-03-26 10:13:16 6991

6991

在数据通讯中最根柢的同步办法即是“位同步”(bit synchronization)或比特同步。比特是数据传输的最小单位。位同步(比特同步)是指接纳端时钟现已调整到和发送端时钟彻底相同,因而接纳端

2020-09-23 10:48:54 29173

29173

液位传感器是指把容器内的液位信号转化成开关信号或者电压电流信号,然后通过外部电路,直观地让测量者准确知道容器内液位情况。

2020-12-25 23:20:15 1194

1194 AD7779: 8通道、24位同步采样ADC

2021-03-21 16:03:43 38

38 UG-1304:评估AD7380 16位和AD7381 14位、2通道、同步采样、逐次逼近ADC

2021-03-22 19:18:51 8

8 LTC1407-1:串行12位/14位,3Msps同步采样ADC,带关断数据表

2021-04-27 12:38:49 11

11 UG-1615:4通道、4 MSPS、16位/14位/12位、双同步采样SAR ADC

2021-05-17 17:56:59 7

7 在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发同步,而且在获取祯同步、群同步及对接收的数字码元进行各种处理的过程中,也为系统提供了一个基准的同步时钟。

2021-05-28 11:20:23 4479

4479

CAN总线上日益增长的带宽需求。相比于CAN2.0主要有2点增强:将数据位段增加到最多64数据字节(CAN 2.0最大为8个数据字节)。标称位和数据位使用不同的比特率,标称位的比特率和CAN...

2021-10-29 11:21:11 19

19 GM8827C 实现27位RGB信号和3位控制信号 HS、VS、DE 的并串转化功能24 位 LVDS 发送器1 、产品概述本产品为一款多通道 LVDS 串行发送器,实现将 27 位 CMOS

2021-12-01 10:21:09 8

8 详细介绍CAN位知识

2022-06-29 14:33:19 0

0 将两个或是多个设备的全局时间进行同步,以保证这些CAN设备对总线上产生的CAN事件有相同的时间戳,这份听起来简单的工作实际操作起来却会花费大量的人工时间。自1980年代开始,克萨(Kvaser)就专注

2023-01-12 14:50:11 3165

3165 V850ES/GB1 VENUS 32位/16位CAN接口单片机硬件用户手册

2023-05-09 19:58:22 0

0 V850ES/GB1 VENUS 32位/16位CAN接口单片机硬件用户手册

2023-06-28 18:48:46 0

0 /S。对于 CAN 总线,一个位分为 4 段: ①、同步段(SS) ②、传播时间段(PTS) ③、相位缓冲段 1(PBS1) ④、相位缓冲段 2(PBS2) 这些段由 Tq(Time Quantum

2023-07-25 10:44:05 2922

2922

在离线分析的过程中,可能会对两个不同的信号进行时间上同步,本文以举例的形式介绍,如何使用 CANape 或者 vSignalyzer 对不同的信号进行时间同步。

2023-10-13 12:28:59 3117

3117

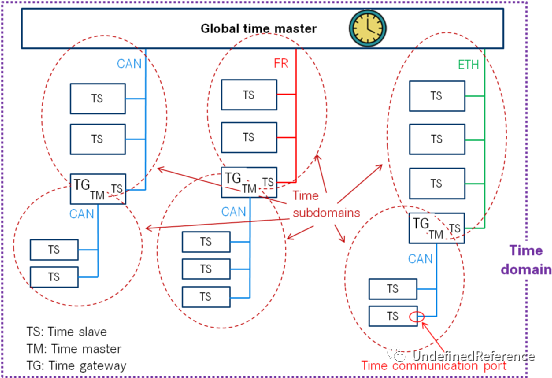

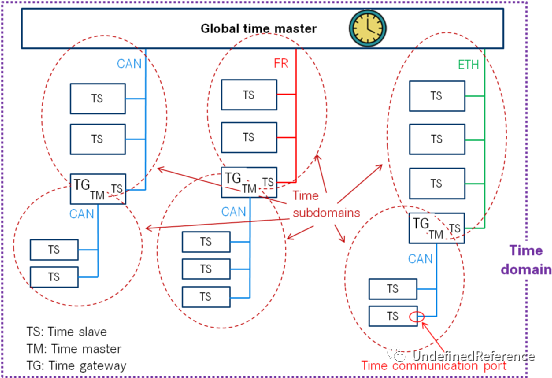

到各slave节点(TS),还可通过时间网关(TW)将时间同步到其他子网,以解决因各ECU节点的硬件时钟信号偏差、CAN总线传输延时如协议仲裁以及各ECU节点内的软件处理等原因导致的时间延迟。网络拓扑

2023-10-27 14:39:19 4636

4636

信号的电平和反向来表示数据的二进制位,具有自同步性和抗干扰能力强的特点。 在差分曼彻斯特编码中,每个数据位都被编码成两个时间间隔,分别称为一个时钟周期。其中,数据位为1时信号取反,数据位为0时信号保持不变。这样的编码方式使得在信号中始终存在电平的变化,

2023-11-22 16:32:33 9259

9259 一文档介绍本文将一步步介绍如何使用DSLogic逻辑分析仪采集并分析CAN/CAN-FD信号,因为CAN信号的测量和CAN-FD的大致一样,所以下文以CAN-FD举例,在有区别之处,将会做特别

2024-01-08 14:54:05 2997

2997

电子发烧友网站提供《ADSxx53双路高速16位、14位和12位同步采样模数转换器数据表.pdf》资料免费下载

2024-07-27 11:26:35 0

0 电子发烧友网站提供《ADSxx54双路高速16位、14位和12位同步采样模数转换器数据表.pdf》资料免费下载

2024-07-27 09:46:46 0

0 数字锁相环(DPLL)提取位同步信号的原理主要基于相位反馈控制系统,通过不断调整接收端时钟信号的相位,使之与发送端时钟信号的相位保持一致,从而实现位同步。以下是详细的原理说明:

2024-10-01 15:38:00 2564

2564 数字锁相环(DPLL)提取位同步信号的设置涉及多个关键步骤和组件的配置。以下是一个概括性的设置流程,以及各个步骤中需要注意的关键点:

2024-10-01 15:41:00 1756

1756 电子发烧友网站提供《CAN位时序参数计算器.pdf》资料免费下载

2024-10-11 09:55:31 1

1 32位硬件过滤器实例分析。推荐阅读:《CH32FV系列CAN设备过滤器配置》32位标识符列表32位标识符模式较16位更好理解,一个CAN_FxRx寄存器不再拆分,

2024-11-08 01:05:14 1158

1158

本文导读在CAN/CANFD通信系统中,波特率的稳定程度是由系统振荡器精度、PLL性能以及物理层传输特性共同影响的,波特率偏差可能会引入过多的重同步修正甚至导致采样点落在非预期位置,从而影响系统

2025-09-04 11:39:17 644

644

电子发烧友App

电子发烧友App

评论