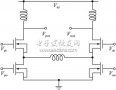

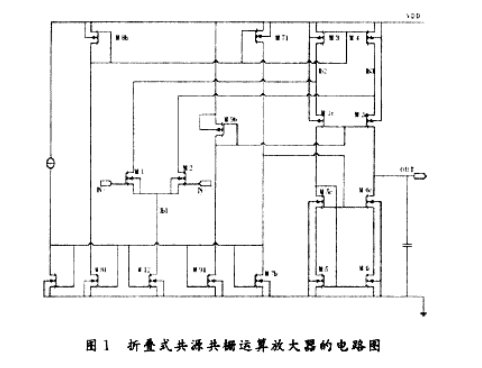

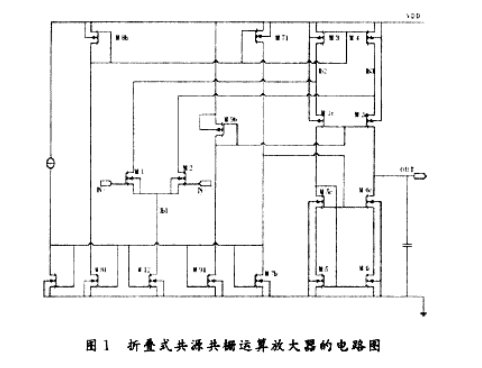

新型的复用型折叠式共源共栅运算放大器是从文献中折叠式共源共栅运算放大器的基础上改进而来。如图的复用型折叠式共源共栅运算放大器主电路

2012-03-08 10:12:03 4142

4142

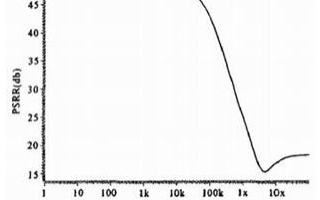

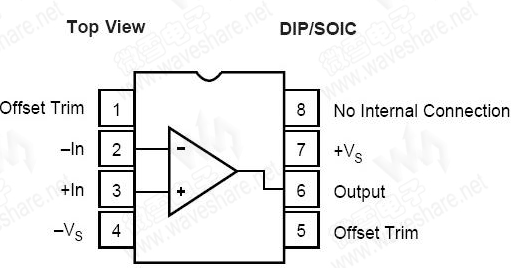

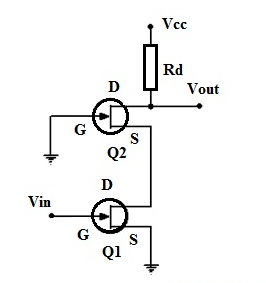

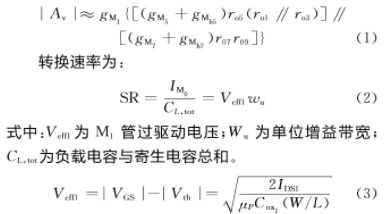

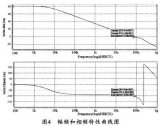

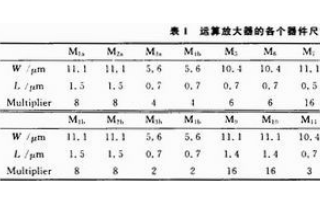

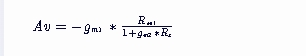

电流镜负载放大器是LDO线性稳压器中误差放大器的基本结构,如图1所示。VDD通过M3、M4,为输出端引入一个电流(go4+sCp4)VDD,通过M3、M1、M2,为输出端引入一个电流(go1+sCp1)VDD,则

2021-03-09 10:38:04 7018

7018

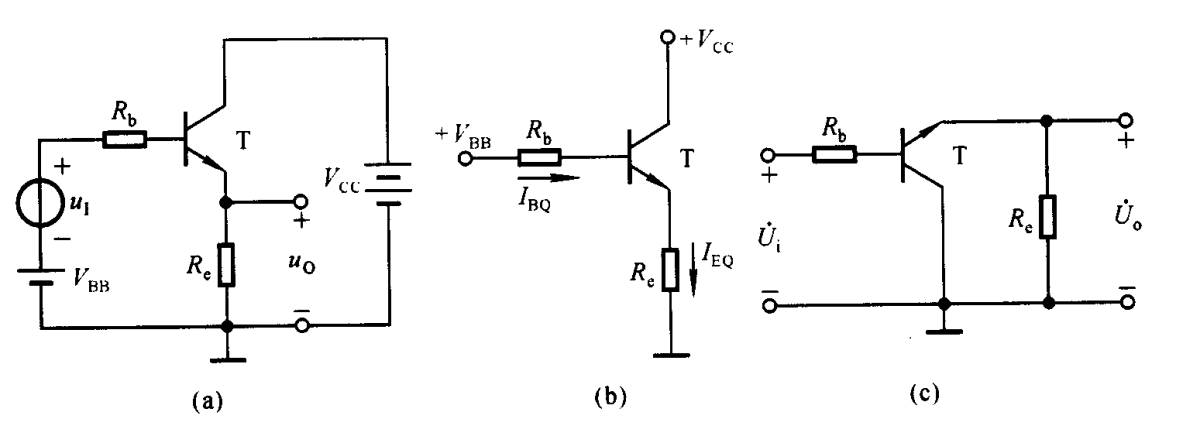

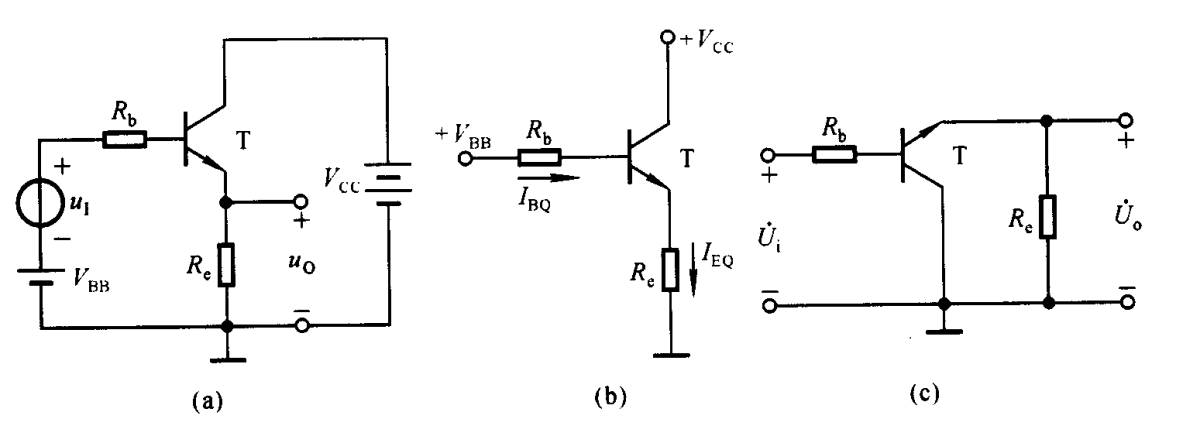

为了理解集成运算放大器里面输入级的共集--共基组合电路,这里给出共集电极电路和共基极电路的分析。

2023-02-23 10:39:26 5331

5331

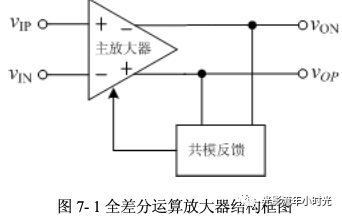

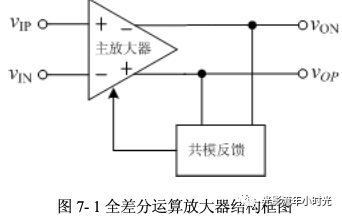

全差分运算放大器就是一种具有差分输入,差分输出结构的运算放大器。

2023-09-25 17:34:56 16365

16365

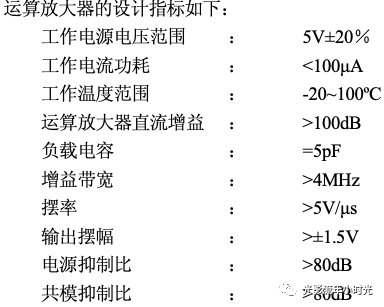

由于设计的运算放大器的电压增益在 100dB 以上,因此通过前面各种电路结构的分析, 可以选择折叠式共源共栅电路和一个简单放大器级联的结构来设计所需的电路。这样可以保证在较高的增益下,保证其他参数的实现。电路结构如图6- 19所示。

2023-09-25 17:37:26 4730

4730

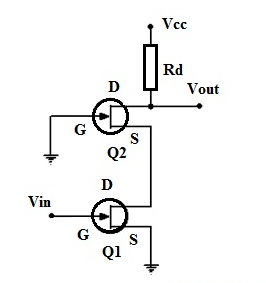

共源共栅放大器是一种特殊的放大器结构,它结合了共源放大器和共栅放大器的特点。在共源共栅放大器中,共源放大器作为主要增益单元,而共栅放大器则作为电流缓冲器。这种结构可以提高基础增益单元的阻值,从而提高放大器的增益和输出摆幅。

2024-02-19 16:15:57 8349

8349

信号,也可以输入共模信号,共模信号大部分来自噪声,最核心的愿景是:共模被抵消,差模被放大。四、输入电压范围(Vin或Vcm)运算放大器输入范围比较复杂,理论上来讲,同相端和反相端模拟输入在电源的正轨到

2021-12-07 07:00:00

描述差分运算放大器板运算放大器在配置为“差分”模式时可用于许多有趣的事情——包括模拟计算器、简单的平衡麦克风前置放大器和原始组件曲线跟踪器。

2022-06-28 07:20:14

运算放大器共模抑制(CMR)的问题出在哪里呢?我们该怎么去解决这个问题?

2021-04-07 06:55:35

信号,也可以输入共模信号,共模信号大部分来自噪声,最核心的愿景是:共模被抵消,差模被放大。四、输入电压范围(Vin或Vcm)运算放大器输入范围比较复杂,理论上来讲,同相端和反相端模拟输入在电源的正轨到

2021-08-25 07:00:00

运算放大器有哪几类?折叠式共源共栅全差分运算放大器会受到哪些影响?

2021-04-07 06:29:07

RF设计领域,回归到了全差分结构,也开启了在差分信号链接口中的新应用领域。如何得心应手地应用运算放大器,快速、准确地设计满足需求的电路系统,是工程师们必须认真面对的问题。本书出自全球领先的半导体公司

2017-06-09 17:38:49

非ppm放大器类型运算放大器的误差源输入共模抑制和偏置误差

2021-02-05 06:17:26

VOUT下限为50 mV。显然,给定运算放大器的内部设计会影响该输出共模动态范围,必要时,器件本身的设计应当最大程度地减小VSAT(HI)和VSAT(LO),以便实现最大输出动态范围。某些类型的运算放大器

2014-08-13 15:34:22

为50 mV。 显然,给定运算放大器的内部设计会影响该输出共模动态范围,必要时,器件本身的设计应当最大程度地减小VSAT(HI)和VSAT(LO),以便实现最大输出动态范围。某些类型的运算放大器就采用

2018-09-21 14:50:51

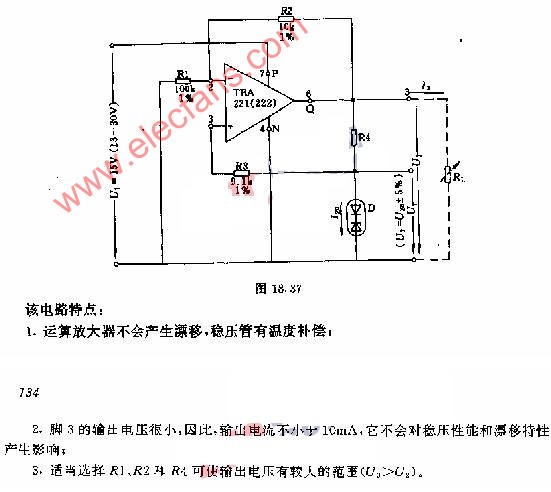

采用运算放大器的基准电压源

2019-10-29 09:01:22

这种全差分放大器能不能使用G=+1高速运算放大器作为buffer使用,增加AD8132的负载能力附件无标题.jpg84.1 KB

2019-01-15 10:43:40

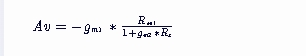

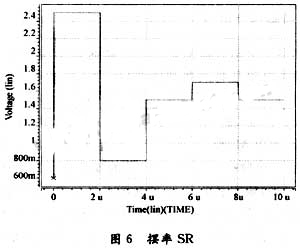

尾电流源架构,运算放大器主体部分单条支路上多达6个晶体管,造成偏置困难、工作不稳定的问题。因此,必须采用折叠式输入设计,本团队对运算放大器主体部分做了下图改进。

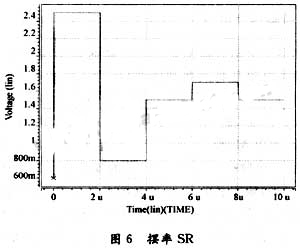

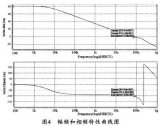

5.4 Cascode补偿提高带宽

2023-09-01 13:42:42

双电源方案,但是双电源方案在实际操作中很麻烦,也容易出错,所以需要找一个单电源供电的差分运算放大器电路。实现方案INA321是一款既可以双电源供电又可以单电源供电的芯片。基本结构很简单,如下图所示...

2021-11-11 08:07:04

最近在设计全差分折叠型共源共栅运放的时候,有一个问题想不明白,加入偏置电压后,调节管子让每个管子都处于饱和状态,并且输出处在了VDD/2。但是我发现只要偏置电压改变一点点哪怕1mv,静态工作点就会有很大的改变,这是为什么呢,好奇怪,有没有老哥为我解惑

2022-09-27 00:29:12

也没有同时流过两个R2电阻,所以放大器A1和A2将作为单位增益跟随器(缓冲器)工作。由于放大器A1和A2的输出端的输入电压在三个电阻器网络上出现差异,只需改变R1的值就可以改变电路的差分增益。差分运算放大器

2020-12-30 09:18:53

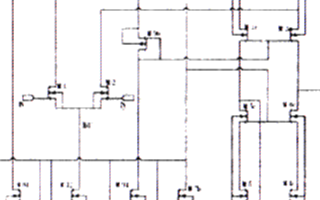

是一种广泛应用的运放结构。 由于所设计的电路应用于电源芯片系统中,基于速度等方面综合考虑,选择的是一个折叠式共源共栅运算放大器,另外由于运放在基准中是用作负反馈,所以选用单端输出的折叠运放。具体电路如下

2018-10-09 14:42:54

DC2319A-A,LTC6363的演示电路,是一款低功耗,低噪声差分运算放大器,具有轨到轨输出摆幅和良好的直流精度。放大器可以被配置为处理全差分输入信号或将单端输入信号转换为差分输出信号。 DC2319A的差分输出可配置一阶RC网络,以驱动ADC的差分输入

2019-05-17 09:11:23

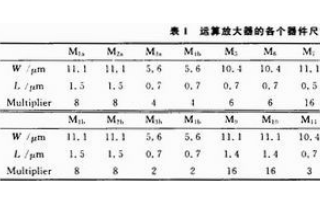

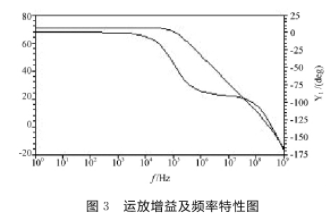

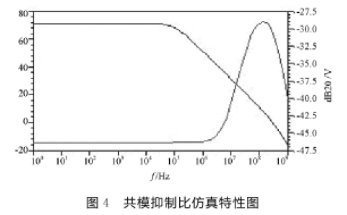

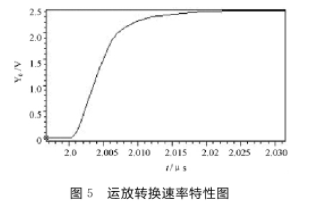

本文介绍的运放是一种采用TSMC 0.18 μm Mixed Signal SALICIDE(1P6M,1.8V/3.3V)CMOS工艺的折叠共源共栅运放,并对其进行了DC,AC及瞬态分析,最后与设计指标进行比较。

2021-04-14 06:59:22

TI高精度实验室-运算放大器-第七节-共模抑制和电源抑制抑制可能是一件好事,特别是在共模或电源电压错误的情况下。 本系列视频介绍了如何改变运算放大器的共模电压或电源电压,从而在交流和直流两端引入误差

2021-12-30 06:50:21

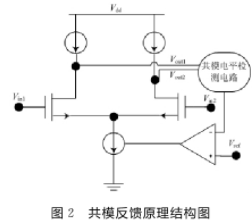

如何设计用于运算放大器的共模反馈电路?共模反馈电路的设计要点有哪些?全差分运算放大器的共模反馈原理是什么?

2021-04-20 06:17:09

共源共栅电感的工作机理是什么?怎么实现共源共栅CMOS功率放大器的设计?

2021-06-18 06:53:41

本文设计的带共模反馈的两级高增益运算放大器结构分两级,第一级为套筒式运算放大器,用以达到高增益的目的;第二级采用共源级电路结构,以增大输出摆幅。另外还引入了共模反馈以提高共模抑制比。

2021-04-14 06:55:14

本文设计的带共模反馈的两级高增益运算放大器结构分两级,第一级为套筒式运算放大器,用以达到高增益的目的;第二级采用共源级电路结构,以增大输出摆幅。另外还引入了共模反馈以提高共模抑制比。该方案不仅

2021-04-22 06:08:31

求微弱电流检测用的共模电压范围最大值大于65V的运算放大器或仪表放大器

2023-11-14 07:21:08

用于精密放大器的匹配电阻网络适用于全差分运算放大器,配置为VOUT / VIN = 0.2

2019-11-06 08:53:34

全差分运算放大器能像一般运算放大器一样设计加法器吗?

2024-08-09 06:26:00

折叠共源共栅比较器怎么修改为迟滞比较器

2021-06-24 07:36:52

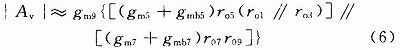

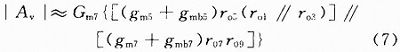

怎么设计一种单级全差分增益增强的折叠共源共栅运算放大器?

2021-04-20 06:26:29

CMOS运算放大器结构具有哪些特点?如何去设计CMOS运算放大器?怎样对CMOS运算放大器进行仿真测试?

2021-04-21 07:21:39

分析了准浮栅晶体管PMOS 的工作原理、电学特性和等效电路,设计了一种电路结构简单的共模反馈电路(CMFB),实现了一个低压低功耗的差分运算放大器。采用Chrt0.35umCMOS 工艺

2009-11-27 11:39:23 8

8 本文设计了一种低压低功耗CMOS 折叠-共源共栅运算放大器。该运放的输入级采用折叠-共源共栅结构,可以优化输入共模范围,提高增益;由于采用AB 类推挽输出级,实现了全摆幅输

2009-12-14 10:37:19 30

30 设计了用于高速高分辨率ADC 的CMOS 全差分运算放大器,采用套筒式级联增益自举电路,达到高增益带宽且低功耗。在3.3V 电源电压下,用TSMC 0.35μmCMOS 工艺模型,通过Cadence 软件Spectre

2009-12-14 11:12:54 46

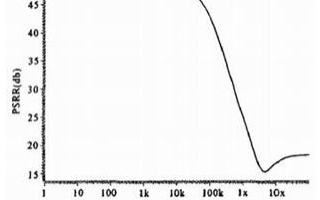

46 LDO 线性稳压器中高性能误差放大器设计孙毛毛 冯全源摘要:本文设计了一个具有高PSRR 性能的共源共栅差分运算跨导放大器。本文设计的误差放大器为带共源共栅电流镜负

2010-02-06 10:39:39 55

55 设计了一种用在高精度音频Σ-Δ A/D转换器中的高增益CMOS全差分运算放大器。该运算放大器采用了套筒式共源共栅结构和开关电容共模反馈电路。通过分析和优化电路性能参数,实现了

2010-07-29 17:23:00 51

51 折叠式共源共栅结构在折叠处引进的电流源降低了输出电阻,从而使增益大幅度降低。针对这一缺陷,论文提出的设计思路是用电流镜代替折叠式,避免输出电阻的下降,从而使

2010-07-30 18:09:08 23

23

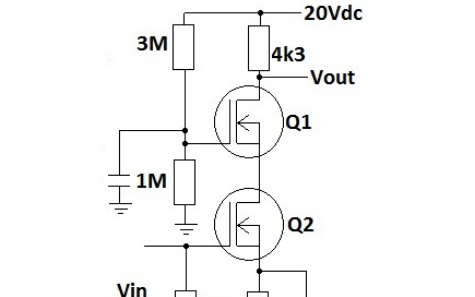

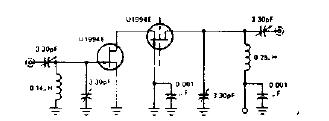

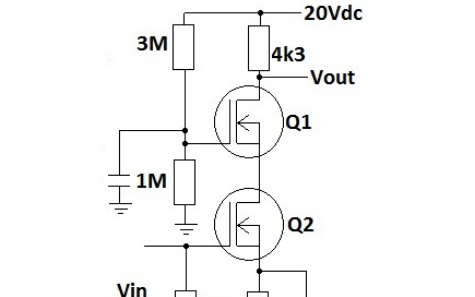

80MHz共源共栅放大器电路图

2009-04-08 09:10:10 2058

2058

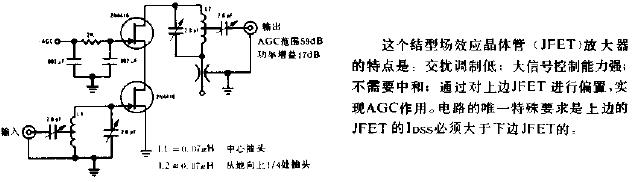

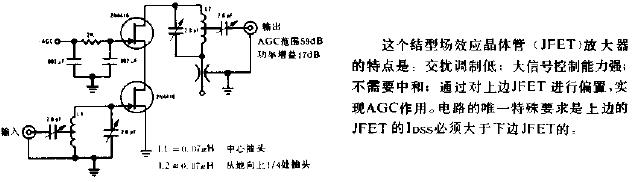

200MHz共源共栅放大器电路图1

2009-04-08 09:12:49 1839

1839

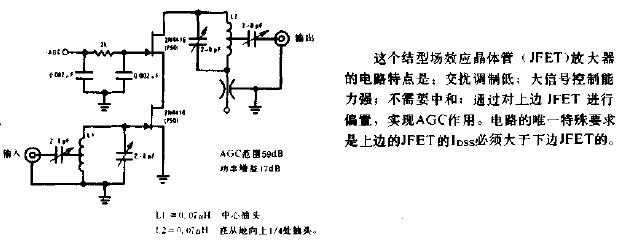

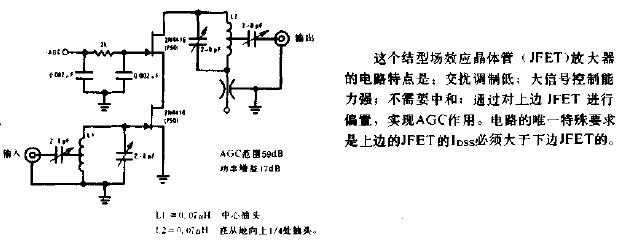

200MHz共源共栅放大器电路图2

2009-04-08 09:13:12 1252

1252

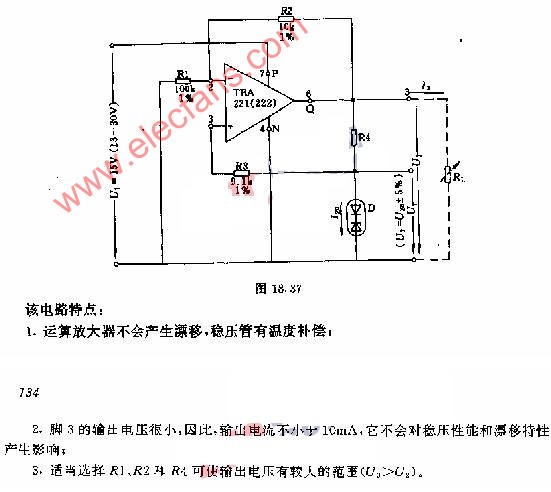

采用运算放大器的基准电压源电路

2009-05-12 22:56:49 5850

5850

0.6μm CMOS工艺全差分运算放大器的设计

0 引言 运算放大器是数据采样电路中的关键部分,如流水线模数转换器等。在此类设计中,速度和精度是两个

2009-12-08 17:19:51 2085

2085 折叠共源共栅运算放大器原理及设计

1 引言

本文介绍的运放是一种采用TSMC 0.18 μm Mixed Signal SALICIDE(1P6M,1.8V/3.3V)CMOS工艺的折叠共源共栅运放,并对其进行了DC

2010-03-12 15:05:24 12904

12904

随着集成电路技术的不断发展,高性能运算放大器广泛应用于高速模/数转换器(ADC)、数/模转换器(DAC)、开关电容滤波器、带隙电压基准源和精密比较器等各种电路系统中,成为模

2011-06-07 16:02:34 52

52 本文设计了一种采用增益增强结构的带开关电容共模反馈的折叠式共源共栅跨导运算放大器,可用于流水线结构的A/D中。出于对性能及版图因素的考虑,采用了单端放大器作为增益提高

2011-06-29 09:45:09 12396

12396

电子发烧友为您提供了李福乐的全差分运算放大器电子书,介绍了全差分 运算放大器 的基本知识,如对于全差分放大器,其输出是差分方式且输出共模电压可以独立于差分电压设置。对

2011-07-18 16:54:32 0

0 设计并讨论了一种高单位增益带宽cmos全差分运算放大器。由于折叠共源共栅结构电路具有相对高的单位增益带宽以及开关电容共模反馈电路稳定性好、对运放频率特性影响小等优点,故

2011-07-31 21:51:57 117

117 采用台积电0.18umCMOS工艺设计了中心频率在5.25GHz的功率放大器,其中使用了共源共栅电感对功率放大器电路进行改进,在一定程度上提高了功率放大器的效率

2011-08-25 14:13:04 5621

5621

给出了两种应用于两级CMOS 运算放大器的密勒补偿技术的比较,用共源共栅密勒补偿技术设计出的CMOS 运放与直接密勒补偿相比,具有更大的单位增益带宽、更大的摆率和更小的信号建立时

2012-02-15 11:09:50 78

78 本文设计了一种用于高速ADC中的高速高增益的全差分CMOS运算放大器。主运放采用带开关电容共模反馈的折叠式共源共栅结构,利用增益提高和三支路电流基准技术实现一个可用于12~14

2012-06-06 13:08:28 42

42 设计了一种用于高速ADC中的高速高增益的全差分CMOS运算放大器。主运放采用带开关电容共模反馈的折叠式共源共栅结构,利用增益提高和三支路电流基准技术实现一个可用于12~14 bit精度

2012-06-07 14:21:36 38

38 结合模/数转换器工作原理和VLSI设计方法,分析和设计了一种应用于ADC的高增益运算放大器。由于套筒式共源共栅结构电路具有增益高、功耗低、频率特性好的优点,故采用套筒式共源

2013-09-25 16:12:03 24

24 介绍了运算放大器的共模电压的输入输出范围和差分电压输入范围。

2013-09-26 14:47:12 38

38 共源共栅跨导运算放大器的设计

2017-03-05 15:00:06 10

10 的。 这种灵活性允许在 CMOS

工艺中发展高性能无缓冲运算放大器。 目前, 这样的放大器已被广泛用于无线电通信的集成电路中。 介绍了一种折叠共源

共栅的运算放大器, 采用 TSMC 0. 18 混合信号双阱 CMOS 工艺库, 用 HSpice W 2005. 03 进行设计仿真, 最后与设计指标

2022-07-08 16:32:35 23

23 基于 chartered 0.35 m 工艺,采用 PMOS 管作为输入管的折叠式共源共栅结构,设计了一种采用增益提高技术的两级运算放大器。利用 Cadence 公司的spectre 对电路进行仿真

2017-11-04 10:40:17 30

30 两级,第一级为套筒式运算放大器,用以达到高增益的目的;第二级采用共源级电路结构,以增大输出摆幅。另外还引入了共模反馈以提高共模抑制比。

2017-12-06 04:28:28 27182

27182

引起A/D转换器的非线性。与单端输出的运算放大器相比,全差分运算放大器能提供更大的输出电压摆幅,并具 有不易受共模噪声影响、更高的线性度、减少偶次谐波干扰以及偏置电路更简单等优点。

2018-06-10 14:20:00 41721

41721

共模反馈电路是全差分运放的一个不可或缺的部分。本文的主运放选用动态开关电容共模反馈,如图2所示。选用这种结构的原因,一方面是这种共模反馈电路可节省功耗;另一方面是其共模电压取样电路不会限制运放的输出

2018-06-08 08:59:00 11077

11077

LME497是一种超低失真,低噪声,高摆率全差分运算放大器优化和完全指定的高性能,高保真应用。

2018-05-16 15:52:03 16

16 。放大器的输出较容易实现轨对轨, 但在输入端实现轨对轨是比较复杂的, 原则上只能是折叠式共源共栅结构才能使输入端包含电源电压的轨, 这种技术是实现所有轨对轨输入放大器的基础。

2018-12-18 09:15:00 9242

9242

CMOS运算放大器的基本分类1、单级差分运算放大器(电流镜做负载的差分放大器)2、套筒式共源共栅CMOS运算放大器(单级)3、折叠共源共栅CMOS运算放大器(单级)4、两级CMOS运算放大器

5、Rail-to-Rail CMOS运算放大器6、Chopper CMOS运算放大器 运放的概念、组成与电路结构

2018-11-07 10:10:57 98

98 本文提出了一款基于CMOS工艺的全差分轨至轨折叠型共源共栅结构AB类音频功率放大器产品的设计,其系统包含有偏置模块、温度保护模块、控制模块及核心功率运算放大器模块。整个系统具有较大的共模信号输入范围

2018-12-25 17:17:56 2

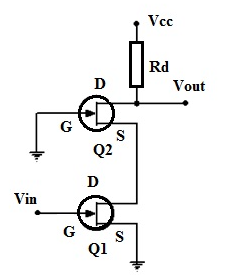

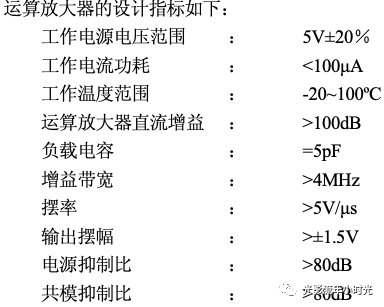

2 如图是一个共源共栅放大器,同时也可以看作双栅场效应管。请问:1.这样结构的电路为什么会产生密勒效应呢?

2018-12-29 09:27:05 0

0

CMOS 运算放大器是 CMOS 模拟集成电路的最重要的模块,它的特性决定了模拟集成电路的特性。复杂的 CMOS 运算放大器的基础是简单的单级放大器。本章将介绍常用的单级共源放大器、共栅放大器、源跟随器、共源共栅放大器。

2019-05-14 08:00:00 2

2 运算放大器是模拟电路中最重要和最通用的单元电路之一,同时也是许多模拟系统和数/模混合信号系统中的一个完整模块。运放具有足够大的正向增益,当加负反馈时,闭环传输函数与运算放大器的增益几乎无关。利用这个

2020-01-25 16:50:00 11760

11760

已有文献[2]采用PMOS差分对来实现电源电压为1V的运算放大器,但由于Vt,PMOS的典型值为-0.75V,使得前置反馈电路的工作电平范围为1-0.15V,几乎涵盖整个共模电平范围,运算放大器

2020-07-24 10:11:29 3189

3189

随着集成电路技术的不断发展,高性能运算放大器广泛应用于高速模/数转换器(ADC)、数/模转换器(DAC)、开关电容滤波器、带隙电压基准源和精密比较器等各种电路系统中,成为模拟集成电路和混合信号

2020-07-24 11:32:27 3485

3485

OPA627差分运算放大器在精密FET运算放大器中提供了新的性能水平。与流行的OPA111运算放大器相比,OPA627具有更低的噪声,更低的失调电压和更高的速度。OPA627在广泛的精密和高速模拟电路中非常有用。

2020-10-27 10:32:03 32534

32534

MT-041:运算放大器输入和输出共模与差分电压范围

2021-03-21 10:37:32 5

5 本文介绍了一种折迭共源共栅的运算放大器,采用TSMC0.18混合信号双阱CMOS工艺库,用HSpiceW-2005.03进行设计仿真,最后

2021-04-16 09:39:53 6643

6643

101:差分运算放大器过时数据表

2021-05-21 08:38:53 1

1 电子发烧友网站提供《差分运算放大器板.zip》资料免费下载

2022-07-04 10:27:11 1

1 电子发烧友网站提供《全差分运算放大器开源分享.zip》资料免费下载

2022-07-26 15:06:11 5

5 全差分运放相较于通用的标准运放,其最突出的特点为输出为差分信号,且有Vocm端口用于控制输出共模电压。图1全差分运放与通用标准运放对比[1]典型的差分放大器结构简图如图所示,其内部包含两个放大器

2023-05-08 09:59:40 7549

7549

单级,共源共栅和调节型共源共栅型放大器的优缺点是什么? 放大器是电子电路中最基础也是最重要的组成部分之一。设计一种适当的放大器电路是电路设计者必不可少的技能。共源共栅和调节型共源共栅型放大器

2023-09-18 15:08:23 4997

4997 为什么共源级和共栅级放大器的输出阻抗是一致的? 共源级放大器和共栅级放大器是两种主要的放大器电路。在这两种电路中,输出阻抗是不同的。但是,在某些情况下,这两种放大器电路的输出阻抗可以相同。本文将

2023-09-20 17:05:16 3151

3151 年撰写的一篇文章中使用了tern共源共栅,讨论的是稳压器应用。他们设计了两个三极管的共源共栅,其中第一个三极管采用共阴极设置,下一个三极管采用公共栅极代替五极管。因此,它的名称可以假设为级联三极管的减少,其具有像五极管一样的相关特性。 那么,共源共栅放大器工作原理究竟是怎样的

2023-09-28 11:23:20 6757

6757

运算放大器采用差分放大是因为差分放大器具有以下几个优点

2024-01-04 18:16:18 1888

1888 电子发烧友网站提供《LME49724全差分运算放大器数据表.pdf》资料免费下载

2024-06-15 09:23:00 0

0 共源共栅放大器是一种特殊的场效应晶体管(FET)放大器,它结合了共源放大器和共栅放大器的优点。在这种放大器中,一个晶体管作为共源放大器,另一个晶体管作为共栅放大器。这种放大器具有高增益、低噪声、高

2024-09-27 09:38:42 2192

2192 共源共栅放大器的增益是一个相对复杂的参数,它受到多个因素的影响,包括晶体管的跨导、负载电阻、源电阻、以及电路的具体设计等。因此,无法直接给出一个具体的增益值,而需要根据具体的电路情况来计算

2024-09-27 09:45:07 2171

2171

共源共栅放大器(Cascode)是一种在集成电路设计中常用的放大器结构,它结合了共源放大器和共栅放大器的优点,具有高输入阻抗、高输出阻抗和较大的电压摆幅。然而,在实际应用中,共源共栅放大器的增益

2024-09-27 09:46:38 1932

1932 共源共栅放大器(Cascode amplifier)是一种在模拟电路设计中常用的放大器结构,它结合了共源(Common Source,CS)和共栅(Common Gate,CG)两种放大器的优点

2024-09-27 09:48:12 4243

4243 折叠共源共栅放大器(Folded Cascode Amplifier)是一种在模拟集成电路设计中常用的放大器结构,它结合了共源(Common Source)和共栅(Common Gate)放大器

2024-09-27 09:50:03 4777

4777 运算放大器的共模输入电压(Common Mode Input Voltage,简称CMVIN或VICM)是电子工程中的一个重要概念,它关系到运算放大器的性能以及信号处理的质量。

2024-10-18 18:02:17 6310

6310

![]()

![]()

电子发烧友App

电子发烧友App

评论