共源极放大器电路及原理

2009-12-08 09:09:28 20965

20965

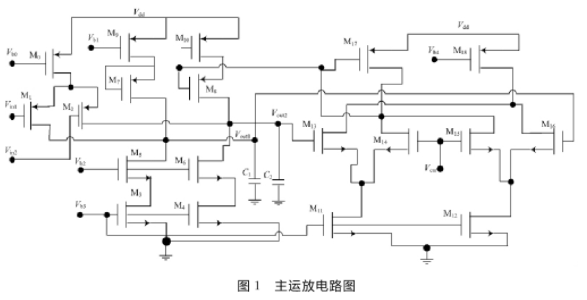

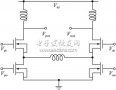

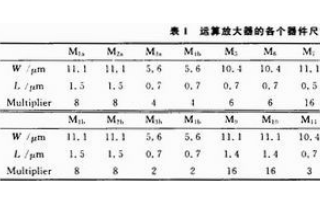

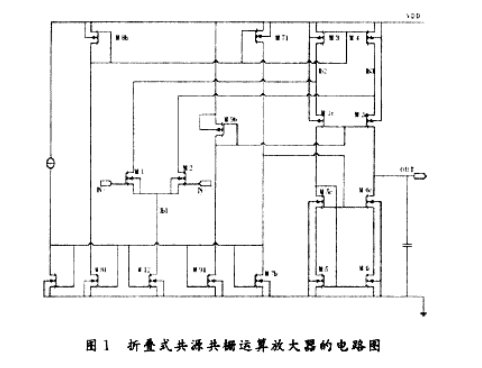

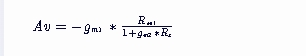

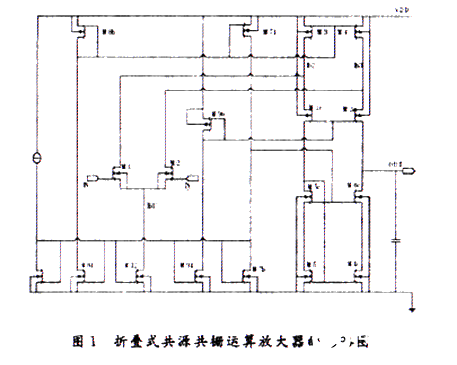

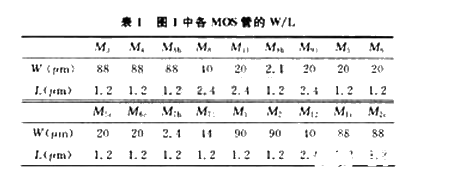

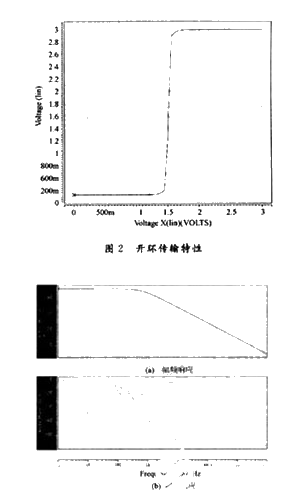

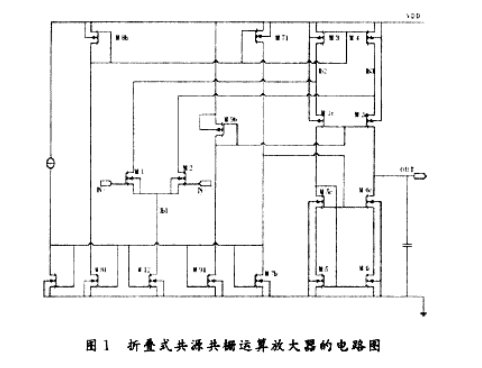

新型的复用型折叠式共源共栅运算放大器是从文献中折叠式共源共栅运算放大器的基础上改进而来。如图的复用型折叠式共源共栅运算放大器主电路

2012-03-08 10:12:03 4142

4142

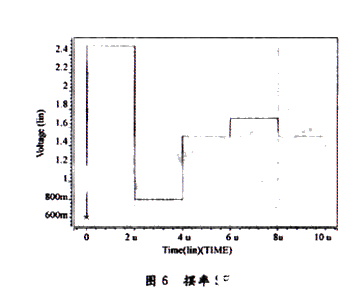

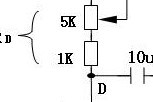

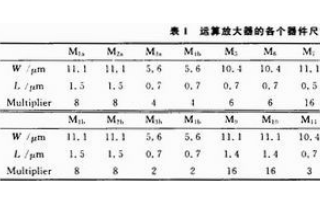

根据需要,本文设计运算放大器需要在较低的电压下能有大的转换速率、快的建立时间,同时要折衷考虑增益与频率特性及共模抑制比(CMRR)和电源抑制比(PSRR)等性能。

2020-12-18 12:10:00 15823

15823

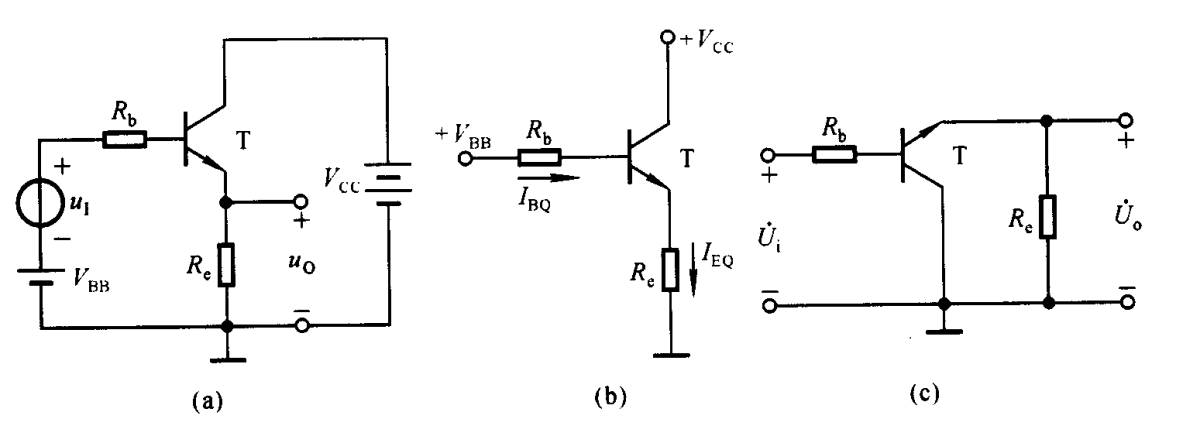

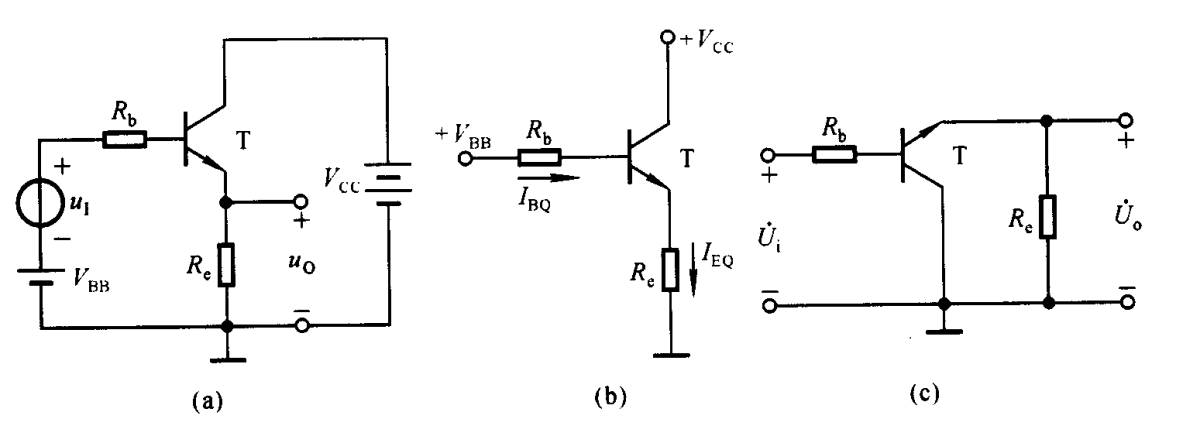

为了理解集成运算放大器里面输入级的共集--共基组合电路,这里给出共集电极电路和共基极电路的分析。

2023-02-23 10:39:26 5331

5331

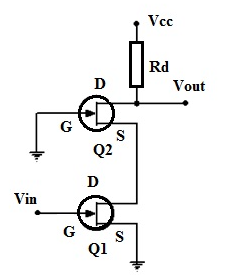

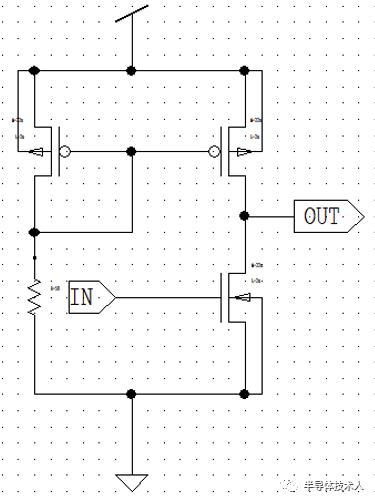

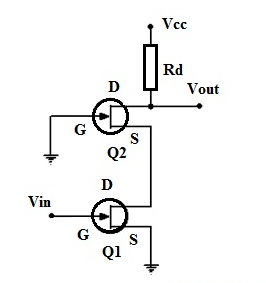

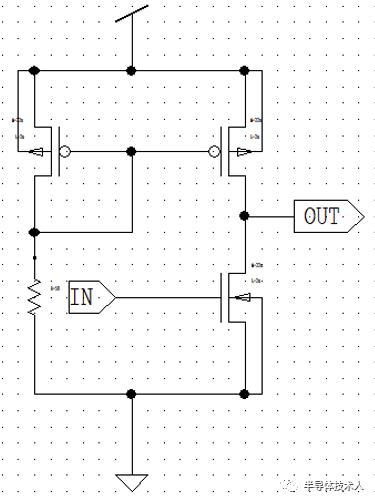

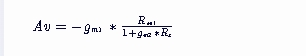

共源共栅放大器是一种特殊的放大器结构,它结合了共源放大器和共栅放大器的特点。在共源共栅放大器中,共源放大器作为主要增益单元,而共栅放大器则作为电流缓冲器。这种结构可以提高基础增益单元的阻值,从而提高放大器的增益和输出摆幅。

2024-02-19 16:15:57 8349

8349

CMOS 的输入级则提供高达 5uV/ºC 的失调漂移。在 CMOS 输入运算放大器中实现极低失调的挑战在于阀值电压之间的差异(输入差分对)以及栅…

2022-11-21 07:45:46

概述:AN4558是一款双运算放大器,一般常应用于VCD和DVD视盘机中,它采用双列8脚和圆筒8脚两种封装工艺,双宽带运放,电源电压±18V,差分输入电压±30V,共模输放电压±15V。

2021-04-08 07:24:55

运算放大器是线性器件,具有几乎理想的DC放大所需的所有特性,因此广泛用于信号调理,滤波或执行数学运算(如加,减,积分和微分)。一个运算放大器,或简称为运算放大器,从根本上是一个电压放大装置设计成

2020-12-25 09:05:21

运算放大器共模抑制(CMR)的问题出在哪里呢?我们该怎么去解决这个问题?

2021-04-07 06:55:35

运算放大器有哪几类?折叠式共源共栅全差分运算放大器会受到哪些影响?

2021-04-07 06:29:07

用于衡量运算放大器对作用在两个输入端的相同直流信号的抑制能力。CMRDC可以用共模电压范围(CMVR)与该范围内对应的输入失调电压变化的峰峰值进行计算:3. 交流共模抑制 (CMRAC) CMRAC用于

2009-09-25 10:42:49

非ppm放大器类型运算放大器的误差源输入共模抑制和偏置误差

2021-02-05 06:17:26

VOUT下限为50 mV。显然,给定运算放大器的内部设计会影响该输出共模动态范围,必要时,器件本身的设计应当最大程度地减小VSAT(HI)和VSAT(LO),以便实现最大输出动态范围。某些类型的运算放大器

2014-08-13 15:34:22

为50 mV。 显然,给定运算放大器的内部设计会影响该输出共模动态范围,必要时,器件本身的设计应当最大程度地减小VSAT(HI)和VSAT(LO),以便实现最大输出动态范围。某些类型的运算放大器就采用

2018-09-21 14:50:51

前级用运算放大器AD845,输出正弦波(10K-300K)电压0-5V峰值,连接AD734A芯片,中间想加一个双运算放大器作为电压跟随器,选择什么型号的双运算放大器?

2018-10-11 09:50:22

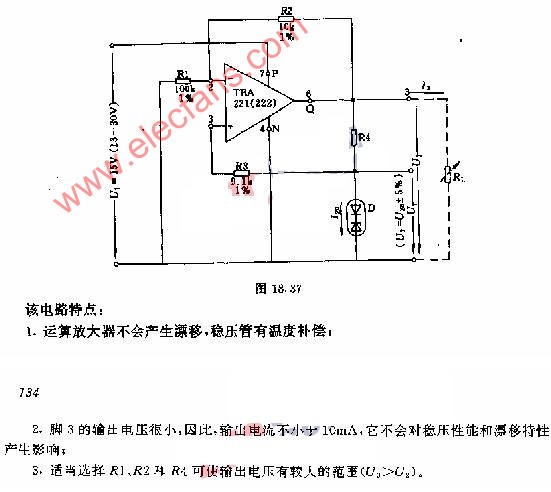

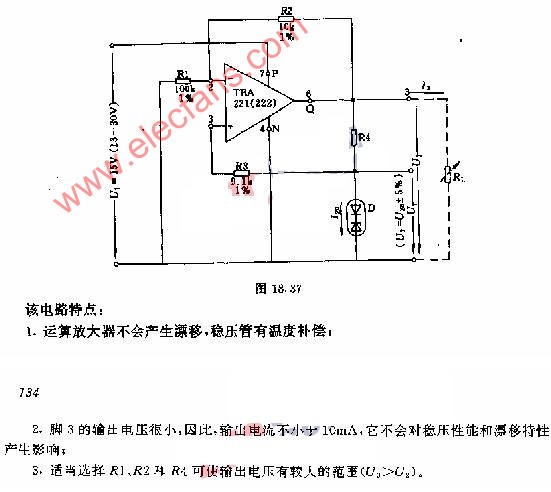

采用运算放大器的基准电压源

2019-10-29 09:01:22

采用运算放大器的基准电压源

2019-10-31 09:02:27

特征除非另有说明,否则在TA=+25°C,VS=+5V,RL=25kΩ时连接至VS/2。应用程序信息OPA336系列运算放大器采用最先进的0.6微米CMOS工艺制造。它们具有单位增益稳定,适用于广泛

2020-09-27 17:38:18

%

工作温度:①25℃,②0℃至50℃,③-20℃至85℃,④-40℃至+125℃

详细指标要求:

4.作品特色

本作品在差分输入单端输出的共源共栅运算放大器基本架构的基础上,大胆尝试了一种新的设计架构

2023-09-01 13:42:42

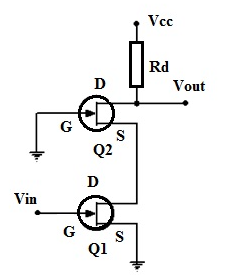

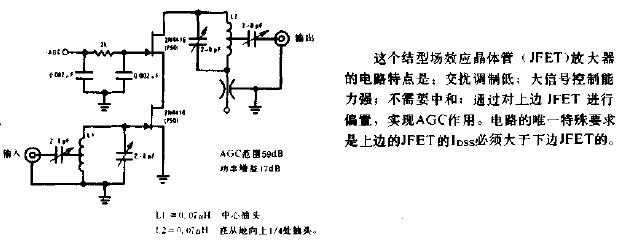

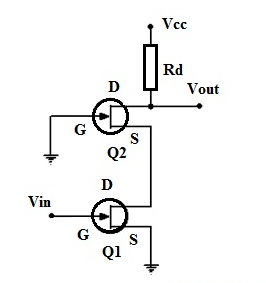

B与水平轴交叉。直流负载线上Q点的实际位置通常位于负载线的中间中心点(用于A类操作),并由Vg的平均值确定,因为JFET是耗尽模式设备。像双极共射极放大器一样,共源JFET放大器的输出与输入信号异相

2020-11-03 09:34:54

时。特别是在CMOS技术成熟后,模拟运算放大器有了质的飞跃。一方面解决了低功耗的问题;另一方面,通过使用混合模拟和数字电路技术解决了直流小信号的直接处理问题。 经过多年的发展,模拟运算放大器技术已经

2023-02-14 15:40:39

。通常,单电源工作与低压工作相同,将电源由±15V或±5V变为单5V或3V,缩小了可用信号范围。因此,其共模输入范围、输出电压摆幅、CMRR、噪声及其它运算放大器的限制变得非常重要。在所有工程设计中

2020-11-20 10:03:54

就属于这种情况。根据前面的假设条件,在电阻失配的情况下,这个电路就不再是一个真正的差分放大器,VO会随着共模分量而变化。 小结 运算放大器,如果选取恰当的外部元件,它能够构成各种运算电路,如放大、加、减、微分和积分等运算电路。运算放大器实现数学运算的能力,是将高增益与负反馈结合起来的结果。

2021-02-20 16:21:09

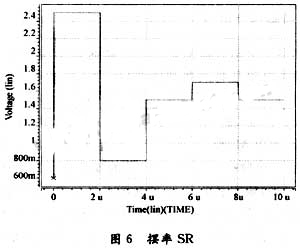

本文介绍的运放是一种采用TSMC 0.18 μm Mixed Signal SALICIDE(1P6M,1.8V/3.3V)CMOS工艺的折叠共源共栅运放,并对其进行了DC,AC及瞬态分析,最后与设计指标进行比较。

2021-04-14 06:59:22

求分享一种基于标准CMOS工艺设计的电源电压低至0.9V的运算放大器

2021-04-08 06:02:52

TI高精度实验室-运算放大器-第七节-共模抑制和电源抑制抑制可能是一件好事,特别是在共模或电源电压错误的情况下。 本系列视频介绍了如何改变运算放大器的共模电压或电源电压,从而在交流和直流两端引入误差

2021-12-30 06:50:21

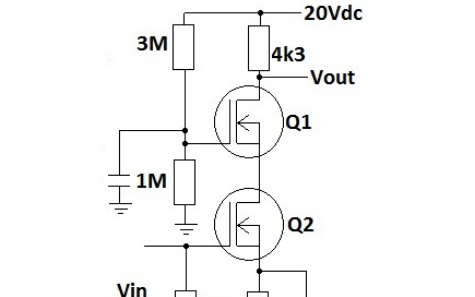

我有一个源极跟随器(共漏极)配置的NMOS晶体管,但具有从输出到输入的反馈。它被用作功率级,因为负载的功率很高。如何用运算放大器代替电压源?

2024-03-01 07:26:44

如何设计用于运算放大器的共模反馈电路?共模反馈电路的设计要点有哪些?全差分运算放大器的共模反馈原理是什么?

2021-04-20 06:17:09

共源共栅电感的工作机理是什么?怎么实现共源共栅CMOS功率放大器的设计?

2021-06-18 06:53:41

实现低于 1uV/ºC 的失调漂移,而 CMOS 的输入级则提供高达 5uV/ºC 的失调漂移。在 CMOS 输入运算放大器中实现极低失调的挑战在于阀值电压之间的差异(输入差分对)以及栅-源电压与阀值

2018-09-13 10:08:21

本文设计的带共模反馈的两级高增益运算放大器结构分两级,第一级为套筒式运算放大器,用以达到高增益的目的;第二级采用共源级电路结构,以增大输出摆幅。另外还引入了共模反馈以提高共模抑制比。

2021-04-14 06:55:14

求微弱电流检测用的共模电压范围最大值大于65V的运算放大器或仪表放大器

2023-11-14 07:21:08

折叠共源共栅比较器怎么修改为迟滞比较器

2021-06-24 07:36:52

怎么设计一种单级全差分增益增强的折叠共源共栅运算放大器?

2021-04-20 06:26:29

CMOS运算放大器结构具有哪些特点?如何去设计CMOS运算放大器?怎样对CMOS运算放大器进行仿真测试?

2021-04-21 07:21:39

。通用运算放大器为我们提供了一个坚实的基础以开发专用的元件。所有运算放大器旨在在这些领域实现好的性能:大开环增益、共模抑制和电源抑制。高输入阻抗和低输出阻抗也是关键要求。Precision

2018-10-22 08:57:48

对轨输入/输出运算放大器.不同于传统的实现恒定跨导的技术,在电路设计实现上通过一个简单的检测电路,使互补差分对在整个共模输入电压变化范围内交替工作,实现了跨导恒定.同时为了得到较高的转换速率,加入了转换

2010-04-22 11:34:49

分析了准浮栅晶体管PMOS 的工作原理、电学特性和等效电路,设计了一种电路结构简单的共模反馈电路(CMFB),实现了一个低压低功耗的差分运算放大器。采用Chrt0.35umCMOS 工艺

2009-11-27 11:39:23 8

8 本文设计了一种低压低功耗CMOS 折叠-共源共栅运算放大器。该运放的输入级采用折叠-共源共栅结构,可以优化输入共模范围,提高增益;由于采用AB 类推挽输出级,实现了全摆幅输

2009-12-14 10:37:19 30

30 基于SOC应用,采用TSMC 0.18μm CMOS工艺,设计实现了一个低电压、高增益的恒跨导轨到轨运算放大器IP核。该运放采用了一倍电流镜跨导恒定方式和新型的共栅频率补偿技术,比传统结构更

2010-02-24 11:56:58 25

25 设计了一种用在高精度音频Σ-Δ A/D转换器中的高增益CMOS全差分运算放大器。该运算放大器采用了套筒式共源共栅结构和开关电容共模反馈电路。通过分析和优化电路性能参数,实现了

2010-07-29 17:23:00 51

51 摘要:采用共源共栅运算放大器作为驱动,设计了一种高电源抑制比和低温度系数的带隙基准电压源电路,并在TSMC0.18Um CMOS工艺下,采用HSPICE进行了仿真.仿真结果表明:在-25耀115益

2010-10-18 01:17:25 56

56

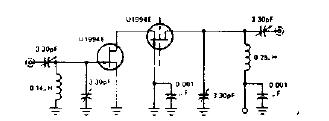

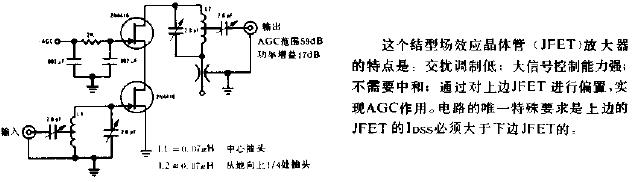

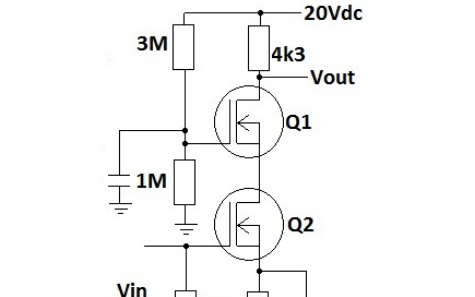

80MHz共源共栅放大器电路图

2009-04-08 09:10:10 2058

2058

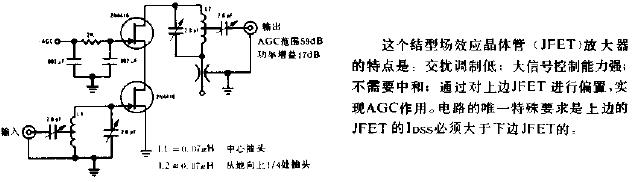

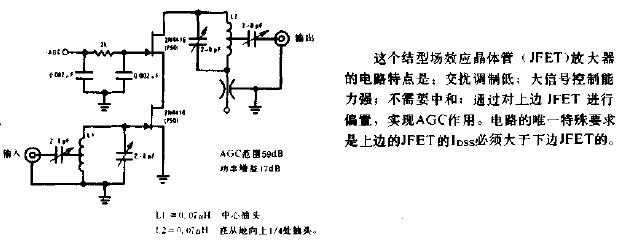

200MHz共源共栅放大器电路图1

2009-04-08 09:12:49 1839

1839

200MHz共源共栅放大器电路图2

2009-04-08 09:13:12 1252

1252

采用运算放大器的基准电压源电路

2009-05-12 22:56:49 5850

5850

折叠共源共栅运算放大器原理及设计

1 引言

本文介绍的运放是一种采用TSMC 0.18 μm Mixed Signal SALICIDE(1P6M,1.8V/3.3V)CMOS工艺的折叠共源共栅运放,并对其进行了DC

2010-03-12 15:05:24 12904

12904

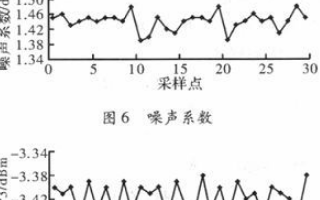

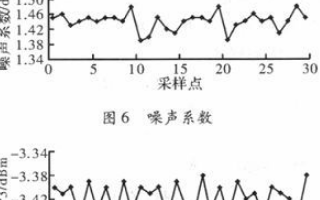

3GHz CMOS低噪声放大器优化设计

摘 要: 基于0.18 μm CMOS工艺,采用共源共栅源极负反馈结构,设计了一种3 GHz低噪声放大器电路。从阻抗匹配及噪声优化的角度分析了

2010-04-13 12:57:29 1966

1966

随着集成电路技术的不断发展,高性能运算放大器广泛应用于高速模/数转换器(ADC)、数/模转换器(DAC)、开关电容滤波器、带隙电压基准源和精密比较器等各种电路系统中,成为模

2011-06-07 16:02:34 52

52 电子发烧友提供了采用运算放大器的基准电压源,欢迎大家学习

2011-06-20 18:55:38 6150

6150

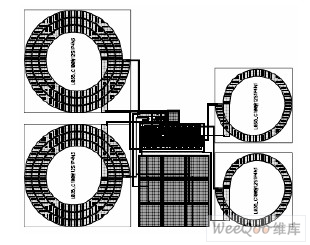

本文设计了一种采用增益增强结构的带开关电容共模反馈的折叠式共源共栅跨导运算放大器,可用于流水线结构的A/D中。出于对性能及版图因素的考虑,采用了单端放大器作为增益提高

2011-06-29 09:45:09 12396

12396

设计并讨论了一种高单位增益带宽cmos全差分运算放大器。由于折叠共源共栅结构电路具有相对高的单位增益带宽以及开关电容共模反馈电路稳定性好、对运放频率特性影响小等优点,故

2011-07-31 21:51:57 117

117 采用台积电0.18umCMOS工艺设计了中心频率在5.25GHz的功率放大器,其中使用了共源共栅电感对功率放大器电路进行改进,在一定程度上提高了功率放大器的效率

2011-08-25 14:13:04 5621

5621

1.)噪声系数。共发和共基放大器噪声系数相同,当考虑内部反馈时,共发电路比共基电路还有低一点;射频小信号放大器基本上都采用共发接法,共基接法在几十几百M还可以见到,但是

2011-12-09 14:59:24 2138

2138 共源共栅级放大器可提供较高的输出阻抗和减少米勒效应,在放大器领域有很多的应用。本文提出一种COMS工艺下简单的高摆幅共源共栅偏置电路,且能应用于任意电流密度。根据饱和电

2012-02-15 10:48:31 64

64 给出了两种应用于两级CMOS 运算放大器的密勒补偿技术的比较,用共源共栅密勒补偿技术设计出的CMOS 运放与直接密勒补偿相比,具有更大的单位增益带宽、更大的摆率和更小的信号建立时

2012-02-15 11:09:50 78

78 本文设计了一种用于高速ADC中的高速高增益的全差分CMOS运算放大器。主运放采用带开关电容共模反馈的折叠式共源共栅结构,利用增益提高和三支路电流基准技术实现一个可用于12~14

2012-06-06 13:08:28 42

42 设计了一种用于高速ADC中的高速高增益的全差分CMOS运算放大器。主运放采用带开关电容共模反馈的折叠式共源共栅结构,利用增益提高和三支路电流基准技术实现一个可用于12~14 bit精度

2012-06-07 14:21:36 38

38 恒跨导轨对轨CMOS运算放大器的设计_赵双

2017-01-07 22:14:03 5

5 共源共栅跨导运算放大器的设计

2017-03-05 15:00:06 10

10 的。 这种灵活性允许在 CMOS

工艺中发展高性能无缓冲运算放大器。 目前, 这样的放大器已被广泛用于无线电通信的集成电路中。 介绍了一种折叠共源

共栅的运算放大器, 采用 TSMC 0. 18 混合信号双阱 CMOS 工艺库, 用 HSpice W 2005. 03 进行设计仿真, 最后与设计指标

2022-07-08 16:32:35 23

23 基于 chartered 0.35 m 工艺,采用 PMOS 管作为输入管的折叠式共源共栅结构,设计了一种采用增益提高技术的两级运算放大器。利用 Cadence 公司的spectre 对电路进行仿真

2017-11-04 10:40:17 30

30 运算放大器作为模拟系统和混合信号系统中的一个重要电路单元,广泛应用于数/模与模/ 数转换器、有源滤波器、波形发生器和视频放大器等各种电路中。伴随着每一代CMOS 工艺 的发展,电源电压和晶体管沟道

2018-06-10 14:20:00 41721

41721

摆幅。尽管其具有上述优点,但它不适合两个辅助运放。因为两个辅助运放的输出负载是主运放中共源共栅管的栅电容,它们都较小。若采用开关电容共模反馈,共模反馈电路的电容势必更小,致使开关的电荷注入效应影响到

2018-06-08 08:59:00 11077

11077

。放大器的输出较容易实现轨对轨, 但在输入端实现轨对轨是比较复杂的, 原则上只能是折叠式共源共栅结构才能使输入端包含电源电压的轨, 这种技术是实现所有轨对轨输入放大器的基础。

2018-12-18 09:15:00 9242

9242

CMOS运算放大器的基本分类1、单级差分运算放大器(电流镜做负载的差分放大器)2、套筒式共源共栅CMOS运算放大器(单级)3、折叠共源共栅CMOS运算放大器(单级)4、两级CMOS运算放大器

5、Rail-to-Rail CMOS运算放大器6、Chopper CMOS运算放大器 运放的概念、组成与电路结构

2018-11-07 10:10:57 98

98 如图是一个共源共栅放大器,同时也可以看作双栅场效应管。请问:1.这样结构的电路为什么会产生密勒效应呢?

2018-12-29 09:27:05 0

0

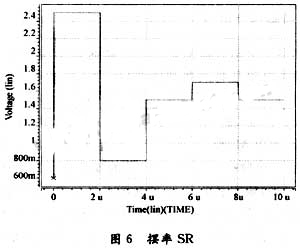

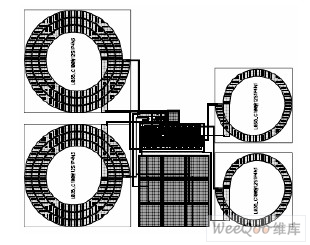

CMOS两级运算放大器输入方波信号,得到其摆率;应用virtuoso绘制该CMOS两级运算放大器版图,进行DRC检查,进行LVS检查。具体过程为:恒流源偏置电路的设计,差分放大器的设计(包括输入对管的设计及有源负载对管的设计),第二级共源放大器的设计,缓冲级的设计考虑,沟道长度的选

2019-03-21 17:23:37 0

0 CMOS 运算放大器是 CMOS 模拟集成电路的最重要的模块,它的特性决定了模拟集成电路的特性。复杂的 CMOS 运算放大器的基础是简单的单级放大器。本章将介绍常用的单级共源放大器、共栅放大器、源跟随器、共源共栅放大器。

2019-05-14 08:00:00 2

2 运算放大器是模拟电路中最重要和最通用的单元电路之一,同时也是许多模拟系统和数/模混合信号系统中的一个完整模块。运放具有足够大的正向增益,当加负反馈时,闭环传输函数与运算放大器的增益几乎无关。利用这个

2020-01-25 16:50:00 11760

11760

稳定性、噪声源、线性度、匹配网路关键点进行分析,并针对WCDMA接收机系统应用,设计了低噪声放大器,电路采用TSMC90nmCMOS工艺。芯片测试结果表明,该低噪声放大器,电压增益达到20 dB、噪声系数NF为1.4 dB、IIP3为-3.43 dBm。

2020-01-01 17:26:00 4092

4092

已有文献[2]采用PMOS差分对来实现电源电压为1V的运算放大器,但由于Vt,PMOS的典型值为-0.75V,使得前置反馈电路的工作电平范围为1-0.15V,几乎涵盖整个共模电平范围,运算放大器

2020-07-24 10:11:29 3189

3189

MT-041:运算放大器输入和输出共模与差分电压范围

2021-03-21 10:37:32 5

5 我的论文题目是《CMOS 运算放大器的设计和优化》。我们可以知道无论在数 字还是模拟电路中,运算放大器运用之广泛是显而易见的。

2021-04-13 09:32:44 19

19 本文介绍了一种折迭共源共栅的运算放大器,采用TSMC0.18混合信号双阱CMOS工艺库,用HSpiceW-2005.03进行设计仿真,最后

2021-04-16 09:39:53 6643

6643

采用运算放大器实现低噪声设计

2021-04-23 08:16:08 15

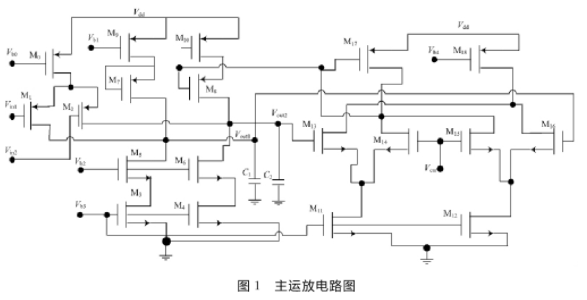

15 共源共栅级放大器可提供较高的输出阻抗和减少米勒效应,在放大器领域有很多的应用。本文提出一种 COMS 工艺下简单的高摆幅共源共栅偏置电路,且能应用于任意电流密度。根据饱和电压和共源共栅级电流密度的定义,本文提出器件宽长比与输出电压摆幅的关系,并设计一种高摆幅的共源共栅级偏置电路。

2022-04-01 14:25:31 5

5 共源级放大器,负载为电流源,电流源采用电流镜实现,偏置为电阻与电流镜实现的简单偏置。

2023-07-07 15:02:12 4804

4804

单级,共源共栅和调节型共源共栅型放大器的优缺点是什么? 放大器是电子电路中最基础也是最重要的组成部分之一。设计一种适当的放大器电路是电路设计者必不可少的技能。共源共栅和调节型共源共栅型放大器

2023-09-18 15:08:23 4997

4997 共栅放大器的两种应用是什么? 共栅放大器是一种常见的基本放大器电路,广泛应用于通信、音频和视频等领域。它具有良好的线性特性、低噪声、高输入阻抗和高输出阻抗等优点,可以实现信号放大和滤波等功能。本文

2023-09-18 15:08:26 2178

2178 。 共源共栅运放常用于放大小信号,用于放大器,滤波器,振荡器等电路中。这种运放的设计简单,线路短,不需要阻抗匹配电路,具有高增益和宽频带特性。 为什么共源共栅运放被称为telescope?这是因为共源共栅电路外部的形状和望远镜类似。共源共栅电路有两个电极,一个电极

2023-09-20 16:29:41 1996

1996 为什么共源级和共栅级放大器的输出阻抗是一致的? 共源级放大器和共栅级放大器是两种主要的放大器电路。在这两种电路中,输出阻抗是不同的。但是,在某些情况下,这两种放大器电路的输出阻抗可以相同。本文将

2023-09-20 17:05:16 3151

3151 年撰写的一篇文章中使用了tern共源共栅,讨论的是稳压器应用。他们设计了两个三极管的共源共栅,其中第一个三极管采用共阴极设置,下一个三极管采用公共栅极代替五极管。因此,它的名称可以假设为级联三极管的减少,其具有像五极管一样的相关特性。 那么,共源共栅放大器工作原理究竟是怎样的

2023-09-28 11:23:20 6757

6757

什么是理想放大器?什么是运算放大器的输入补偿电压?运算放大器的共模输入电压(CMVIN)是多少? 理想放大器是一种没有内部阻抗和无限增益的放大器。在理想放大器中,所有输入信号都被无限精确地放大到变为

2023-10-25 11:01:49 2482

2482 共源放大器(Common Source Amplifier)是一种常见的晶体管放大器配置,主要应用于模拟电路设计中。它使用一个晶体管作为放大元件,通过控制输入信号的电压来改变输出信号的电压。 1.

2024-09-27 09:29:40 2813

2813 共源共栅放大器是一种特殊的场效应晶体管(FET)放大器,它结合了共源放大器和共栅放大器的优点。在这种放大器中,一个晶体管作为共源放大器,另一个晶体管作为共栅放大器。这种放大器具有高增益、低噪声、高

2024-09-27 09:38:42 2192

2192 共源共栅放大器的增益是一个相对复杂的参数,它受到多个因素的影响,包括晶体管的跨导、负载电阻、源电阻、以及电路的具体设计等。因此,无法直接给出一个具体的增益值,而需要根据具体的电路情况来计算

2024-09-27 09:45:07 2171

2171

共源共栅放大器(Cascode)是一种在集成电路设计中常用的放大器结构,它结合了共源放大器和共栅放大器的优点,具有高输入阻抗、高输出阻抗和较大的电压摆幅。然而,在实际应用中,共源共栅放大器的增益

2024-09-27 09:46:38 1932

1932 共源共栅放大器(Cascode amplifier)是一种在模拟电路设计中常用的放大器结构,它结合了共源(Common Source,CS)和共栅(Common Gate,CG)两种放大器的优点

2024-09-27 09:48:12 4243

4243 的优点,以提高增益、稳定性和频率响应。 优点: 高增益 : 折叠共源共栅放大器通过级联共源和共栅放大器,实现了更高的增益。 共源放大器提供电压增益,而共栅放大器提供电流增益。 高输入阻抗 : 共栅放大器具有高输入阻抗,这使得折叠共源共栅放大器的输入阻抗非常高。 低输出阻抗 : 共源放大

2024-09-27 09:50:03 4777

4777 运算放大器的共模输入电压(Common Mode Input Voltage,简称CMVIN或VICM)是电子工程中的一个重要概念,它关系到运算放大器的性能以及信号处理的质量。

2024-10-18 18:02:17 6310

6310

电子发烧友App

电子发烧友App

评论