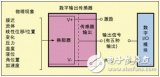

数字传感器以及由数字信号驱动的激励器的应用非常广泛,几乎所有现实中的变量(如温度、流量、压力、速度等等)测量中都可以找到数字传感器的应用,其数字输出有多种格式,本文首先根据输出信号和电路接口的类型对数字传感器分类,然后指出在选择与传感器接口的数字I/O模块时应注意哪些问题。

2015-10-01 16:34:00 1965

1965

本文介绍了数字I/O和逻辑分析仪的常用术语和定义。

2015-12-31 09:46:02 1666

1666 单片机应用系统中,常有用单片机的I/O口来实现自关机(彻底关机)的功能。一般用单片机的一个I/O口控制一个电

2017-12-20 07:32:24 9892

9892

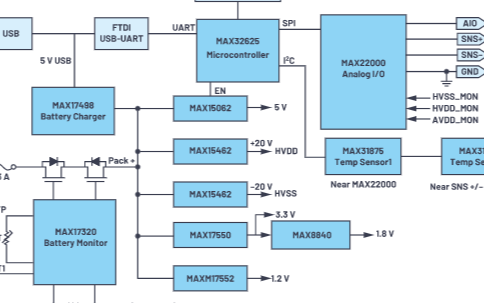

工业CAN I/O模块中基板的主要功能是对模块实施控制,并与系统控制单元进行通信。基板配备有8个模拟通道。基板从逻辑上又可以分成微控制器模块、CAN接口、模拟输入和RS232_485接口4个模块。

2020-07-06 07:58:00 3779

3779

virtio 是一种通用的半虚拟化的 I/O 通信协议,提供了一套前后端 I/O 通信的的框架协议和编程接口。根据该协议实现的设备通过前后端的配合,相比全模拟设备可以大幅减少陷入陷出以及内存拷贝的次数,使 guest 获得高效的 I/O 性能。

2022-03-10 13:37:10 8024

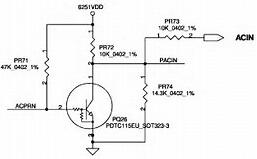

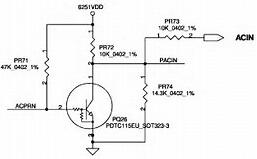

8024 电路图如下!~想用光敏三极管的信号来使用单片机的外部中断,但是单片机I/O口一直保持初始值高电平,不能被光敏三极管的信号改变。同样的管脚,用一个震动模块产生的信号可是实现功能,但是光敏三极管就不能实现。请教高手是什么原因!~~如何解决?

2019-10-15 21:57:14

数字逻辑功能单元有哪些呢?数字逻辑是怎样通过数字电路的形式来实现的?

2021-11-02 07:08:41

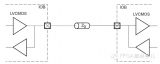

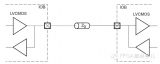

小弟毕设需要用到一个逻辑电平转换模块,主要问题如下: 1、FPGA输出的 3.3V 数字信号 需要通过 逻辑电平转换芯片,转换为1.8V或2.5V或3.3V中的一种。 2、 本设计需要16路数字IO

2015-09-04 21:21:28

都可配置成输入、输出。每个bank的首尾管脚只能作为单端I/O,其余48个I/O则可配置成24对差分I/O。在差分信号的实现过程中,管脚分配应选择相应电平标准的bank中除首尾以外的其他48个IO

2020-12-23 17:17:47

)来实现组合逻辑,每个查找表连接到一 个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用 金属连线互相连接或

2019-08-11 04:30:00

为什么配置I/O口:I/O端口寄存器复位后默认为输入(输出高阻态);为实现I/O端口功能需要先对端口进行I/O口初始化配置I/O口需要的几种寄存器:ANSELx(模拟选择寄存器):0 = 数字I/O

2021-11-24 06:19:54

前言此实验是通过STM32CubeMX来配置stm32实现按键输入,以此来了解stm32I/O的输入操作及如何使用HAL库来实现I/O输入。本实验中的按键操作使用的是软件中断,并未用到stm32

2022-03-01 06:58:08

,输出高低电平。就是通过这简单的控制电平来实现大多数的应用控制。1. 什么是 I/O 口?I 表示 IN(输入),O 表示 OUT(输出),所以 I/O = 输入/输出2. I/O 具体能做什么呢?如果你是刚刚步入电子的新手,那你最好要知道一下I/O口具体能做什么。感性的认识对你的..

2021-11-24 06:47:23

UEFI学习(四)-SuperIo的访问一、什么是Super I/O?二、我们要用SuperIo实现什么三、NCT5581D的访问机制一、什么是Super I/O?Super I/O 芯片也叫 I

2022-01-24 08:12:27

本文介绍了数字I/O和逻辑分析仪的常用术语和定义。

2021-05-06 06:39:26

P1.7使用上升沿触发中断。在仿真运行时,在外部还没有加上中断信号时,会进入一次中断。每次都是这样,是不是由于仿真过程中I/O管脚有上升电平造成的?

2015-02-10 14:13:16

使用MCU的I/O管脚连接物理按键,当按键按下时会发送上升沿或下降沿的电平出发中断,这个容易判断。

请问,对于按键双击动作,以及按键长按动作,应该如何判断?

是否存在简单的实现方法,最好能给Demo源码,多谢!

2023-08-24 07:42:04

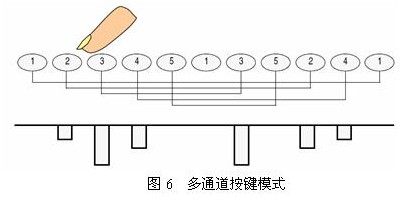

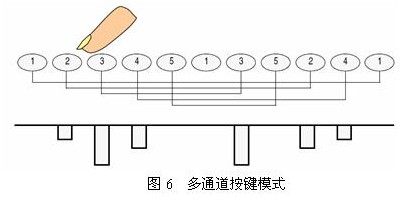

的作用。因此,探讨一些键盘的特殊结构,用尽可能少的输入输出端口实现较多数量的按键数仍具有重要的应用价值。 有些特殊情况下,在组成一个最小的单片机系统的过程中,由于通用的I/O口有限,而又需要大量的按键

2012-02-15 22:02:49

逻辑门是数字电路的基础。各种多姿多彩的逻辑门组合在一起,形成了数字电路的大千世界。实际上,逻辑门反映的是逻辑代数的几种基本运算,只要你能够实现这样的逻辑代数规则,你就能够用其他设备来实现逻辑门的功能,看!

2019-07-23 07:03:30

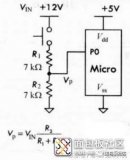

单片机应用系统中,常有用单片机的I/O口来实现自关机(彻底关机)的功能。一般用单片机的一个I/O口控制一个电子开关来实现,因单片机关电后,失去电源,所以在关机时,实现关机的IO口的电平必须用低电平

2017-12-14 20:15:53

我毕设要做一个多通道数采系统,需要用NI 多功能数采卡的数字I/O输出控制CD4051的3个控制端,在数字输出的编程上遇到了点问题。想请教一下,这个DO输出的数字量是瞬时的还是持续的?我需要通道选定后保持,然后发波、采集,完了之后再切换通道,即改变数字输出量。这个数字I/O编程怎么实现?

2014-04-25 21:44:34

如何实现数字系统的电平和极性转换?比较器在电路中起到什么作用?

2021-04-14 06:31:09

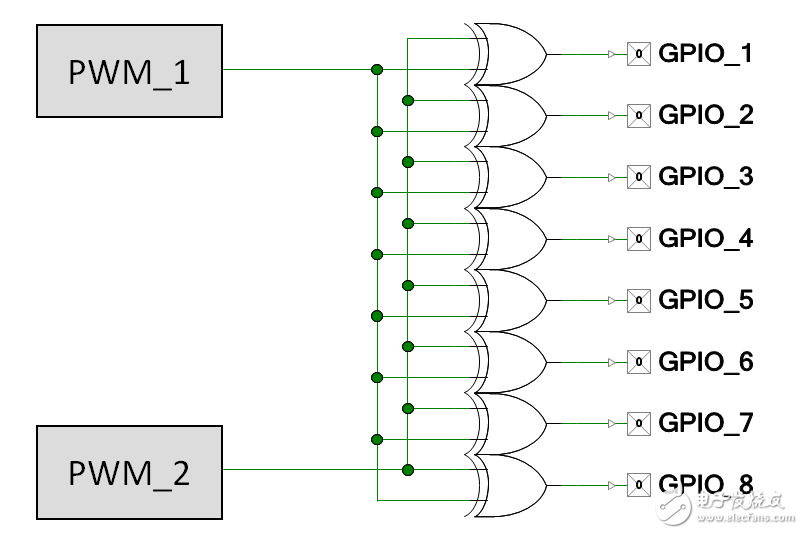

MCU通用I/O引脚扩展 低端MCU由于I/O口数量不足导致部分功能无法实现,用户需要使用数字集成芯片进行扩展,如74LS系列移位寄存器,但是这种集成芯片也会由于引脚数量限制而无法确保单片机端口

2024-01-08 09:35:10

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2019-08-19 06:15:33

电平才能跳变,否则维持原来状态。如下图,A、B分别是2个输入端电平,O是输出端电平,怎样用简单的电路实现功能?关键是第2阶段和第4阶段的跳变条件要满足。

2013-10-28 14:16:25

DSPF2812 GPIOF12配置成通用I/O,发现输出不了逻辑高电平,结果发现这个管脚没有内部上拉,是这个原因吗?

2020-06-04 14:04:45

轻松实现高速串行I/OFPGA应用设计者指南输入/输出(I/O)在计算机和工业应用中一直扮演着关键角色。但是,随着信号处理越来越复杂,I/O通信会变得不可靠。在早期的并行I/O总线中,接口的数据对齐

2020-01-02 12:12:28

本文介绍了一种基于Windows下通过程序采用数字I/O卡控制步进电机的方法。

2009-04-02 16:07:16 34

34 本文介绍了一种基于VXI总线的数字I/O模块(型号为DIOM-64)在数字电路板ATE中的应用,内容包括模块的工作原理和测试设备的组成。该数字I/O模块已在某雷达的数字电路板ATE和数字/模

2009-07-15 11:20:14 37

37 数字系统的基本算法与逻辑电路实现:本章主要介绍数字系统的基本算法设计及对应的逻辑电路的实现方法。算法设计中主要考虑的因素1.逻辑指标这是数字系统最重要、

2009-09-01 09:04:09 0

0 数字I/O脚有专用和复用。数字I/O脚的功能通过9个16位控制寄存器来控制。控制寄存器分为两类:(1)I/O复用控制寄存器(MCRX),来选择I/O脚是外设功能还是I/O功能。(

2009-09-16 12:20:48 19

19 使用一个I/O口实现A/D转换输入:在某些特定的场合,主要是在数字电子应用方面,需要一个模拟信号输入来做一些基本的模拟量的测量或者是提供可控的方式使用外部电位器。当然

2009-09-26 10:34:36 38

38 EDA9060开关量I/O 模块在电气控制柜中的典型应用—— EDA9060结合交流接触器实现远程控制EDA9060开关量I/O模块是山东力创科技自主研发的一款分布式DI/DO工控模块,主

2009-12-07 13:42:34 44

44 使用一个I/O口实现A/D 转换输入在某些特定的场合,主要是在数字电子应用方面,需要一个模拟信号输入来做一些基本的模拟量的测量或者是提供可控的方式使用外部电位器。当然

2010-03-28 22:36:53 36

36 二值数字逻辑和逻辑电平

二进制数正好是利用二值数字逻辑中的0和1来表示的。二值数字逻辑是Binary Digital Logic的译称。 与模拟信

2009-04-06 23:37:10 4687

4687

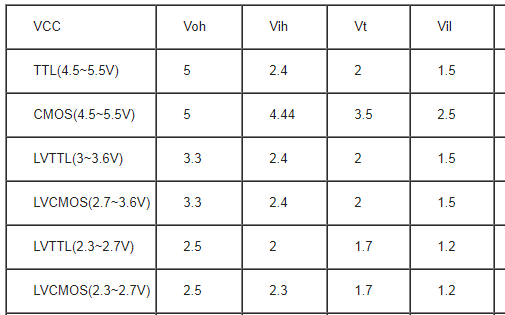

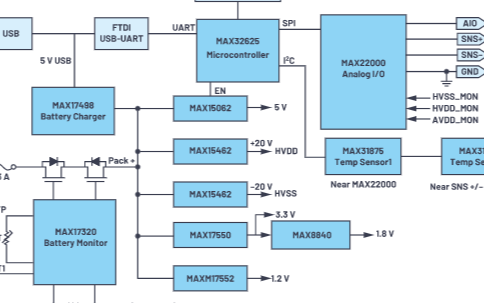

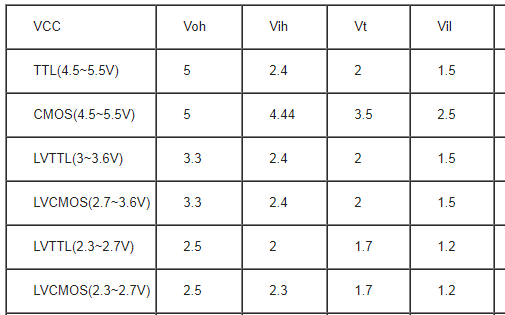

摘要:逻辑电平转换技术及其缺陷—Maxim的解决方案。

对逻辑电平转换的需求越来越多的数字IC采用与以往不兼容的电源电压、更低的VDD、或者VCORE和VI/O不同的

2009-04-23 14:01:11 3725

3725

摘要: 介绍了采用Videx-ⅡPR0系列FPCA设计的应用于下一代无线通信系统中的高速I/O。由于充分利用芯片中集成的Rocket I/O模块,并采用差分输入参考时钟、

2009-06-20 10:45:35 1632

1632

利用普通I/O口实现电容触摸感应方案

技术背景

现在电子产品中,触摸感应技术日益受到更多关注和应用,不仅美观

2010-04-22 10:16:16 1952

1952

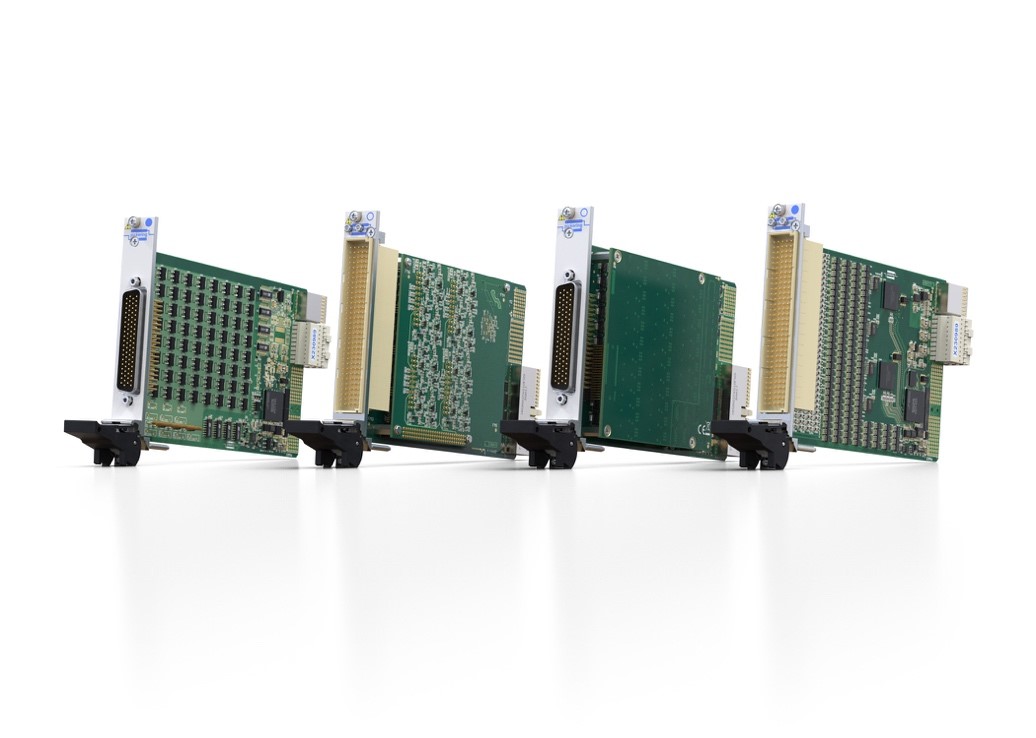

本文介绍的基于CompactPCI总线的数字隔离I/O模块是应用于对抗震性能要求较高的内场测试系统上

2011-04-15 15:07:31 36

36 一名设计工程师怎样才能真正充分利用串行I/O的各种技术呢?在开始设计之前,我们需要知道什么对于实现串行I/O是有益的。我们需要研究一些基于串行设计的单元器件,从而了解一下

2012-04-01 15:01:36 29

29 本内容提供了德州仪器PLC/DCS I/O模块的模拟数字输入输出解决方案

2012-12-03 16:13:28 4746

4746 凌华科技发表100 MHz的新款PCI Express®接口高速数字I/O模块,PCIe-7360支持高达400 MB/s数据带宽,适用于高速IC检测与数字波形采集及输出应用。

2013-09-13 15:10:16 2355

2355 Delphi教程实现Windows95/98的I/O端口读写,很好的Delphi学习资料。

2016-03-16 14:59:35 6

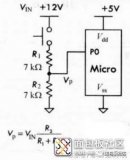

6 本文是对三极管实现逻辑电平转换进行具体分析,希望能帮助到大家!

2016-03-24 17:35:11 15

15 Xilinx FPGA的I/O兼容多种电平标准,包括LVTTL、LVCMOS、LVDS、LVPECL等,下面对各类电平标准做简要介绍。 一、LVTTL(LowVoltage

2017-02-08 03:42:12 11033

11033

TURCK全新工业以太网多协议I/O模块FEN20系列可以将自动化系统中的数字量I/O信号快速地接入控制网络。由于采用即插即用的多协议网络技术,可以方便地通过FEN20系列将数字量I/O信号接入PROFINET,ETHERNET/IP或MODBUS TCP系统。

2017-09-21 16:30:35 5

5 T1K系列I/O模块采用基架式安装方式。根据I/O模块所占用的I/O点数,选择合适的基架,模块安装于基架中,通过各基架上的总线系统连接起来,加上电源模块,通讯连接模块组成T1K子局系统。每个T1K子局系统最多可以带16个I/O模块。

2017-09-22 16:04:31 10

10 使用一个电源模块时,应放置在最左边的位置,增加的电源模块必须安装在I/O组件之间以适合电流消耗的要求。每个电源模块都对其右边的组件进行供电,截止到下一电源模块。本地扩展I/O系统的最左边位置不一定使用电源模块。

2017-09-24 11:03:44 9

9 介绍常用的几种逻辑电平,然后给出其与光模块的接口电路。 TTL 电路的电平就叫 TTL 电平,CMOS 电路的电平就叫 CMOS 电平。 TTL 集成电路的全名是晶体管-晶体管逻辑集成电路(Transistor-Transistor Logic),标准 TTL 输入高电平最小 2V,输出高电平

2017-11-06 16:50:08 100

100 1. 电压等级概述 数字设备需要在规定的电压等级下才能进行的正常信号采集和生成操作。 数字I/O设备的电压等级定义了设备如何确定有效的逻辑状态(逻辑高电平或逻辑低电平)。 电压等级的定义根据设备是单

2017-11-16 16:33:30 15446

15446

随着嵌入式系统的小型化趋势,市场对减少器件间通信所用的I/O 引脚数的需求与日俱增。Microchip 开发的UNI/O® 总线满足了这一需求,这一低成本且易于实现的解决方案,仅需要使用一个I/O 引脚就可实现双向通信。

2018-04-27 16:14:24 8

8 内容包括:理想的确定性以太网I/O,具有确定性分布式I/O的NI系统,C系列的I/O模块,与LabVIEW的无缝集成,

2018-06-14 06:19:00 5059

5059

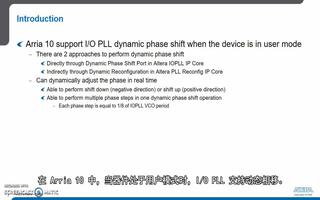

如何在 Arria 10 中实现 I/O 锁相环 (PLL) 动态相移

2018-06-20 04:56:00 4141

4141

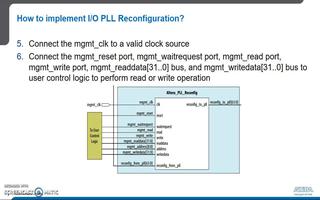

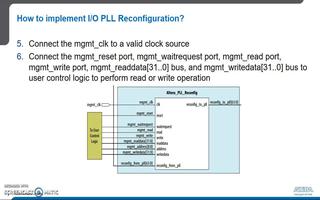

如何在 Arria 10 中实现 I/O 锁相环 (PLL) 重配置

2018-06-20 00:57:00 4559

4559

速度替高70倍的数字I/O模块 (点击CC按钮,选择中文字幕)

2018-10-08 03:16:00 6124

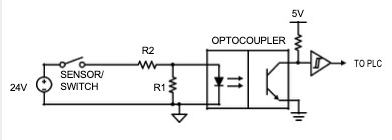

6124 如何为I/O模拟模块设计保护电路

2019-04-28 06:07:00 5040

5040

观看此视频,了解ADuM1250/ADuM2250 iCoupler®数字隔离器如何利用Philips针对I2C开发的三电平逻辑系统来实现双向数据传输。

2019-08-01 06:06:00 6772

6772 此在线研讨会将探讨如何应对与工业控制应用中所用的模拟I/O模块设计与实现相关的需求与挑战,特别着重讨论PLC(可编程逻辑控制器)模块。还将介绍一些设计和应用的诀窍及技巧,并讨论ADI公司的解决方案实例。

2019-07-11 06:19:00 2838

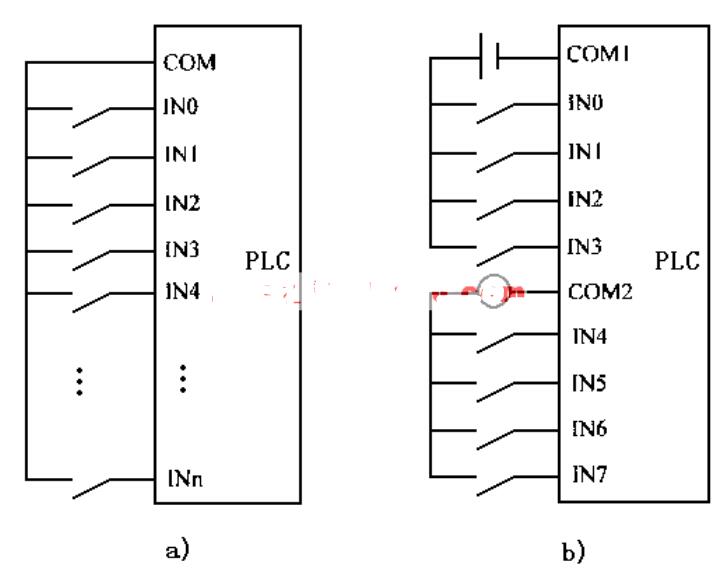

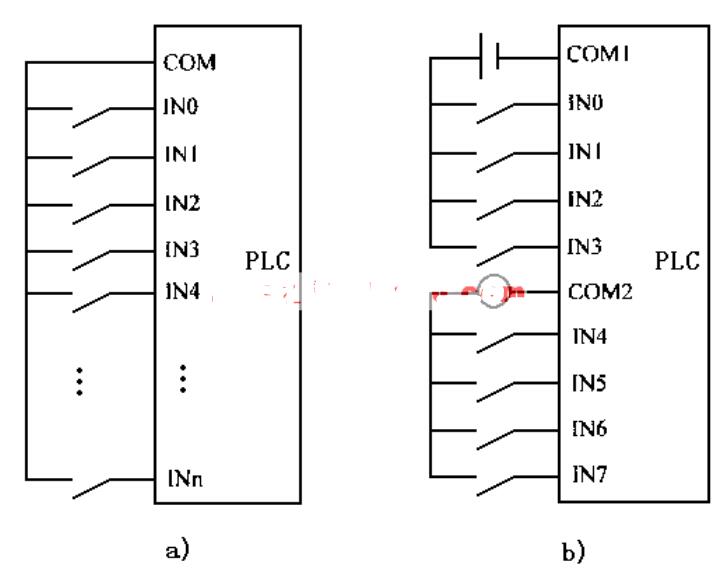

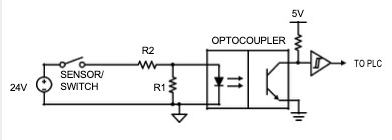

2838 一般I/O模块的价格占PLC价格的一半以上。PLC的I/O模块有开关量I/O模块、模拟量I/O模块及各种特殊功能模块等。不同的I/O模块,其电路及功能也不同,直接影响PLC的应用范围和价格,应当根据实际需要加以选择。

2020-05-19 08:54:16 10599

10599

单片机应用系统中,常有用单片机的I/O口来实现自关机(彻底关机)的功能。一般用单片机的一个I/O口控制一个电子开关来实现,因单片机关电后,失去电源,所以在关机时,实现关机的IO口的电平必须用低电平。

2020-09-08 13:53:00 6105

6105

本篇为逻辑电平系列文章中的第一篇,主要介绍逻辑电平相关的一些基本概念。后续将会介绍常见的单端逻辑电平(针对CMOS的闩锁效应进行详细介绍)、差分逻辑电平、单端逻辑电平的互连、差分逻辑电平的互连、一些

2021-01-02 09:45:00 26223

26223

电子发烧友网为你提供实现管脚电平数字逻辑功能和降低CPU负载资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-14 08:46:14 9

9 可靠的逻辑高电平I/O电路(输入) 微控制器I/O端口线能承受的最大电压不超过5V(不同微控制器有所区别),否则有可能烧坏I/O端口。本电路中,即使使用较大的电源电压,分压网络也会送一个安全的(5V

2021-08-16 14:52:33 9694

9694

第6章:数字输入/输出模块(I/O)PPT下载

2021-10-08 14:51:53 21

21 为什么配置I/O口:I/O端口寄存器复位后默认为输入(输出高阻态);为实现I/O端口功能需要先对端口进行I/O口初始化配置I/O口需要的几种寄存器:ANSELx(模拟选择寄存器):0 = 数字I/O

2021-11-16 11:21:01 6

6 单片机应用系统中,常有用单片机的I/O口来实现自关机(彻底关机)的功能。一般用单片机的一个I/O口控制一个电子开关来实现,因单片机关电后,失去电源,所以在关机时,实现关机的IO口的电平必须用低电平。

2022-02-09 10:42:12 4

4 单片机应用系统中,常有用单片机的I/O口来实现自关机(彻底关机)的功能。一般用单片机的一个I/O口控制一个电子开关来实现,因单片机关电后,失去电源,所以在关机时,实现关机的IO口的电平必须用低电平。

2022-02-09 11:17:27 4

4 如何实现单片机用一个I/O采集多个按键信号

使用模数转换(ADC)的特点就可以实现单片机用一个I/O采集多个按键信号。

一、单片机的I/O口检测按键简说

我们知道,一般情况下单片机的一个I/O口作为

2022-02-11 14:23:22 11

11 工业模拟I⁄O模块用于和工厂内的传感器、执行器之间实现精准、低电平的电压信号与电流信号的收发。同所有电子器件一样,长时间的重复使用和不断变化的环境条件会导致其性能下降,因此需要对其进行定期校准以确保其能够按照既定标准持续运行。

2022-05-16 10:49:07 2427

2427

电子发烧友网站提供《Arduino Nano数字I/O板.zip》资料免费下载

2022-07-18 14:59:24 4

4 不管是用于过程控制安装还是工业自动化系统,I/O模块或现场接线盒在整个产品生命周期中都面临着各种独特的挑战。产品管理层需要决定每个产品使用多少个通道以及进行哪些组合,电子设计人员必须决定如何对项目

2022-08-23 09:13:19 5600

5600 I/O 模块用户手册 产品规格书

2022-08-25 15:21:53 0

0 HIMA 黑马 K1412B模块远程 I/O 配备安全相关输入。HIMA 黑马 K1412B模块输入端的输入值通过安全以太网安全地传输到连接的控制器。如果设备在数字输入上检测到故障,则用户程序会根据断电跳闸原理处理低电平。

2022-09-05 16:03:02 1064

1064

HK-MXB I/O模块可以将I/O信号与机器人系统的一些特殊功能相关联,用于对机器人进行某种控制和监控机器人系统的状态。同时,MXB模块可以安装在远程机架柜中,在合适的地方布置远程I/O站点。

2022-10-19 09:54:21 2244

2244 位于高压、恶劣、嘈杂的工厂车间环境和复杂的低压可编程逻辑控制器 (PLC) 之间的边界是经常被忽视且不起眼的数字 I/O 模块。由于应用用途的多样性以及对电气隔离、小尺寸和低功耗的共同要求,这些模块

2022-12-01 14:46:44 1990

1990

模拟转数字4-20mA转rs-485/232总线I/O采集模块带隔离

2022-12-20 11:29:10 2209

2209

Mxxc系列CANopen工业I/O数据采集模块按照苛刻的工业应用环境需求而设计,广泛应用于各种工业自动化生产、安防监控系统、自动化测量与控制系统中。用户可以采用不同的I/O的模块,来扩展IO,实现现场扩展控制和数据采集。

2022-12-30 14:00:14 1446

1446 另外,该模块可以用于用户软件的实现和测试。基于这一目的,电路板需要配备重新编程和调试用的后台调试模式(BDM)接口。工业CAN I/O模块从逻辑上分成基板、电源和I/O板三个基本电路板。板与板之间的数据传送由串行外设接口(SPI)协议保证。

2023-07-23 14:55:25 1186

1186

通过前面的输入输出的内容(LED控制与按键的使用),我们对控制I/O口有了一个基本的了解。如果需要输出高低电平,可以对该引脚进行写"1"或者"0";如果需要读取I/O的电平,直接判断该引脚是高电平或者低电平既可。

2023-10-31 17:50:54 12080

12080

什么是线与逻辑,要实现它,在硬件特性上有什么具体要求? 线与逻辑是一种基本的数字逻辑电路,用于实现布尔代数中的逻辑运算。在线与逻辑中,当所有输入信号都是高电平时,输出信号才为高电平;否则,输出信号

2023-11-17 14:11:38 9268

9268 逻辑电平是数字电子系统中的关键概念之一。它决定了信号被认定为高电平还是低电平,并进一步影响着数字电路的正确操作。逻辑电平是用来表示数字信号状态的电压水平。在数字电子系统中,常用的逻辑电平有高电平

2023-11-24 08:20:20 13297

13297

FANUC外部I/O点数不够用了怎么办?可以扩展I/O点数吗? 扩展FANUC的外部I/O点数是一种常见的需求,这可以通过一些方法来实现。 在FANUC控制系统中,I/O模块被用于将外部设备与控制器

2024-02-18 15:21:47 3600

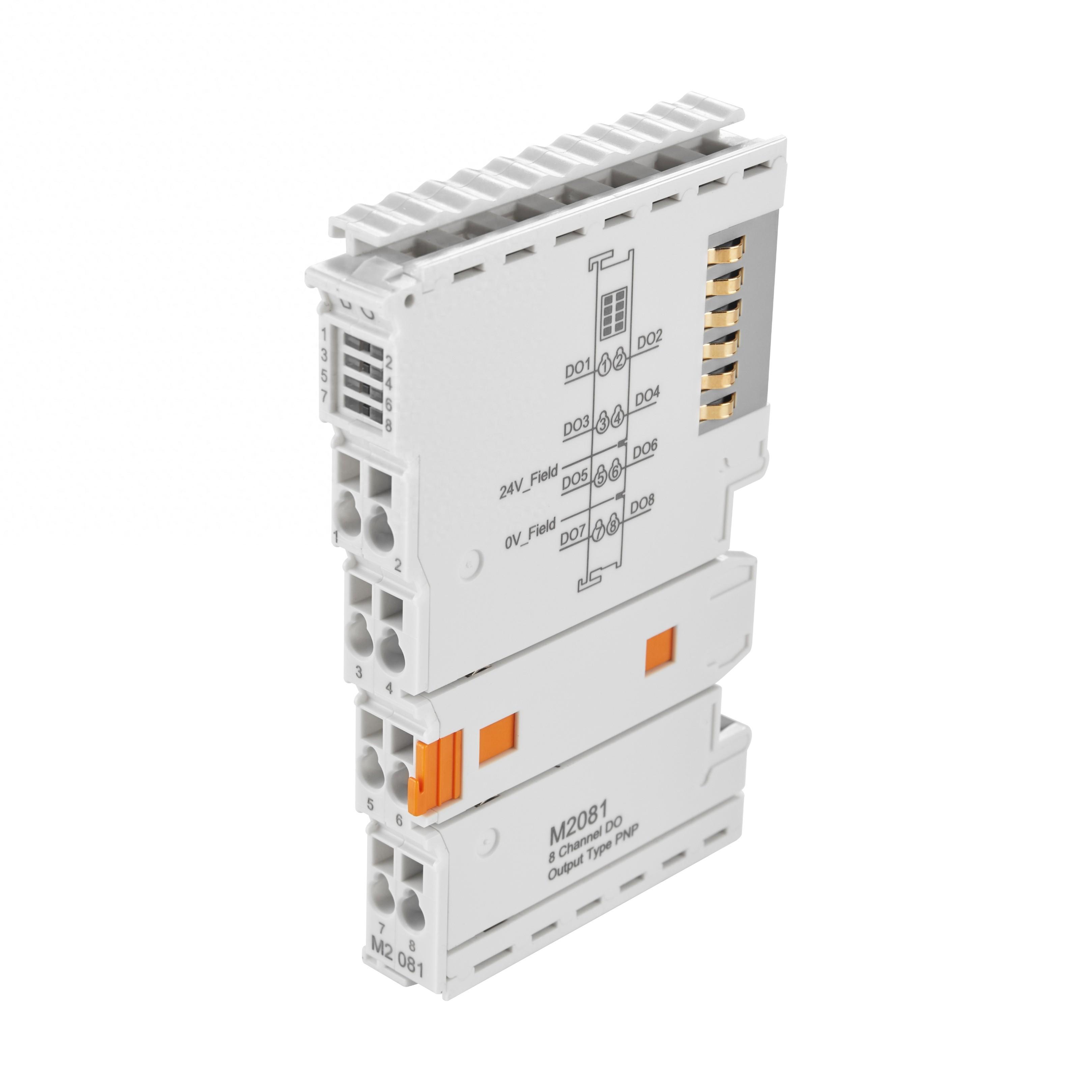

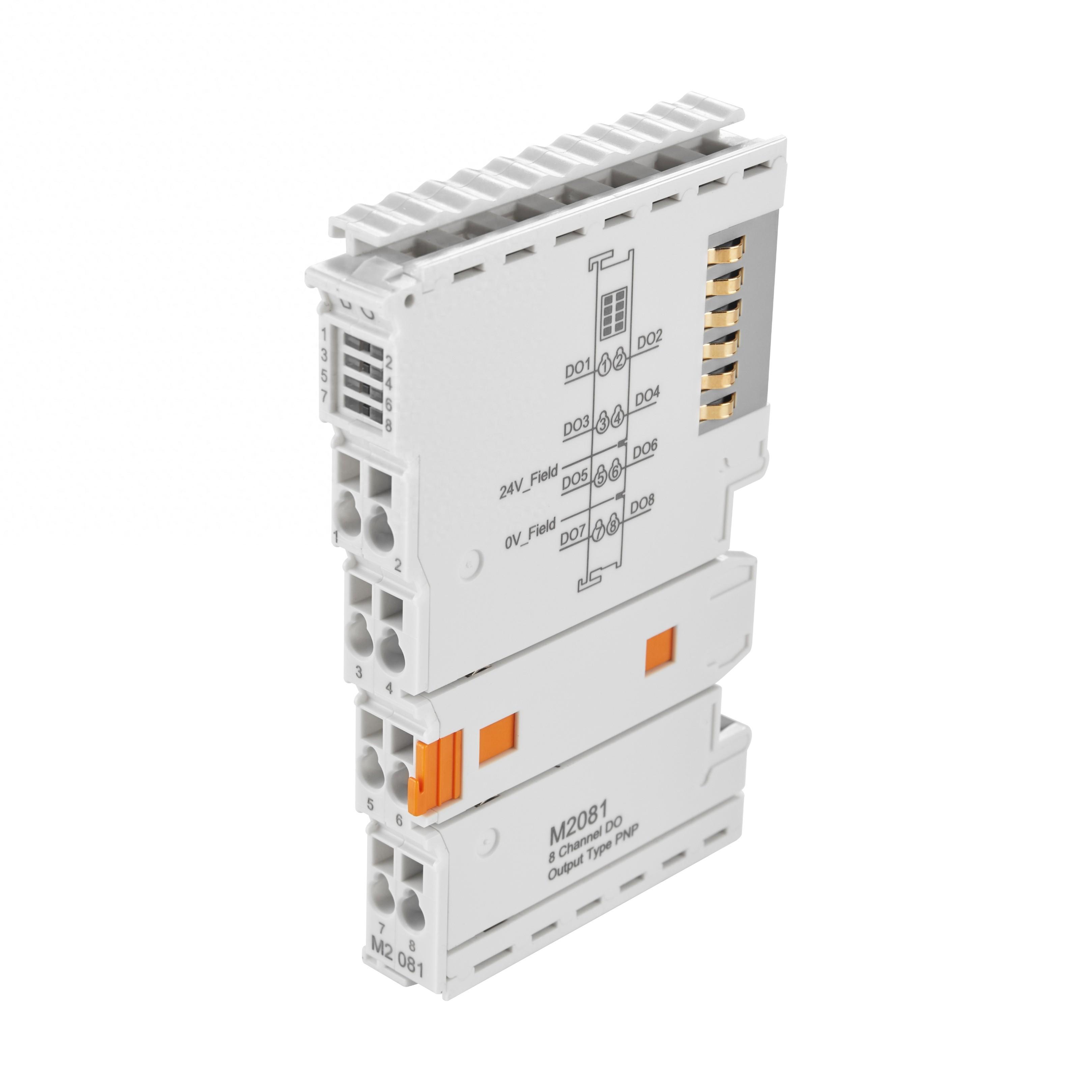

3600 16路数字量输入I/O模块M1161、M1162 16路数字量输入模块是EdgeIO I/O 系统的重要组成部分。16路数字量输入I/O模块通过高速背板总线与 EdgeI/O 控制器进行通信。有多种

2024-04-07 16:57:15 1918

1918

在工业自动化领域中,可编程逻辑控制器(PLC)扮演着至关重要的角色。作为PLC的核心组成部分,I/O(输入/输出)模块不仅连接着PLC与外部设备,更是实现信息交换的关键桥梁。本文将详细探讨PLC的I/O模块的作用,并通过多个方面来揭示其在工业自动化中的重要性。

2024-06-19 10:43:12 6269

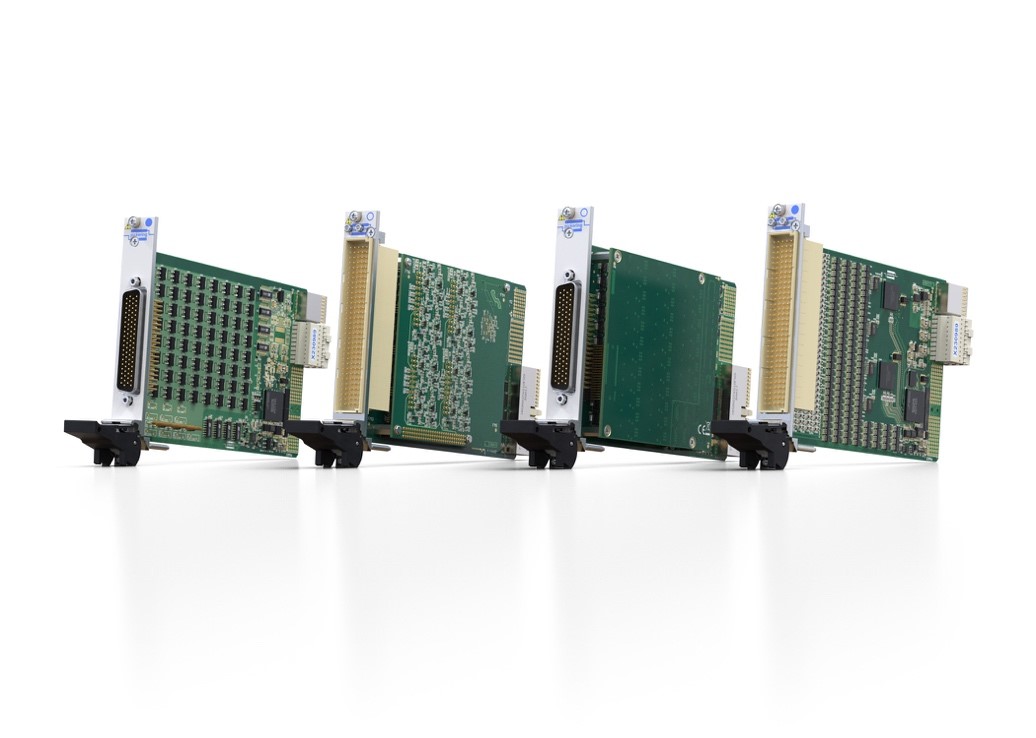

6269 开关与仿真产品的领先供应商,发布了四个新的工业数字I/O 产品系列,适用于基于 PXI 和 LXI的系统。这四个系列大幅扩展了公司现有的工业数字I/O模块的适用范围,提供了更高的通道密度,拓展了电压和电流的范围,并提供可编程的逻辑电平——所有PXI 和 PXIe 平台的产品均具有以上特性。有了这些新产

2024-06-26 09:15:49 536

536

系列大幅扩展了公司现有的工业数字I/O模块的适用范围,提供了更高的通道密度,拓展了电压和电流的范围,并提供可编程的逻辑电平——所有PXI 和 PXIe 平台的产品均具有以上特性。有了这些新产品,Pickering 现在拥有业界最大、最全面的 PXI 和 PXIe 数字 I/O 模块组合。 数字

2024-06-29 14:15:57 1216

1216 扩展了公司现有的工业数字I/O模块的适用范围,提供了更高的通道密度,拓展了电压和电流的范围,并提供可编程的逻辑电平——所有PXI和 PXIe平台的产品均具有以上特性。有了这些新产品,Pickering现在拥有业界最大、最全面的 PXI 和 PXIe 数字 I/O 模块组合。

2024-07-01 14:49:21 1188

1188 电子发烧友网站提供《保护I/O模块免受浪涌事件的影响.pdf》资料免费下载

2024-09-21 10:14:09 1

1 逻辑电平输出是数字电路中的一个重要概念,它涉及到数字信号的表示和传输。在数字电路中,逻辑电平通常指的是电路中用于表示二进制数字(0和1)的电压水平。逻辑电平输出则是指电路输出端能够提供的逻辑电平

2024-09-20 17:32:57 2210

2210 电子发烧友网站提供《使用智能高边开关优化数字I/O模块的电源.pdf》资料免费下载

2024-09-25 10:07:21 1

1 在计算机系统中,I/O接口与I/O端口是实现CPU与外部设备数据交换的关键组件,它们在功能、结构、作用及运作机制上均存在显著差异,却又相互协同工作,共同构建起CPU与外部设备之间的桥梁。本文旨在深入探讨I/O接口与I/O端口的定义、特性、功能及其区别,为读者提供全面、深入的技术解析。

2025-02-02 16:00:00 3196

3196 ),转换为串口数据传输到组态软件或PLC,通过串口下发指令控制1/2/3/4路继电器开关输出(DO),实现远程采集控制功能的串口I/O联网模块(又称“远程IO”)。产品

2025-06-05 19:32:37 1043

1043

的散热,以避免 I/O 或 ASIC 工作温度热裕度过高。根据处理器冷却需求和光学 I/O 模块总功率优化冷却策略,有助于实现适当的平衡,最大限度地提高系统的能效。

2025-11-03 09:32:02 609

609

电子发烧友App

电子发烧友App

评论