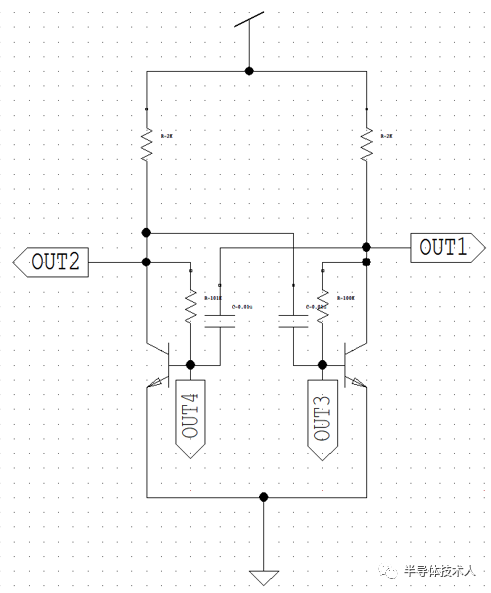

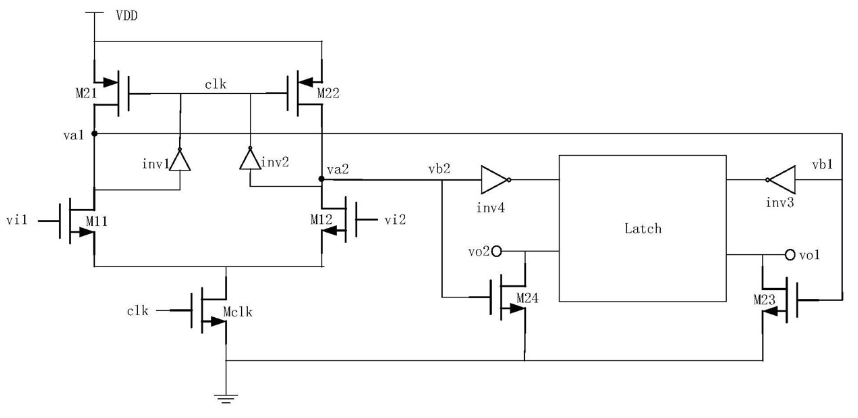

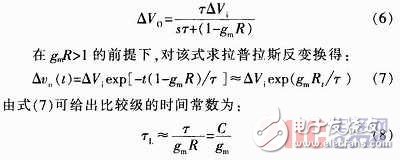

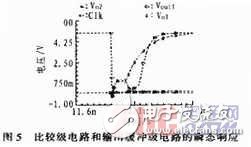

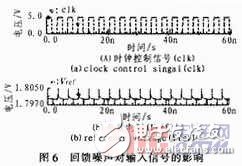

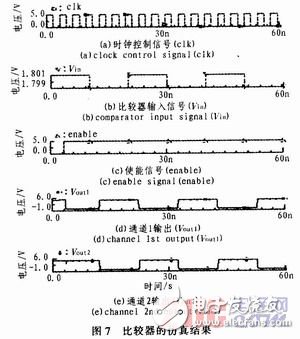

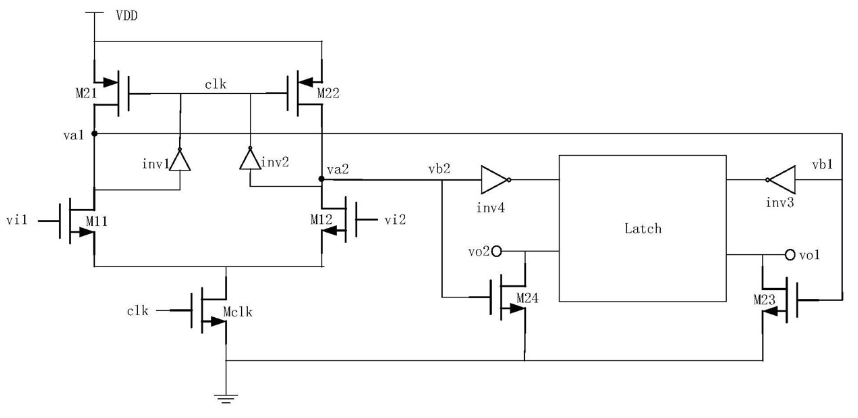

本文通过理论和仿真对比较器结构进行了分析,优化预放大电路和比较电路,设计了一种由预放大级、判断级、输出级构成的钟控比较器。把时钟脉冲应用于比较器的设计,极大地提高了比较器的性能和速度,

2011-03-01 10:44:41 12589

12589

所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。典型的锁存器逻辑电路是 D 触发器电路。 PS:锁存信号(即对LE赋高电平时Data端的输入信号)。锁存,就是把信号暂存以维持某种电平状态。

2017-10-30 14:35:53 63606

63606

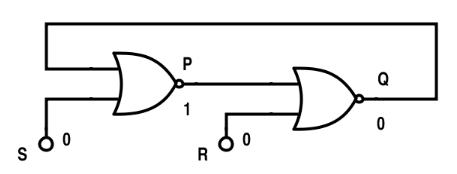

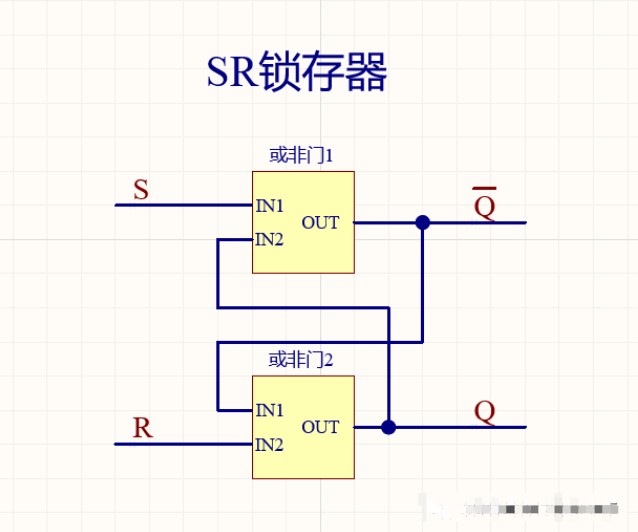

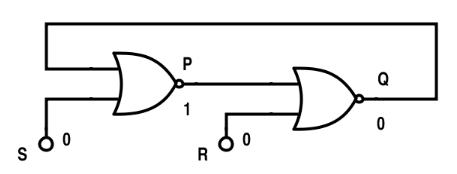

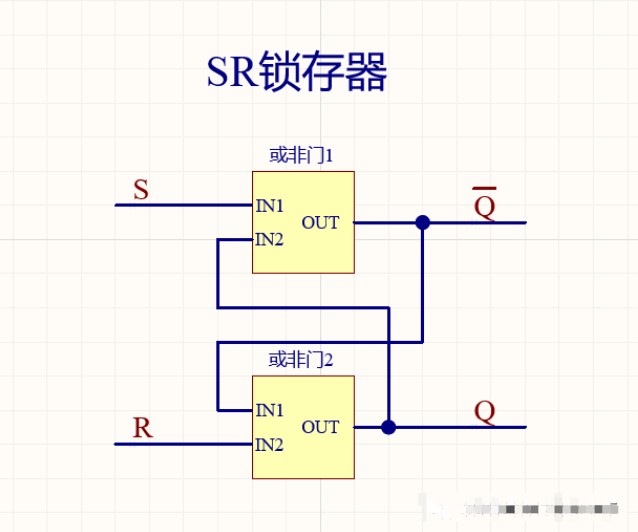

一、SR锁存器 1、RS锁存器的电路结构及工作原理 RS锁存器是一两输入、两输出的电路,其电路如图1(a),其有两个互相交叉反馈相连的两个与非门构成,其两个输出为两个相反的输出(或称为互补输出),图

2020-10-07 15:24:00 53207

53207

前言 在FPGA的设计中,避免使用锁存器是几乎所有FPGA工程师的共识,Xilinx和Altera也在手册中提示大家要慎用锁存器,除非你明确知道你确实需要一个latch来解决问题。而且目前网上大多数

2020-11-16 11:42:00 9318

9318

锁存器是具有两个稳定状态的时序逻辑电路,即它是双稳态多谐振荡器。锁存器有一个反馈路径来保留信息。因此,锁存器可以是存储设备。只要设备处于开机状态,锁存器就可以存储一位信息。当使能启用时,锁存器会在输入更改时立即更改存储的信息,即它们是电平触发设备。当使能信号打开时,它会持续对输入进行采样。

2022-09-12 16:13:00 12307

12307

上学时,老师说判断语句要把条件写全, **不然会生成锁存器,做项目时又说多比特寄存器信号的赋值一定要加if条件,不让出现else的赋值** 。就很矛盾,本文主要讲下什么是锁存器,**什么情况下会出现锁存器,以及锁存器的危害。**

2023-11-09 12:28:31 2856

2856

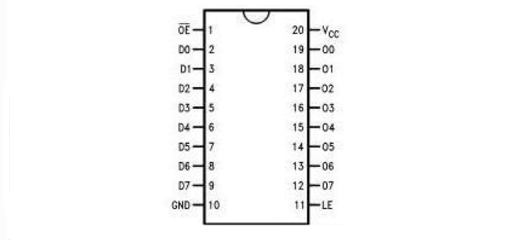

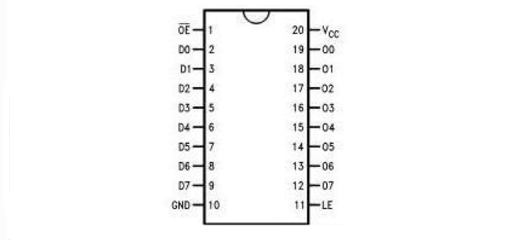

锁存器作用:可以把数据输入端与输出端进行隔离或连接。74HC573锁存器原理图见文末。图中:锁存器2-9脚为数据输入端,连接单片机数据输出引脚;12-19脚为数据输出端。GND接地,Vcc接正极

2021-11-23 06:58:06

说明rs锁存器的思想来源,或者说怎么想起来,求具体过程,即一步一步的过程

2013-10-13 09:38:12

请问,锁存器的工作原理是什么?

2013-10-15 19:35:26

锁存器的工作原理是什么?锁存器的动态特性及其应用有哪些?触发器的工作原理是什么?触发器的电路结构是如何构成的?

2021-11-03 06:48:50

锁存器和触发器1.什么情况要用到锁存器?状态不能保持?现在的单片机状态都是可以保持的吧2.看到很多产品用施密特触发器作为门极驱动器(栅极驱动器),是隔离的作用还是其他?这种触发器和专用的门极驱动器有哪些异同

2022-03-10 17:52:14

数码管的动态显示截取了部分程序,使用了74hc573锁存器,但是我觉得去掉锁存器程序照样可以执行,那么这里使用锁存器的意义是什么呢?还是说只是用一下没有什么特殊的含义? for( i=0; i

2013-03-11 16:59:52

数码管的动态显示截取了部分程序,使用了74hc573锁存器,但是我觉得去掉锁存器程序照样可以执行,那么这里使用锁存器的意义是什么呢?还是说只是用一下没有什么特殊的含义?

for( i=0

2023-10-26 07:18:07

的处理时间,消耗了处理器的处理能力,还浪费了处理器的功耗。 锁存器的使用可以大大的缓解处理器在这方面的压力。当处理器把数据传输到锁存器并将其锁存后,锁存器的输出引脚便会一直保持数据状态直到下一次锁存

2011-03-26 20:41:22

P0口作为分时复用接口,既要作为数据总线口,又要作为地址总线口 输出的低8位地址需要用8位锁存器锁存 ALE的下降沿将P0口输出的低8位地址锁存• 对于锁存器:○ /OE为输出使能端 § /OE有效

2021-12-13 08:23:27

前言在学习了基本锁存器原理后,剩下就是对各个外设以及对单片机寄存器的相关学习,如果没有看过之前对锁存器原理的讲解的同学,可以回看一下。蓝桥杯基础教程之锁存器操作(非常重要!)学习蓝桥杯必看

2021-12-03 08:05:27

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着

2019-04-23 03:35:28

预放大锁存比较器是什么工作原理?运放锁存器的电路结构分析如何使用Spectre预放大锁存比较器进行仿真?

2021-04-08 06:56:02

FS177 FS177Y 单霍尔效应锁存器芯片

特征

宽工作电压范围: 3.0V至20V

最大输出汇电流50 mA

开放集电器预驱动器

电源反向极性保护

内部拉高预驱动器

可在

2023-08-22 14:18:01

特征

宽工作电压范围: 3.0V至28V

最大输出汇电流50 mA

开放集电器预驱动器

电源反向极性保护

可用在SIP-3L包

一般说明

FS41是一个集成的霍尔效应锁存传感器,设计用于无刷直流电机

2023-12-20 16:20:31

未知未能而求知求能谓之学;已知已能而行之不已谓之习;温故而知新;故写而记之;锁存器74HC373:在学习和使用过程中,一般将OC直接接地,当LE为高时,此时将锁存器引脚打开;当LE为低时,此时将锁存器引脚关闭;其他引脚正常连接;//写该文章仅仅只为将学过的知识学之,习之。...

2021-12-06 07:24:22

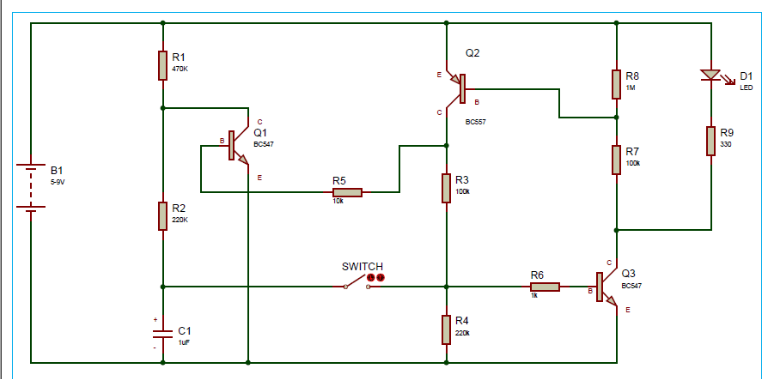

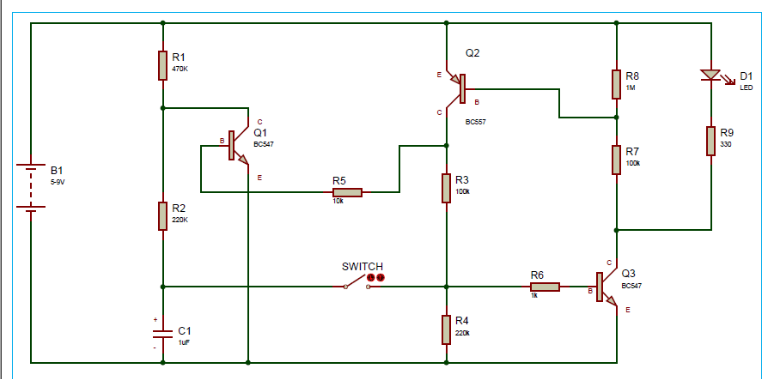

这种电路的一个有趣特性是,您可以通过选择电阻器值建立 SCR 的保持电流。为了让锁存电路在触发以后仍然保持开启,两个基极发射极结点必须要有足够的电压(~0.7 V)让其保持开启状态。这就意味着,如果

2011-12-13 09:36:29

关于锁存器问题的讨论很多同学提问到锁存器的相关问题,说明大家对这方面知识还不是很了解,今天我们就来探讨一下。上面是两个没有else的代码,其等效于下面的代码。也就是说,当if条件里面没有写else

2020-03-02 00:25:31

光立方必须是74ALS573这种锁存器吗?我现在有这种74hc373d的锁存器能用吗?

2013-11-22 00:18:53

本帖最后由 xvjiamin 于 2021-9-26 20:46 编辑

如图,在编写TDC延时链的时候,结果通过D触发器做锁存。但是出现了红色的不定态,这是为什么?该怎么解决呢?可以看到,信号

2021-09-26 20:46:03

哪位高手可以详细讲解下段锁存和位锁存的原理和用法?!!!!!!{:23:}

2013-04-26 21:43:16

LT1394的典型应用是UltraFast(7ns)比较器,具有互补输出和锁存器

2019-03-19 10:09:16

经常看到各种写HDL代码时说要避免生成锁存器,但是在某些情况,我不关心那种情况即使它生成了锁存器,对我的工程实现也没有什么影响啊,想请教下各位大神,既然这样,为什么还要避免生成锁存器(if和case

2018-01-08 23:54:39

你好什么是FPGA IO引脚的扇出....我正在使用LVTTL 3.3信号电平...我想将FPGA连接到比较器的锁存信号....我有32个比较器需要从FPGA给出锁存信号....问候,维诺德

2020-06-02 14:22:53

在CSMC O.5μm CMOS工艺条件下,采用预放大器、锁存比较电路和输出缓冲级级联的锁存比较电路结构,设计了一个高速、高精度的高性能集成电压比较器,它具有低输入失调电压、低功耗的特点。

2021-04-12 06:15:00

寄存器:register锁存器:latch触发器:flipflop 一、锁存器锁存器对脉冲电平敏感,在时钟脉冲的电平作用下改变状态。锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能

2018-07-03 11:50:27

`请问锁存器下面3个针脚怎么接线?`

2014-12-28 15:45:25

位锁存和段锁存的区别是什么怎么用

2014-03-01 10:49:27

的情况下,它们便开始导电,压制光耦合器U3的电流。U3触发由Q4和Q5组成的锁存电路。锁存电路对偏置电容器C3放电,而当VDD电压达到U2的欠压停止点时U2 停止工作。在电压接近1伏以前,锁存电路持续

2019-05-13 14:11:53

怎么设计一种中速高精度模拟电压比较器?比较器电路的总体结构是怎样的? 锁存比较器与数字触发电路有什么不同?

2021-04-20 06:05:03

本文设计了一款用于△-∑调制器的高增益高速CMOS锁存比较器。在两相互不交叠时钟的控制下,采用四级前置放大器完成对输入信号的采样、放大,高增益提高了比较器的精度并抑制

2010-07-30 17:37:50 33

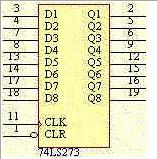

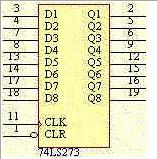

33 地址锁存器--74LS273

74LS273是带清除端的八D触发器,只有清除端为高电平时才具有锁存功能,锁存控制端为11脚CLK,在上升沿锁存。单片机的ALE端输出的锁存控制信号必须经反

2009-03-14 15:37:57 5418

5418

锁存器,锁存器是什么意思

锁存器定义一位钟控D触发器只能传送或存储一位二进制数据,而在实际工作中往往是一次传送或存

2010-03-09 09:44:12 12791

12791 锁存器和缓冲器的作用是什么?

锁存器广泛用于计算机与数字系统的输入缓冲电路,其作用是将输入信号暂时寄存,等待处理,这一方

2010-03-09 09:48:02 25567

25567 地址锁存器,地址锁存器是什么意思

地址锁存器就是一个暂存器,它根据控制信号的状态,将总线上地址代码暂存起来。8086/8088数

2010-03-09 09:49:49 5250

5250 锁存器的原理分析

锁存器就是把单片机的输出的数先存起来,可以让单片机继续做其它事.. 比如74HC373就是一种锁存器 它的LE为高

2010-03-09 09:54:52 67812

67812 电压比较器,电压比较器是什么意思

电压比较器可以看作是放大倍数接近“无穷大”的运算放大器。

电压比较器的功能:比

2010-03-09 11:13:13 2107

2107 提出了一种应用于开关电容流水线模数转换器的CMOS预放大锁存比较器。比较器采用了交叉耦合负载、PMOS/NMOS比例优化和电容中和技术。该结构大幅提高了比较器的速度并有效抑制了回馈

2013-09-25 17:33:30 12

12 锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态 锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2017-11-02 09:24:41 95604

95604

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。锁存,就是把信号暂存以维持某种电平状态。锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题

2018-01-31 13:57:22 12766

12766

本文开始介绍了什么是锁存器与锁存器的工作原理,其次介绍了锁存器的作用与锁存器的应用实例,最后介绍了常用74系列锁存器芯片介绍。

2018-01-31 16:30:53 84093

84093

本文首先介绍了锁存器的工作原理,其次阐述了锁存器的作用,最后阐述了锁存器应用场合。

2018-08-21 18:57:52 92126

92126 当复位输入为假且锁存输入为真时,输出为真。无论锁存器输入如何,输出仍然是真实的,直到复位输入为真。

2019-02-11 08:00:00 6

6 锁存器(有时也称为S/R锁存器)是最小的存储器块。它们可以使用两个NOR逻辑门(S和R为高电平有效)或两个NAND门(输入为低电平有效)构建,并用于构建更复杂的锁存器和触发器。

2019-07-30 11:23:28 7318

7318

作者:电子工程师小李 1)锁存器 锁存器(latch)是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。 简单地说

2020-11-29 11:02:11 26377

26377 AD1317:带锁存过时数据表的超高速窗口比较器

2021-04-15 18:21:39 2

2 P0口作为分时复用接口,既要作为数据总线口,又要作为地址总线口 输出的低8位地址需要用8位锁存器锁存 ALE的下降沿将P0口输出的低8位地址锁存• 对于锁存器: ○ /OE为输出使能端 § /OE

2021-11-26 20:51:04 13

13 作为电路设计者,锁存器很多场合都会用到,今天和大家分析一下SR锁存器的原理。

2022-08-20 17:30:23 7981

7981

在这个项目中,我们将制作一个软锁存电路,通过按一个按钮来打开和关闭电子设备。该电路称为软锁存开关。软锁存电路与普通锁存电路不同,在软锁存器中,可以使用外部手段(按钮)改变开启和关闭状态,但在普通锁存

2022-08-25 16:32:47 6419

6419

用或非门组成的基本SR锁存器。

2023-02-27 10:29:42 11262

11262

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态,当Gate输入为高电平时,输入D透明传输到输出Q;当Gate从高变低或者保持低电平时,输出Q被锁存保持不变。锁存器是电平触发的存储器。

2023-03-23 14:48:54 4273

4273

锁存器(Latch)是一种基本的数字电路元件,用于存储二进制数字的状态信息,并能够在需要时通过加电或控制信号的作用保持状态。它通常由几个逻辑门组成,可以实现简单的存储、移位、计数等功能。锁存器在数

2023-04-09 18:45:34 11496

11496 锁存器(Latch)是一种对脉冲电平敏感的存储单元,它们可以在特定输入脉冲电平作用下改变状态。锁存,就是把信号暂存以维持某种电平状态。

2023-07-06 15:10:39 1884

1884

的霍尔效应锁存传感器,设计用于无刷直流电机应用的电子换向。该设备包括一个用于磁传感的片上霍尔电压发生器,一个放大霍尔电压的比较器,以及一个用于为噪声抑制提供开关滞后的施密特触发器,以及开集电极输出。一个

2022-09-15 13:03:03 0

0 的霍尔效应锁存传感器,设计用于无刷直流电机应用的电子换向。该设备包括一个用于磁传感的片上霍尔电压发生器,一个放大霍尔电压的比较器,以及一个用于为噪声抑制提供开关滞后的施密特触发器,以及开集电极输出。一个

2022-11-11 14:06:31 0

0 锁存器的工作原理 锁存器(latch)是一种用于存储和记忆数字信号的电路。它被广泛用于计算机和数字电子电路中,用于实现内存存储、寄存器和其他计算单元。 锁存器的工作原理是通过反馈电路和放大

2023-12-08 11:18:03 9264

9264 Diodes 公司 (Diodes) (Nasdaq:DIOD) 将 AH371xQ 系列高电压霍尔效应锁存器加入产品组合。

2024-01-05 13:52:22 1291

1291 集成的霍尔效应锁存传感器,设计用于无刷直流电机应用的电子换向。该设备包括一个用于磁传感的片上霍尔电压发生器,一个放大霍尔电压的比较器,以及一个用于为噪声抑制提供开关滞后的施密特触发器,以及开集电极输出。一个内部带隙调节器用于为内部电路提供温度补偿的电源电压,并允

2024-01-10 14:23:37 0

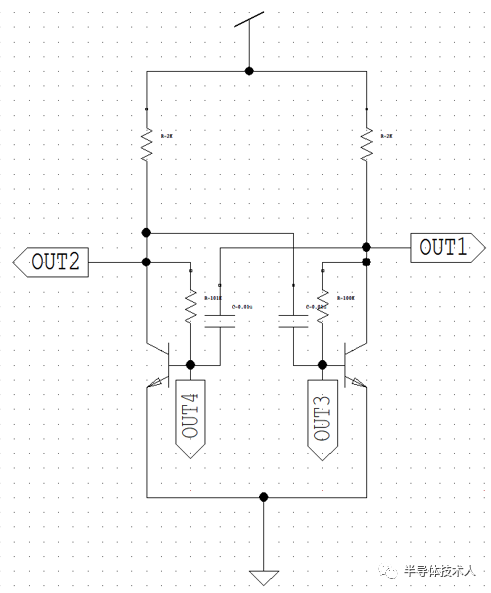

0 该专利揭示了一款高精度比较器,主要由预放大模块和比较锁存模块组成。预放大模块包含第一输入开关管、第二输入开关管、第一配合开关管、第二配合开关管、时钟开关管、第一反相器以及第二反相器。

2024-04-22 10:06:19 1122

1122

在数字电子学中,锁存器(Latch)和触发器(Flip-Flop)是两种基本的存储元件,它们在数字系统中扮演着至关重要的角色。它们的主要功能是存储和保持数据状态,以供后续处理。然而,它们在实现方式

2024-07-23 10:16:31 1093

1093 锁存器(Latch)是一种存储电路,用于存储一位二进制信息。锁存器在数字电路设计中非常常见,它可以用来保持数据状态、实现同步等功能。锁存器的工作原理和触发方式是数字电路设计的基础之一。 1. 锁存器

2024-07-23 10:17:50 1387

1387 在数字电路中,锁存器和触发器是两种非常重要的存储元件,它们在逻辑功能上有着明显的区别。锁存器和触发器都是用于存储二进制信息的基本元件,但它们在结构、工作原理、应用场景等方面都存在差异。 一、锁存器

2024-07-23 10:19:20 1892

1892 锁存器(Latch)是一种存储单元,用于存储一位二进制信息。在数字电路中,锁存器是一种基本的存储元件,广泛应用于寄存器、计数器、触发器等电路中。锁存器的原态和新态是描述锁存器状态变化的两个重要概念

2024-07-23 10:21:06 1532

1532 锁存器电路概述 定义与功能 锁存器(Latch)是数字电路中的一种基本存储元件,用于存储一个位(1或0)的状态。它能够在特定输入脉冲电平作用下改变状态,并保持该状态直到下一个脉冲电平到来。锁存器

2024-07-23 11:29:39 1073

1073 锁存器(Latch)是一种在数字电路中广泛使用的存储元件,它能够存储一位二进制信息。锁存器电路的触发方式有很多种,包括同步触发、边沿触发、电平触发等。 一、锁存器的基本概念 锁存器是一种具有记忆功能

2024-07-23 11:31:06 1263

1263 锁存器(Latch)是一种具有记忆功能的数字电路元件,用于存储和保持数字信号的状态。锁存器在数字电路设计中扮演着重要的角色,广泛应用于各种电子设备和系统中。本文将介绍锁存器的组成、功能及应用。 一

2024-07-23 11:32:56 5357

5357 RS锁存器和SR锁存器是数字电路中两种常见的存储单元,它们在功能和应用上有一些区别。 RS锁存器 RS锁存器,即Reset-Set锁存器,是一种具有两个稳定状态的存储单元。它有两个输入端,分别

2024-07-23 14:15:52 2983

2983 电子发烧友网站提供《DRV5011低电压数字锁存器霍尔效应传感器数据表.pdf》资料免费下载

2024-08-14 09:16:10 0

0 电子发烧友网站提供《AMC23C12-Q1汽车类快速响应增强型隔离式窗口比较器(具有可调阈值和锁存功能)数据表1kVPK 的工作电压。 比较器.pdf》资料免费下载

2024-08-15 09:19:31 0

0 锁存器(latch)是数字电路中的一种基本存储单元,用于存储和保持一个或多个位的状态。锁存器在数字逻辑设计中扮演着重要的角色,它们可以用于实现各种功能,如数据存储、信号同步、状态保持等。 锁存器

2024-08-28 09:09:00 2438

2438 锁存器(Latch)是一种存储设备,用于在数字电路中存储和保持数据。锁存器的主要作用是将输入信号的电平状态保持一段时间,直到下一个输入信号到来。锁存器在数字电路设计中具有广泛的应用,包括数据存储

2024-08-28 09:11:46 2927

2927 D锁存器是一种常见的数字逻辑电路,用于存储一个二进制位的状态。以下是一些常用的D锁存器型号及其特点: 74LS74:这是一种低功耗的正触发D锁存器,具有4个独立的锁存器。它具有数据输入、时钟输入

2024-08-28 09:13:51 2829

2829 D锁存器(Data Latch)和SR锁存器(Set-Reset Latch)是数字电路中常见的两种存储元件。它们在数字系统中扮演着重要的角色,用于存储和传递信息。然而,这两种锁存器在设计和应用上

2024-08-28 09:16:42 1796

1796 RS锁存器的R和S端分别代表 Reset(复位) 和 Set(置位) 端。 R(Reset)端 功能 :当R端接收到有效信号(通常是低电平,但具体取决于锁存器的实现方式,有时高电平也可能为有效信号

2024-08-28 10:25:27 2822

2822 端口锁存器和引脚是微控制器和数字电路中常见的概念,它们在硬件设计和编程中扮演着重要的角色。 端口锁存器 端口锁存器(Port Latch)是一种存储数字信号的电路元件,它通常用于微控制器或数字电路中

2024-08-28 10:36:47 1657

1657 RS锁存器(Reset-Set Latch)中的不定状态,是指在特定输入条件下,锁存器的输出状态变得不确定或不可预测的现象。这种不定状态主要源于RS锁存器的输入逻辑和电路特性,具体含义可以从以下几个

2024-08-28 10:42:09 2089

2089 SR锁存器是一种数字电路中常用的存储元件,它具有一些重要的功能和特点。以下是对SR锁存器功能的介绍: 存储功能 SR锁存器最基本的功能是存储信息。它有两个稳定状态,分别对应于“1”和“0”。当输入

2024-08-28 10:55:56 2493

2493 在深入探讨锁存器的输出时序时,我们需要详细分析锁存器在不同控制信号下的行为表现,特别是控制信号(如使能信号E)的电平变化如何影响数据输入(D)到输出(Q)的传输过程。以下是对锁存器输出时序的详细描述,旨在全面覆盖其工作原理和时序特性。

2024-08-30 10:43:44 1768

1768 在Verilog HDL中实现锁存器(Latch)通常涉及对硬件描述语言的基本理解,特别是关于信号如何根据控制信号的变化而保持或更新其值。锁存器与触发器(Flip-Flop)的主要区别在于,锁存器

2024-08-30 10:45:03 2394

2394 电子发烧友网站提供《具有比较器电路的过电流锁存电路.pdf》资料免费下载

2024-09-02 11:00:31 4

4 电子发烧友网站提供《锁存电压监控器(复位IC).pdf》资料免费下载

2024-09-18 10:34:52 0

0

电子发烧友App

电子发烧友App

评论