FM信号的解调电路--斜率鉴频器

频率检波就是从FM信号中检取出原调制信号。鉴频器是实现频率检波的装置。

鉴

2010-05-27 16:52:29 25206

25206

该应用笔记讨论了鉴频鉴相器的指标对锁相环(PLL)死区及抖动性能的影响。

2011-12-06 11:28:55 6745

6745

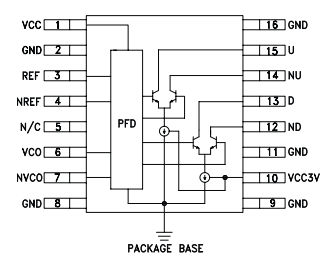

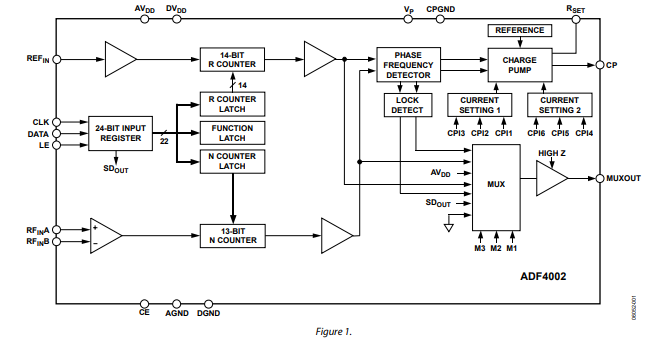

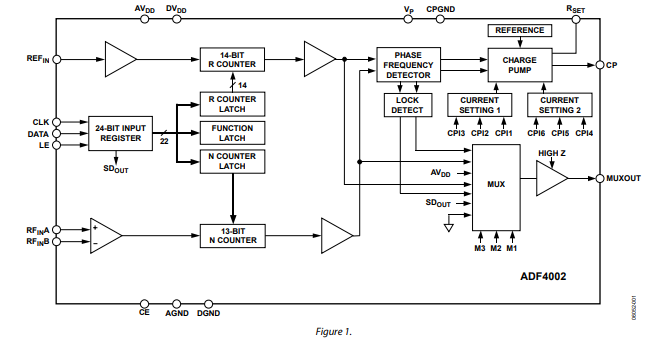

ADF4002由低噪声数字鉴频鉴相器(PFD)、精密电荷泵、可编程参考分频器和可编程N分频器组成。14位参考计数器(R计数器)允许PFD输入端的REFIN频率为可选值。如果频率合成器与一个外部环路滤波器和电压控制振荡器(VCO)一起使用,则可以实现完整的锁相环(PLL)。

2013-10-22 15:15:59 2039

2039

频率合成器的核心是鉴相器或鉴频鉴相器。在这里,将参考频率信号与VCO输出反馈的信号进行比较,产生的误差信号用于驱动环路滤波器和VCO。在数字PLL(DPLL)中,鉴相器或鉴频检波器是一个逻辑元件。三种最常见的实现是:

2023-01-30 10:19:07 2823

2823

在这篇文章中,我们将介绍鉴频鉴相器(PFD)的工作原理。

2023-11-22 14:49:09 10754

10754

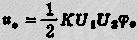

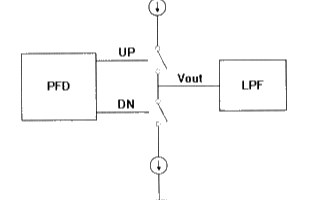

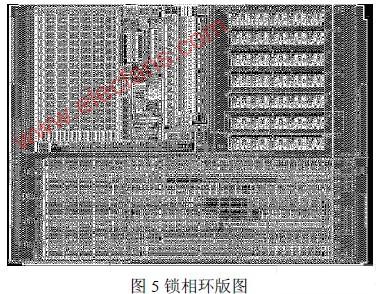

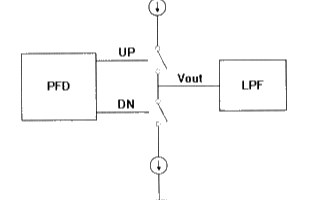

鉴相器+电荷泵(PFD+CP)是锁相环内部的重要结构,在通信系统、频率合成以及时钟信号生成中有着广泛的应用。鉴相器用于检测两个输入信号的相位差,电荷泵把鉴相器输出的相位差转换成电荷输送给滤波器,用于给后续的震荡器提供控制电压。本文将对鉴相器和电荷泵结构进行设计和优化。

2025-01-02 09:39:08 3718

3718

Hello! 请教个关于鉴相频率杂散与环路滤波器布线的问题。例如ADF4360,鉴相频率的杂散抑制的典型值为-70dBc左右,而实测为-60~-65dBc,也能接受,只是感觉各次倍频的鉴相频率太多

2018-11-07 09:03:01

ad9518-4,改芯片用过好多次,这次应用相噪要求较高,鉴相器工作频率20MHz。发现如下问题:

鉴相器工作频率20MHz下,环路滤波器带宽设置为250k、100k、50k都不能锁定;

环路滤波器

2023-12-06 06:51:29

求教各位大神有用过AD9901这款鉴相芯片吗,我用来检测两列信号的相位差。为什么我输入两列1MHZ占空比不同的方波,输出始终在直流4V左右,而不是我想得到的两列方波的异或输出。还有AD9901KQ和AD9901TQ哪个是TTL电平啊,有没有用过这款芯片的请赐教啊

2014-06-05 21:07:37

资料下载。希望大家喜欢哦! 本讲义涉及以下主题内容五种类型的频率合成什么是时钟? 常用频率是多少?锁相环(PLL)基本模型鉴频鉴相器(PFD) 驱动电荷泵(CP)数字PLL框图 —— 分频器PLL中输入

2018-10-26 09:16:36

`EV1HMC3716LP4数字鉴频鉴相器产品介绍EV1HMC3716LP4询价热线EV1HMC3716LP4现货EV1HMC3716LP4代理王先生***深圳市首质诚科技有限公司

2019-05-19 11:59:10

`HMC3716LP4E数字鉴频鉴相器产品介绍 产品名称:数字鉴频鉴相器 HMC3716LP4E特征 超低SSB相位噪底:-153dBc/Hz(10kHz偏置时,100MHz)集成输出电阻改善输入

2019-05-19 11:44:33

请问HMC704鉴相器能不能实现小数模式100M参考,100M鉴相,有用过的大神能不能指导一下?

2021-06-08 09:41:45

,即N为整数,则鉴相频率PFD=fvco/N,算出鉴相频率后AD9912再输出这个频率送至HMC的参考输入脚,鉴相频率范围为68MHz~72MHz,环路带宽为手册上推荐的90KHz,当输出频率变化小于

2019-02-22 12:27:30

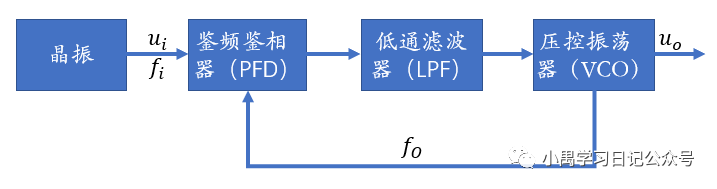

EF3 FPGA 内嵌 2 个多功能锁相环(PLL),可以实现时钟分频、倍频、占空比调整、输入和反馈时钟对准、多相位时钟输出等功能。PLL 的架构如图 1 所示,包含鉴频鉴相器(PFD)、压控振荡器(VCO)、低通滤波器(LPF)等基本电路。

2022-10-27 09:07:03

哪位可以提供一下mc1496用于锁相环鉴相器的电路实例?数据手册偏偏在这地方没有给具体的电路。

2011-04-05 14:37:12

multisim中没有高速鉴相器件AD9901,那么有什么方法可以解决此问题吗?是否可以用其他的器件代替,望大家不令赐教,谢谢!!

2015-01-30 15:37:37

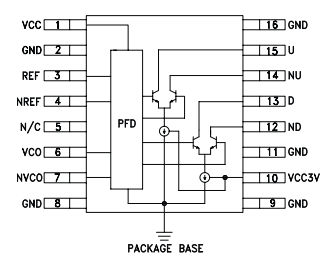

。该电路的第一个基本元件是鉴频鉴相器(PFD)。PFD将输入到REFIN的频率和相位与反馈到RFIN的频率和相位进行比较。ADF4002 是一 款可配置为独立PFD(反馈分频器N = 1)的PLL

2019-10-02 08:30:00

的经典数字PLL架构。图1.PLL基本配置该电路的第一个基本元件是鉴频鉴相器(PFD)。PFD将输入到REFIN的频率和相位与反馈到RFIN的频率和相位进行比较。ADF4002 是一款可配置为独立PFD

2019-01-28 16:02:54

为什么鉴相器之后要连接环路滤波器?

2014-03-24 14:02:20

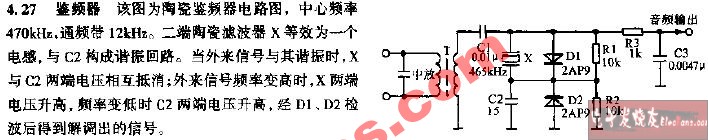

类型,前者用于同步鉴相器作平衡式鉴频解调,后者用于差分峰值鉴频器作差动微分式鉴频解调。德键调频音频窄带型JTCV10.7M系列贴片鉴频器,搭配多种IC应用于FM程序检验,转换频率为有用的音频信号。 调频

2013-12-17 17:58:19

正在做一个东西,里面需要用到LABVIEW的鉴相器的仿真但是没有思路,网上找的看不清楚,谁有文件希望让我参考一下,谢谢

2020-04-28 09:52:27

小白网上找了很多鉴相芯片都是最多到2π,有没有0~4π鉴相范围的芯片?

2015-04-16 22:29:52

小白网上找了很多鉴相芯片都是最多到2π,有没有0~4π鉴相范围的芯片?

2015-04-17 09:24:14

各位老师专家好,我刚接触这方面的东西有些不太明白的地方,谢谢大家的帮助。我想将AD8032用作鉴相器,有以下两个个问题:1、芯片鉴相输出端输出的信号是与两路输入信号相位差成正比的直流电压,还是 需要加环路滤波器才行;2、是否有实现鉴相功能的现成评估板,大概多少钱

2018-10-31 09:12:38

异或门鉴相器具有何种鉴相特性呢?

2023-04-24 11:39:05

根据一种雷达微波锁相本振的需要,本文作者研制了一个X波段的微波鉴频器。这个鉴频器的研制早在1989年就已完成,于1991年投入小批量生产。它的鉴频特性好,性能稳定可靠,在生产过程中已经表现出良好的社会效益和经济效益。

2019-08-20 07:25:39

我用DSP芯片发出两路有相位差的25KPWM方波进入CD4046的3脚和14脚,为什么沿上升沿触发的鉴相器2输出的13脚非常乱?仿真电路图如上传文件。。PS:CD4046用万用板搭的。

2012-11-15 20:53:29

相对光电编码器的鉴相和计数电路

2019-09-16 06:25:02

正常置数。以上是遇到的问题,由于印制板已投产,无法实现分别上电,请问如何在同时上电的情况下解决鉴相器SPI置数无效的问题,谢谢。

2018-08-22 08:23:13

一般经典的锁相环推导公式中鉴相器的鉴相灵敏度都是v/rad,那ADF4153的输出时电荷泵的电流,它和经典的鉴相器灵敏度之间有什么关系?该怎么计算它的鉴相器灵敏度?

2018-11-06 09:02:53

的?举例说明:鉴相频率50M,输出频率5015M,这个时候在5000M和5030M观察到杂散,约为-75dBc,同时输出信号的参考杂散也较强,约为-82dBc,请问有什么解决办法么?@

2019-02-15 13:26:51

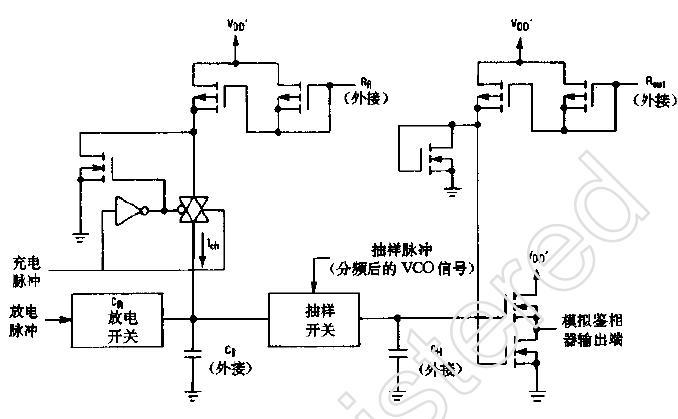

将模拟鉴相器输出与频率牵引输出相结合的方法

2019-09-26 09:00:59

带宽1MHz~3GHz或更宽,希望能同时鉴频鉴相,贵司大多RMS Responding Detector都不能鉴相。如果没有集成的芯片那就只好单独采用鉴相器了。

2018-08-09 08:55:13

有没有哪位大佬做过雷达中相位干涉仪中数字鉴相的模块呀

2019-03-30 20:58:50

模拟鉴相器逻辑图

2020-03-16 09:00:30

请问在电子电路中锁相环和鉴相器的电路结构是什么样的?它是如何实现此电路功能的?可否详细解释一下?

2024-02-29 22:34:45

有没有人做过鉴频鉴相器的仿真?

2014-08-14 20:31:18

难道说鉴相器也有鉴频的功能吗?假设初始状态我的参考频率和vco的自由震荡频率不一样,电路是怎样达到使频率相等的平衡状态的呢,我觉的不太好理解,因为这是2个不同频率的信号输入鉴相器,这怎么比较相位差啊。。

求高手指点一下

2023-04-24 10:33:47

鉴相器电路

2008-08-04 14:06:52 210

210 针对数字鉴频鉴相器的相位噪声较高的缺点,本文设计了一种低噪声模拟鉴相器,并提出了一种双鉴频鉴相器结构,将模拟鉴相器和数字鉴频鉴相器有机地结合在一起。在锁相环中,该结

2010-07-29 15:34:51 76

76 介绍一种由复杂可编程逻辑器件(CPLD)实现的相位法激光测距用数字鉴相器的设计方案,给出原理图及部分模块的仿真结果。由于CPLD具有高速度和高带宽等优点,因此,本方案较之单

2010-08-03 15:37:49 78

78 本文探讨鉴频鉴相器(PFD)设计中死区的产生原因和消除方法。设计了一种用于高速锁相环的零死区PFD。这种PFD采用无反馈回路结构,在保证死区为零的前提下,兼顾功耗和速度性

2010-08-04 11:39:23 42

42 PFD1K-鉴频鉴相器具有双40 GHz预分频器的8 GHz相位频率检测器ICPFD1K是一款具有全差分输入和输出的高频相频检测器。它具有双7位高速预分频器,允许PFD1K在

2024-02-29 13:56:31

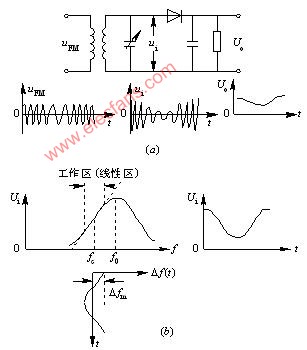

相位鉴频器实验

一、实验目的 1 .了解实现鉴频的基本方法。 2 .熟悉电容耦合式相位鉴频电路的基本工作原理。 2 、熟悉鉴频

2008-10-21 12:54:28 9078

9078

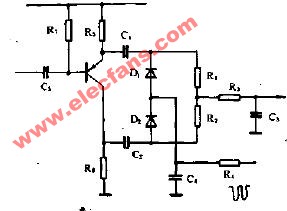

鉴频器电路

2009-03-14 14:58:38 1760

1760

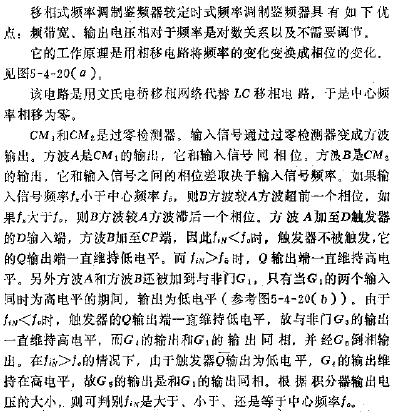

移相式鉴频器

2009-04-13 11:05:55 1838

1838

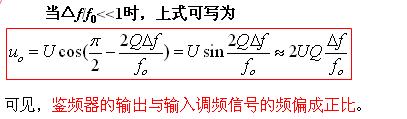

振幅鉴频器原理

鉴频方法的分类 (1) 直接鉴频法:是直接从调频信号的频率中提取原来调制

2009-06-29 10:56:20 8438

8438

乘积型相位鉴频原理

乘积型相位鉴频器实际上是一种正交鉴频器,它由移相网络、乘法器和低通滤波器三部分

2009-06-29 11:19:32 10912

10912

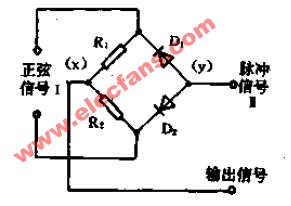

双脉冲型鉴相器电路

如图是电视机使用的双脉冲平衡型

2009-08-05 12:25:43 3523

3523

桥式鉴相器电路

如图所示的电路是一种桥式

2009-08-05 12:29:40 3481

3481

鉴相器频率在20M时的频谱

鉴相器频率在1M时的频谱,旁瓣如图标示:

2009-09-03 08:19:56 2357

2357 模拟鉴相器逻辑图

2009-09-05 10:44:48 3480

3480

正交鉴频器,正交鉴频器原理是什么?

乘积型相位鉴频(或称正交鉴频器,或称差动峰值鉴频器)

2010-03-22 15:56:43 6658

6658 斜率鉴频器,斜率鉴频器电路及原理

①单失谐回路斜率鉴频器

电路

2010-03-22 15:58:51 16547

16547 鉴相器 ,鉴相器的分类和原理是什么?

鉴相器

鉴相器,顾名思义,就是能够鉴别出输入信号的相差的器件。它是PLL的重要组成部分。

PLL的概念

2010-03-23 10:55:54 18391

18391 数字鉴相器,数字鉴相器原理是什么?

背景知识:

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副载

2010-03-23 15:10:25 11617

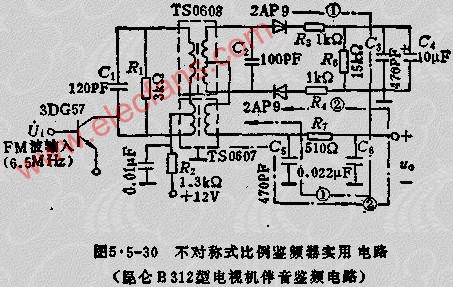

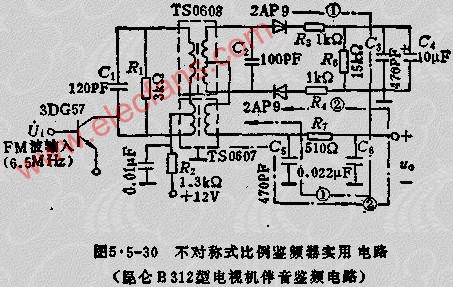

11617 FM信号的解调电路--比例鉴频器

斜率鉴频器和相位鉴频器的共同缺点是鉴频输出电压不仅与输入信号的瞬时频率有关,而且还与输入信号的振幅有关。因此,

2010-05-27 18:01:26 9773

9773

PM信号的解调电路--集成鉴相器

该种鉴相器电路与图5.5-18B、C采用集成模拟乘法器组成的乘积检波器

2010-05-28 14:30:49 2486

2486

1 引言

本文在传统锁相环结构的基础上进行改进,设计了一款用于多路输出时钟缓冲器中的锁相环,其主 要结构包括分频器、鉴频鉴相器(PFD)、电荷泵、环路滤波器

2010-08-17 15:33:59 1683

1683

摘要! 就如何使用单片机对旋转增量编码器鉴相进行了研究! 给出了常用的鉴相算法以及识 别毛刺#的方法!并通过在!AVR单片机上编程验证了所给出的鉴相方法$

2011-03-30 10:16:50 387

387 就如何使用单片机对旋转增量编码器鉴相进行了研究! 给出了常用的鉴相算法以及识别毛刺的方法!并通过在单片机上编程验证了所给出的鉴相方法

2011-08-25 15:40:55 143

143 AD9548是一款配有直接数字频率合成器(DDS)的数字PLL,其中DDS的作用相当于模拟PLL中的VCO。由于AD9548的数字特性,设计人员还可以实现数字鉴频鉴相器

2011-11-24 14:29:11 58

58 鉴相器的技术应用和鉴相器的设计资料。

2015-10-29 15:24:19 17

17 一种基于bang_bang鉴频鉴相器的全数字锁相环设计_陈原聪

2017-01-07 20:49:27 11

11 低杂散锁相环中鉴频鉴相器与电荷泵的设计_李森

2017-01-07 22:14:03 3

3 一、引言 根据一种雷达微波锁相本振的需要,本文作者研制了一个X波段的微波鉴频器。这个鉴频器的研制早在1989年就已完成,于1991年投入小批量生产。它的鉴频特性好,性能稳定可靠,在生产过程中已经

2017-12-07 18:24:02 1556

1556

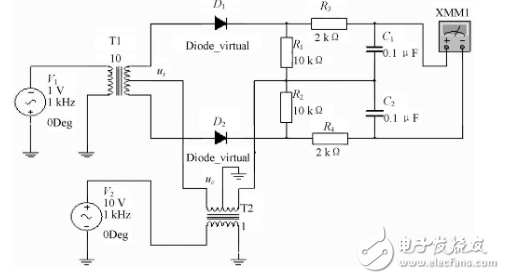

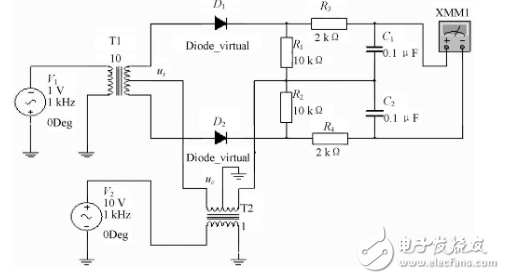

本文主要介绍了相敏检波器的鉴相特性。相敏检波电路的鉴相特性为:输出电压为正时,表示输入的调幅信号us与参考信号(即载波信号)uc(或Uc)同相,此时调制信号为正(或负);当输出电压为负时,表示输入

2018-03-15 12:40:35 31778

31778

性能直接决定系统各项指标的好坏。典型CPPLL频率合成器由鉴频鉴相器(Phase Frequency Detector,PFD)、电荷泵(CP)、环路滤波器(LPF)、压控振荡器(VCO)和可编程分频器(DIV)组成,如图1所示。

2018-06-21 09:29:00 12493

12493

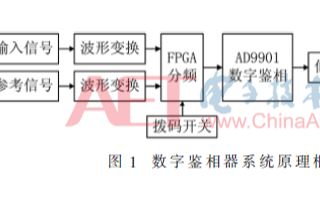

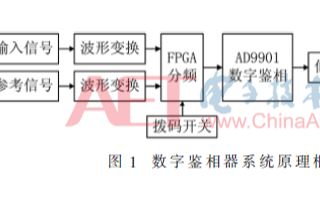

鉴相技术是电力电子系统和测试控制中的关键技术之一,在仪器仪表、通信、导航定位、研究网络相频特性和锁相环等测试中,经常需要测量两列同频信号的相位差。相较于模拟鉴相器,数字鉴相器的突出优点在于提供的鉴相范围更宽,从而使鉴相更可靠,适用范围也更广。

2018-06-28 11:53:00 6941

6941

鉴幅鉴相漏电保安器和脉冲型漏电保护器相比,具有保护灵敏度高的优点。但如何在保证灵敏度高的前提下, 提高其动作的可靠性和准确性成为衡量这类产品性能的一个重要指标。本文成功的采用PIC16C711A

2020-11-06 17:32:59 5

5 PLL 频率合成器基本构建模块 PLL 频率合成器可以从多个基本构建模块的角度来考察。我们在前面已经提到过这个问题,下面将更加详细地进行探讨:鉴频鉴相器(PFD) 参考计数器(R) 反馈计数器(N

2020-12-03 01:47:00 21

21 图l是典型的电荷泵结构。此处电荷泵为两个受鉴频鉴相器(PFD)输出信号控制的开关电流源,它与后面的环路滤波器共同作用,将PFD的逻辑信号转化为电压信号,该电压信号进而调节压控振荡器的振荡频率。

2021-03-11 09:30:07 5154

5154

AD8302: 2.7GHz RF / IF增益鉴相器 数据手册

2021-03-20 10:57:43 9

9 AD9901:超高速鉴相器/鉴频器数据表

2021-04-19 09:36:22 16

16 鉴相器作为环路的关键模块,主要鉴别参考频率和反馈信号的相位关系,对于环路精度和频率捕捉范围起到决定性作用。

2023-04-24 15:37:43 24325

24325

鉴相器作为环路的关键模块,主要鉴别参考频率和反馈信号的相位关系,对于环路精度和频率捕捉范围起到决定性作用。

2023-05-02 16:20:00 3188

3188

为什么叫Bang-Bang鉴相器? Bang-Bang鉴相器是用于判定和测量蒸汽锅炉和燃煤锅炉烟气中含有的油烟,黑烟和粉尘等污染物的一种设备。它是由美国火力设备公司(Honeywell)研发的一种

2023-09-20 16:23:36 2011

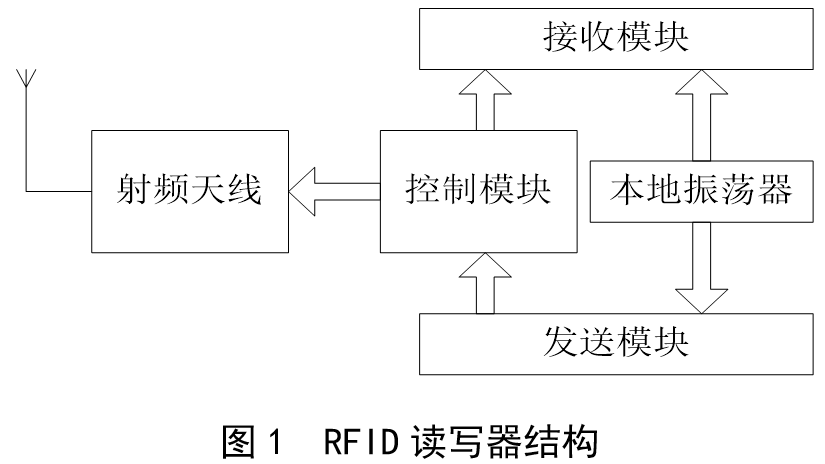

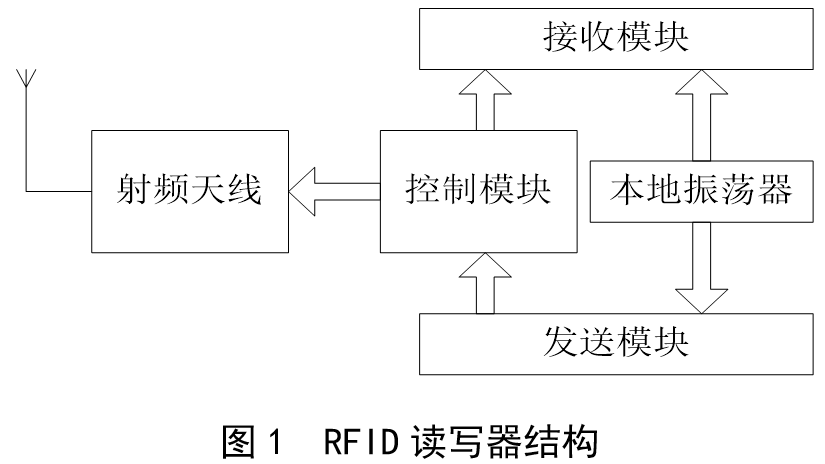

2011 介绍了一种用于射频识别(Radio Frequency Identification,RFID)系统读写器的数字鉴相器(DPFD)工作原理及其应用,并结合二分频率搜索方案,实现对数控振荡器频率预设字

2024-08-13 17:01:12 113

113

鉴相器是一种重要的电子元件,广泛应用于信号处理、通信系统和测量仪器中。它的主要功能是比较两个信号的相位差,并输出与相位差相关的信号。本文将详细介绍鉴相器的基本概念、工作原理、类型、技术参数及其应用领域,帮助您更好地理解这一关键组件。

2024-10-05 13:38:30 4131

4131 HMC439QS16G(E)是一款数字鉴相鉴频器,适合低噪声相位锁相环应用,输入频率10至1300 MHz。 它将高工作频率和超低相位噪底结合在一起,能够提供具有很宽环路带宽的合成器和低分频数,从而

2025-04-17 15:39:11 754

754

ADF4002频率合成器用来在无线接收机和发射机的上变频和下变频部分实现本机振荡器。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵、可编程参考分频器和可编程N分频器组成。14位参考分频器(R分频器)允许PFD输入端的REF~IN~频率为可选值。

2025-04-27 09:48:25 1238

1238

电子发烧友App

电子发烧友App

硬声App

硬声App

2039

2039

2823

2823

3718

3718

76

76 78

78 42

42 18391

18391 11617

11617 9773

9773

1683

1683

387

387 143

143 58

58 1556

1556

31778

31778

12493

12493

6941

6941

5

5 21

21 5154

5154

2011

2011 113

113

4131

4131 754

754

1238

1238

评论