为简化和加速复杂IC的开发,Cadence 设计系统公司 (NASDAQ:CDNS) 今天推出Tempus™ 时序签收解决方案。这是一款新的静态时序分析与收敛工具,旨在帮助系统级芯片 (SoC) 开发者加速时序收敛,将芯片设计快速转化为可制造的产品。

2013-05-21 15:37:37 3256

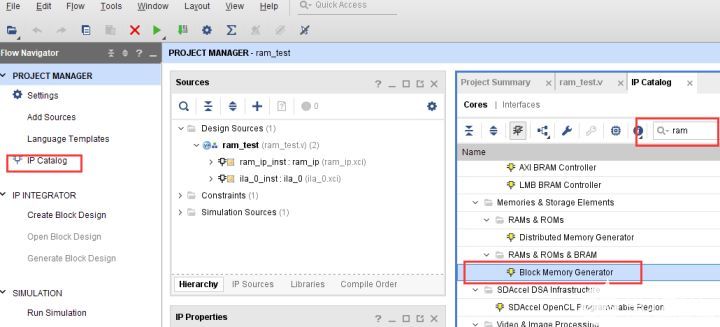

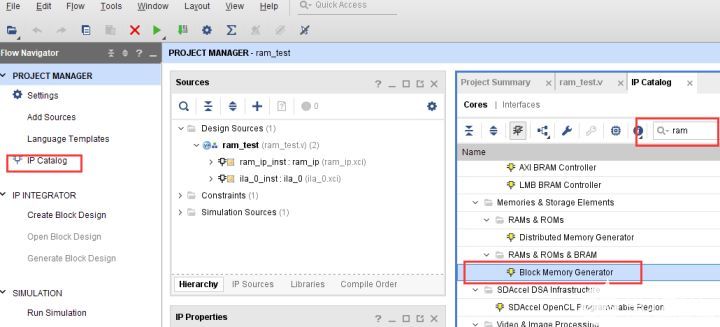

3256 RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

2021-01-22 09:43:11 5909

5909

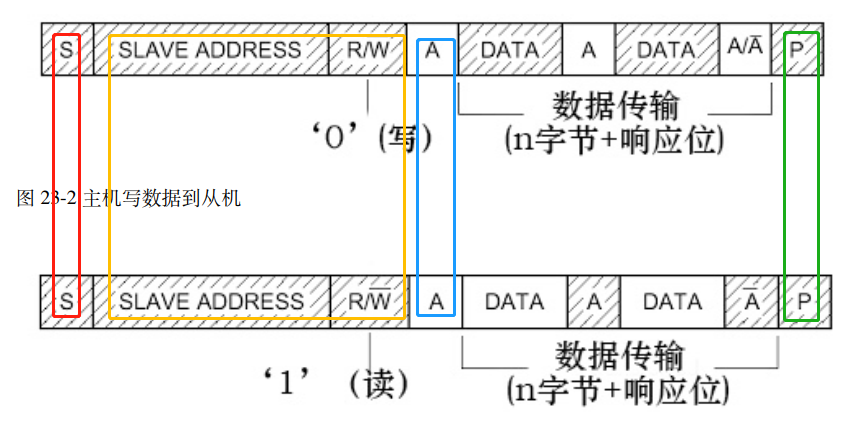

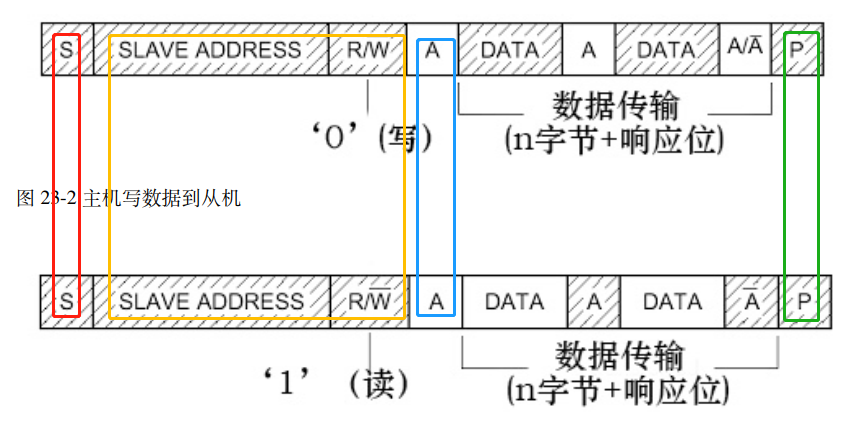

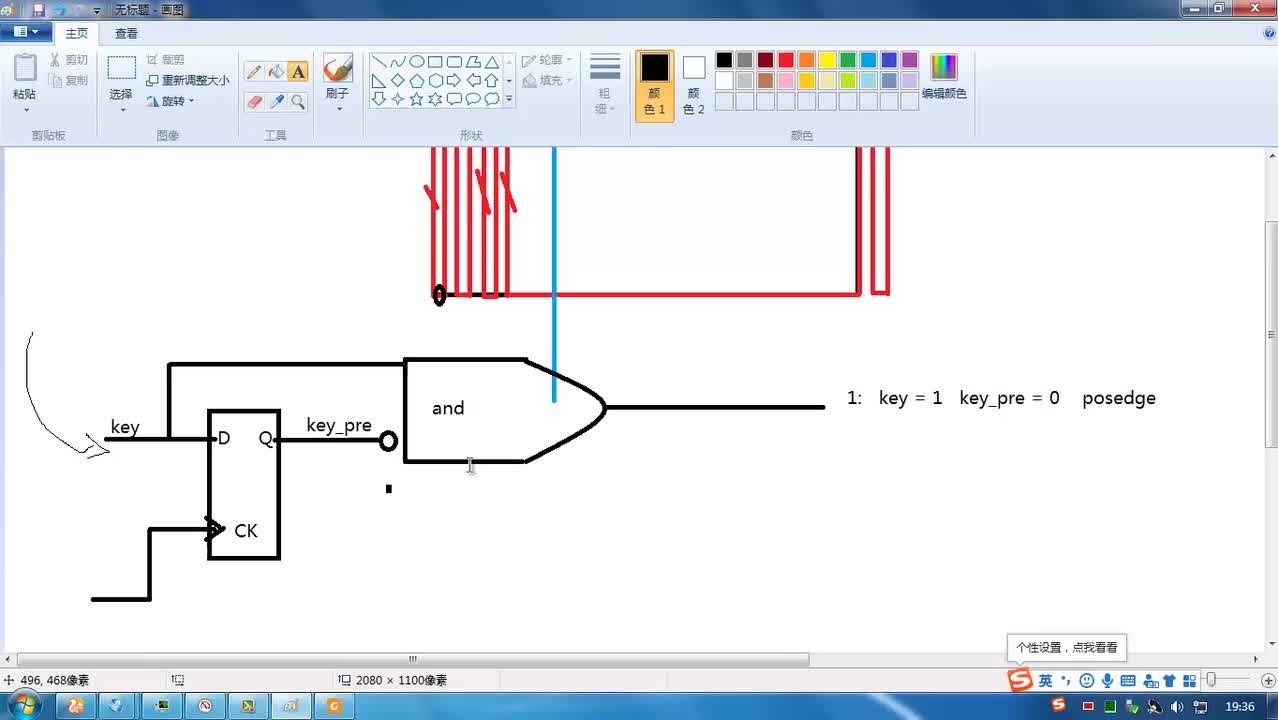

上篇推文对I2C总线的特性进行了介绍和描述。对于开发者而言,最重要的是编码I2C的读写时序驱动。本篇推文主要总结和分享I2C总线主机端通信的编程实现思路,并不对应特定MCU的硬件I2C外设,此处需要加以区分。

2023-10-01 16:54:00 3902

3902

WebAssembly (Wasm) 正在成为一个广受欢迎的编译目标,帮助开发者构建可迁移平台的应用。最近 Greptime 和 WasmEdge 协作,支持了在 WasmEdge 平台上的 Wasm 应用通过 MySQL 协议读写 GreptimeDB 中的时序数据。

2023-12-22 11:03:26 1731

1731 ram也叫主存,是与cpu直接交换数据的内部存储器。它可以随时读写(刷新时除外)且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。ram工作时可以随时从任何一个指定的地址写入

2020-12-16 06:29:16

ram也叫主存,是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外)且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。ram工作时可以随时从任何一个指定的地址写入

2020-12-10 15:50:38

ram也叫主存,是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外)且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。ram工作时可以随时从任何一个指定的地址写入

2020-12-31 06:18:55

DS1302数据读写时序图

2012-08-05 21:34:50

DS2411的读写时序和DS18B20一致,毕竟同一个公司出的。下面是代码源文件 ds2411.c#include "ds2411.h"#include "

2022-01-17 07:04:16

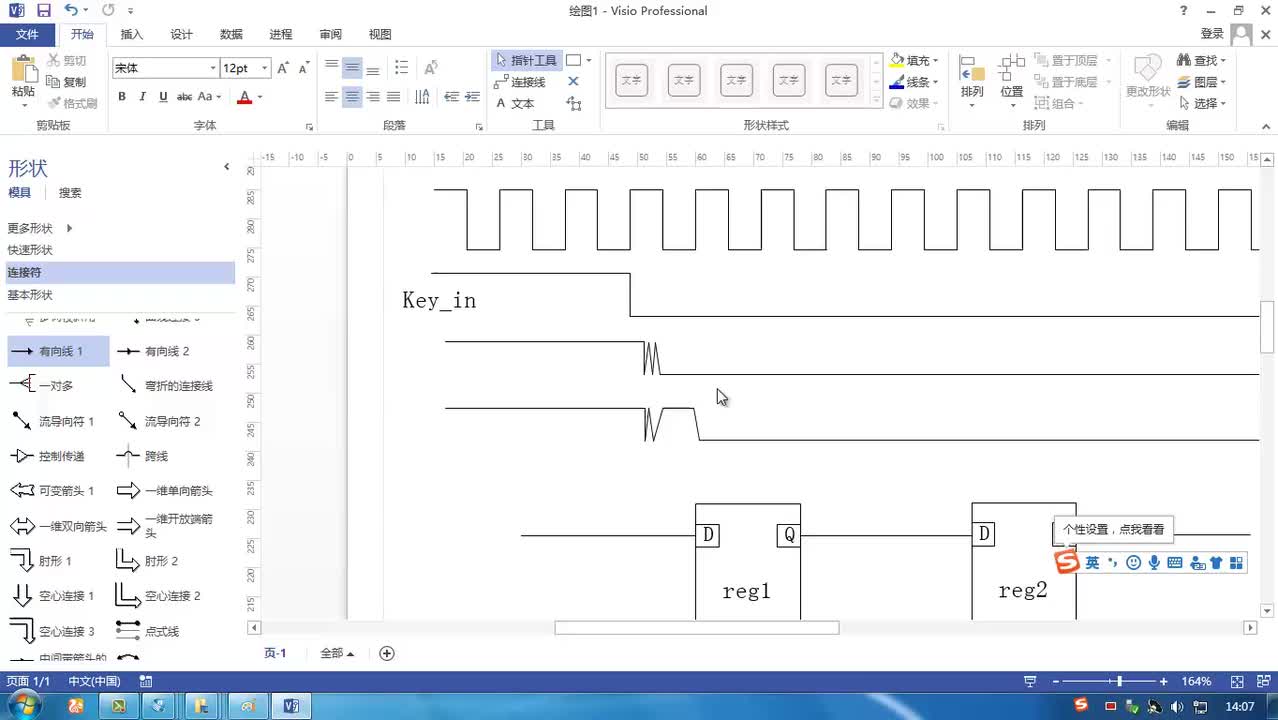

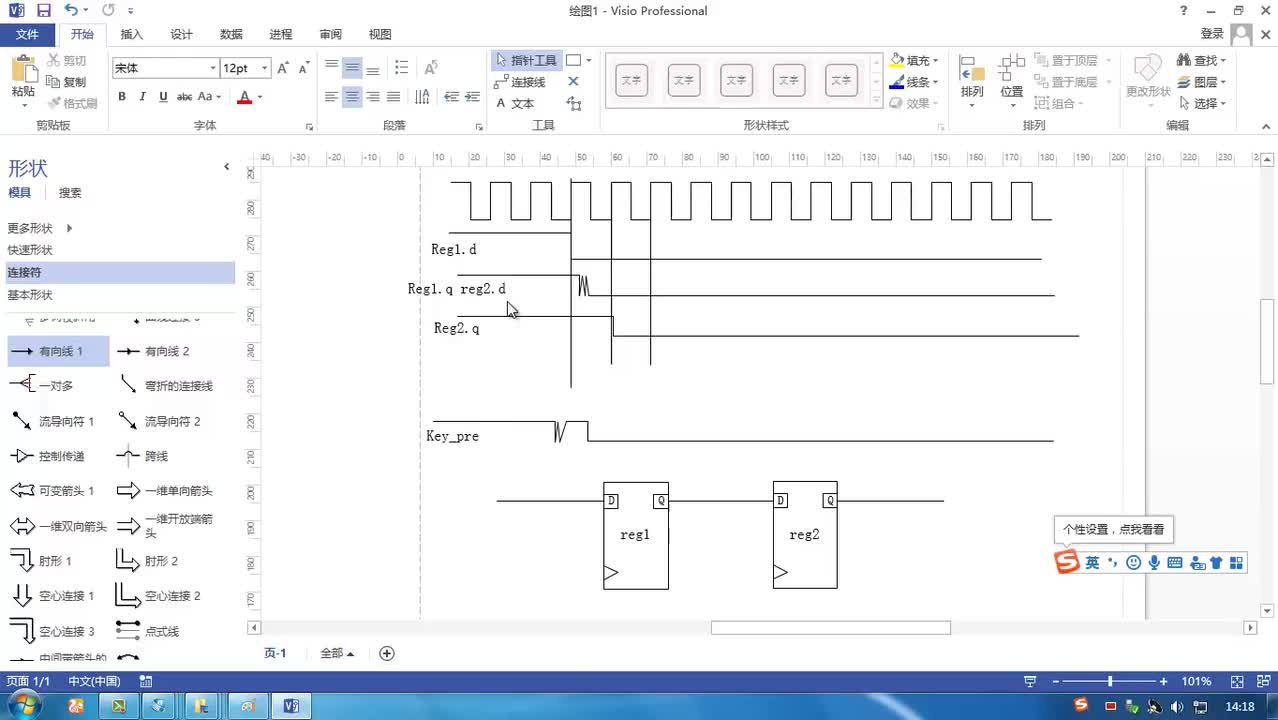

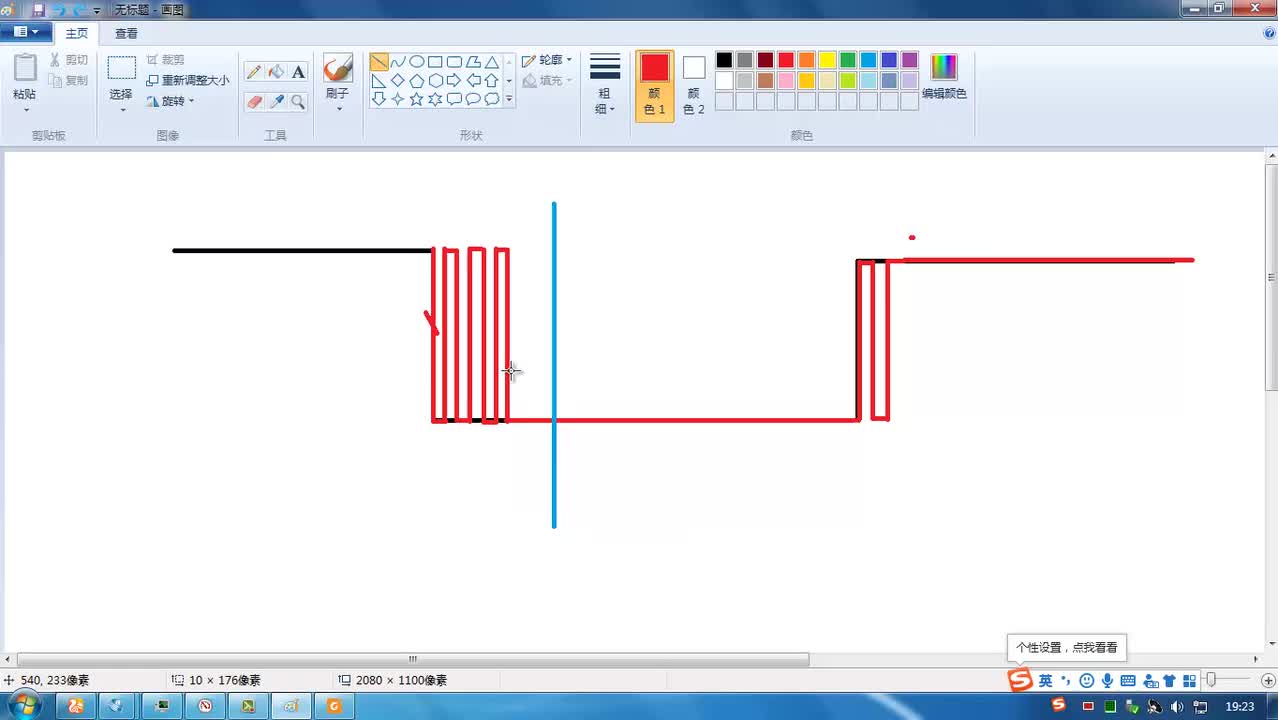

大佬们,求助一下。下面两张图是正常的读写时序和非正常读写时序。非正常读写时序中,发现数据保持长度比较短,而且AED在无效时应该为高阻态,有问题的那块板子,在无效时,AED为0

2019-12-24 15:42:02

文章目录EEPROM介绍EEPROM 单字节读写操作时序EEPROM 写数据流程EEPROM 读数据流程EEPROM介绍在实际的应用中,保存在单片机 RAM 中的数据,掉电后就丢失了,保存在单片机

2022-01-26 06:43:52

文章目录EEPROM 多字节读写操作时序EEPROM 多字节读写操作时序我们读取 EEPROM 的时候很简单,EEPROM 根据我们所送的时序,直接就把数据送出来了,但是写 EEPROM 却没有

2021-11-24 07:01:10

I2C读写时序I2CI2C写时序I2C读时序I2CI2C 总线上的每一个设备都可以作为主设备或者从设备,而且每一个设备都会对应一个唯一的地址(可以从 I2C 器件数据手册得知),主从设备之间就是通过

2022-01-18 07:30:22

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

看了芯片使用手册,没有看到,对其读写时序很模糊,求高手指导,谢谢

2012-07-10 22:10:27

目录0 引言1 SDIO接口1.1 SDIO接口有什么用?1.2 SDIO的功能框图1.3 SDIO的命令与响应1.4 SDIO数据块读写时序1.5 SDIO常用寄存器1.6 SD卡初始化流程

2022-02-21 06:58:01

SLE4442卡的读写时序,也是下降沿读,上升沿写吗???求大神解惑!!!

2013-12-12 17:04:09

STM32 Cubemax(十三) ——SPI时序读写RFID-RC522目录STM32 Cubemax(十三) ——SPI时序读写RFID-RC522前言一、SPI时序通信二、模块接线三

2022-02-08 06:13:14

用 NFC 技术可提高流程效率并优化成本。为了满足这些市场需求,意法半导体提供了 ST25 NFC读写器和标签,用于设计先进的集成式读写器+标签NFC 解决方案。意法半导体将为这一强大而安全的集成方案提供专业支持。

2023-09-13 06:01:57

分析IS62WV51216BLL的读写时序图和时间特性参数,得到较合理的时间参数,大大优化了外部RAM的操作时间。下面先介绍下前面3个参数:1.Address setup time: 从设置引脚地址开始到能够读取数据的时间段2.Data setup time: 设置完地址后,能够读取数据总线的时间段3.Bus

2021-12-03 06:43:54

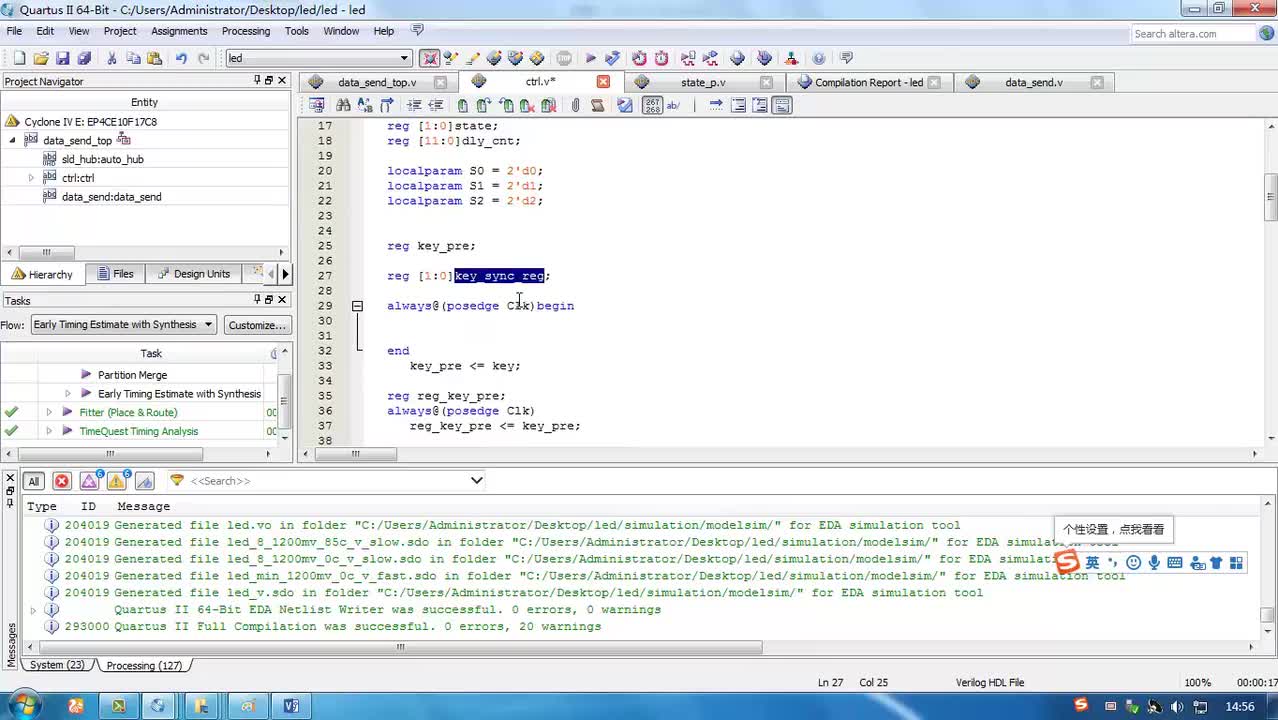

的读写时序。 2 模块划分本实例工程模块层次如图所示。●Pll_controller.v模块产生FPGA内部所需时钟信号。●Ram_test.v模块例化FPGA片内RAM,并产生FPGA片内RAM读写

2016-01-20 12:28:28

的在线逻辑分析仪chipscope,我们可以观察FPGA片内ROM、FIFO和RAM的读写时序,也可以只比较ROM预存储的数据和RAM最后读出的数据,确认整个读写缓存过程中,数据的一致性是否实现。 2

2016-03-16 12:43:36

逻辑分析仪chipscope,我们可以观察FPGA片内ROM、FIFO和RAM的读写时序,也可以只比较ROM预存储的数据和RAM最后读出的数据,确认整个读写缓存过程中,数据的一致性是否实现。 2 模块

2019-01-10 09:46:06

问题是这样的,单片机读取外部ram时候,通过movx读写指定地址,单片机自动配置wd rd P0 以及ale口。并且自动产生读写时序。那么有没有可能用单片机A来模拟一种时序,让单片机B通过movx来读取。所以想问问大家,这种做法有没有可能实现

2017-03-23 23:40:55

求助:ddr2 ram,256M,64位位宽,突发长度为4时,读写地址如何提供。 1. 提供给控制器的数据是上升沿和下降沿的拼接,一个周期提供两个数据到app_wdf_data,位宽为128位。那么

2013-09-29 21:48:53

spi读写时序里,图中圆圈处MISO和MOSI为什么不一样代表什么时序

2017-04-09 20:29:25

单片机读写U盘开发方案 u***dll.com 非 51MCU+***/CH735 ,单芯片实现* 支持FAT32,FAT16* 是块写数据,延长U盘寿命*一般

2009-01-17 10:12:34

本帖最后由 runileking 于 2016-4-14 17:56 编辑

RAM1和RAM2是两个一样的IP核,两个时序一样,见图,为什么RAM1可以正确读写,RAM2读不出数据?

2016-04-14 17:13:24

鸟人我找不到TFT读写命令时序的说明, 目前只有在程序里看的求贴士。。。。

2020-08-06 06:09:37

本文一方面旨在找到正确解决方案并选择最合适的电源管理产品,另一方面则是如何优化实际解决方案以用于FPGA。找到合适的电源解决方案寻找为FPGA供电的最佳解决方案并不简单。许多供应商以适合为FPGA

2019-05-05 08:00:00

基于Blackfin的解决方案 针对ADSP-BF706 BLACKFIN+处理器的EVWSS软件架构基于SigmaDSP的解决方案

2021-01-21 06:25:57

简介 电源时序控制是微控制器、FPGA、DSP、ADC和其他需要多个电压轨供电的器件所必需的一项功能。这些应用通常需要在数字I/O轨上电前对内核和模拟模块上电,但有些设计可能需要采用其他序列

2018-09-30 16:01:35

在VIVADO里为我们已经提供了RAM的IP核, 我们只需通过IP核例化一个RAM,根据RAM的读写时序来写入和读取RAM中存储的数据。实验中会通过VIVADO集成的在线逻辑分析仪ila,我们可以观察

2021-01-07 16:05:28

使用NVRAM的简单解决方案

2021-01-13 06:56:35

nRF24L01+ 2.4GHz无线收发器的主要特性有哪些?如何使用SPI?如何对SPI的操作时序进行读写呢?

2021-12-20 06:32:33

早上好,来自西班牙的每个人,这里是一个棘手的问题,我需要填补(几乎)8Mbit RAM(1Mx8)与传入的ADC数据,然后处理它。当我正在读DMA规范时,似乎有64K的页面限制,即当较低的16比特从

2019-08-02 07:49:48

SPI协议是什么?如何去实现SPI时序协议的基本读写呢?

2021-12-20 06:43:04

STM32F103的FSMC硬件有哪些呢?怎样以代码形式去说明LCD的读写时序呢?

2021-10-29 06:26:30

画中画的效果。在调试DDR3的过程中,我有一些高速存储器的使用心得,特分享给大家。首先我先介绍一下SDRAM存储器的读写时序。SDRAM即同步动态随机存储单元,主要用来存储较大容量的数据。我们都知道,数据

2020-01-04 19:20:52

方案1、分配两个独立显存区——A和B,显示A区时写B区准备,完成B区准备后,设定控制器显示B区,交替循环更新

方案2、客户MCU 的TFT控制器资源是否有类似的 “TE”信号可以监测,根据“TE

2025-12-29 09:07:56

进行监控。当所有电压建立之后,时序控制器电路产生电源良好信号。模拟时序控制解决方案(如ADM1186-1)很容易使用。它们具备多电压系统所需的全部功能。模拟时序控制器与数字时序控制器的不同之处在于,前者

2021-04-12 07:00:00

;_00000000_00000000,然后再发送16bit的sclk来读取寄存器数据,但是读取到的数据是adc的转换数据,并且写入也没成功,看过spi的时序是对的,想请问这个期间的读写时序是怎么样的

2024-11-21 08:23:51

51 系列单片机慢速读写的时序扩展

2009-05-15 14:28:16 18

18 SRAM的简单的读写操作教程

SRAM的读写时序比较简单,作为异步时序设备,SRAM对于时钟同步的要求不高,可以在低速下运行,下面就介绍SRAM的一次读写操作,在

2010-02-08 16:52:39 140

140 LSI 公司与Zarlink半导体日前宣布联合推出一款解决方案,该解决方案预集成了 Zarlink 的时序分组 (TOP) 专业技术和 LSI Axxia通信处理器系列产品,可大幅加速产品上市进程,并显著简化网络 OEM 厂商的集成工作。

2011-03-15 09:12:32 2635

2635 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。

2014-08-15 14:22:10 1476

1476 单片机扩展外部ROM或RAM读写时序,PPT介绍。

2016-12-12 21:36:19 9

9 关键词:MEMS , OCXO , Emerald , 5G时序 , SiTime SiTime 公司今天宣布推出 Emerald Platform,这是一款革命性的高精度时序解决方案,解决 5G

2019-04-06 16:45:58 933

933 对于mig与DDR3/DDR2 SDRAM的读写时序我们不需要了解太多,交给mig就可以了。

2019-03-03 11:11:53 6929

6929

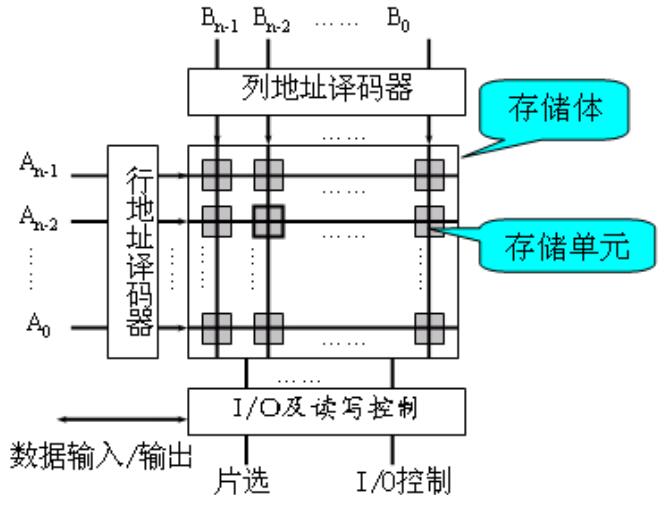

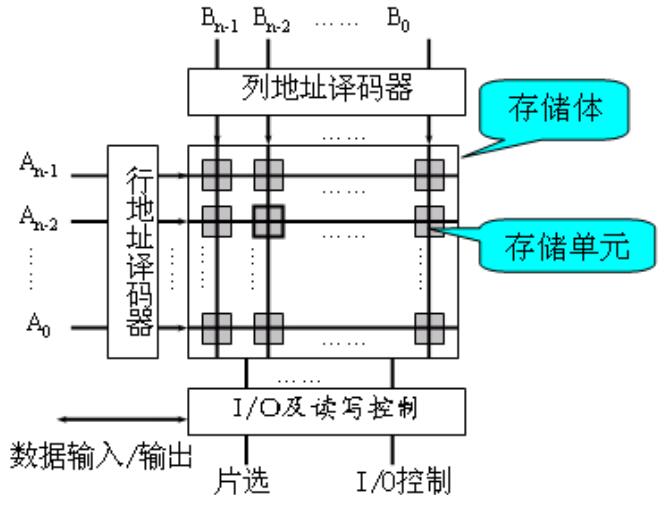

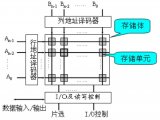

随机存取存储器也叫主存,是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外),而且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。RAM工作时可以随时从任何一个指定的地址写入(存入)或读出(取出)信息。

2019-09-10 06:03:00 3585

3585

ram也叫主存,是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外)且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。ram工作时可以随时从任何一个指定的地址写入

2020-12-09 14:25:05 17047

17047

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

2022-02-08 15:50:49 16174

16174

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

2021-03-15 06:09:45 14

14 文章目录EEPROM 多字节读写操作时序EEPROM 多字节读写操作时序我们读取 EEPROM 的时候很简单,EEPROM 根据我们所送的时序,直接就把数据送出来了,但是写 EEPROM 却没有

2021-11-16 14:21:05 9

9 STM32入门开发: 采用IIC硬件时序读写AT24C08(EEPROM)

2021-11-21 13:51:04 47

47 分析IS62WV51216BLL的读写时序图和时间特性参数,得到较合理的时间参数,大大优化了外部RAM的操作时间。下面先介绍下前面3个参数:1.Address setup time: 从设置引脚地址开始到能够读取数据的时间段2.Data setup time: 设置完地址后,能够读取数据总线的时间段3.Bus

2021-11-23 17:36:41 21

21 时序的,本文采用的是模拟时序,下篇文章就介绍配置STM32的IIC硬件时序读写AT24C02和AT24C08。模拟时序更加方便移植到其他单片机,通用性更高,不分MCU;硬件时序效率更高,单每个MCU配置方法不同,依赖硬件本身支持。目前器件: 采用AT24C02 EEPROM存储芯...

2021-11-25 20:06:02 39

39 提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档文章目录前言一、EC RAM是什么?二、使用步骤1.高级配置和电源接口(ACPI)规范2.EC RAM读写过程总结前言提示:这里可以

2021-12-04 11:36:12 27

27 STM32 Cubemax(十三) ——SPI时序读写RFID-RC522目录STM32 Cubemax(十三) ——SPI时序读写RFID-RC522前言一、SPI时序通信二、模块接线三

2021-12-04 20:36:09 55

55 ram也叫主存,是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外)且速度很快,通常作为操作系统或其他正在运行中的程序的...

2022-01-25 20:03:25 1

1 新思科技近日宣布与Ansys联合开发的电压时序签核解决方案已获三星采用,用以加速开发其具有理想功耗、性能和面积(PPA)的高能效比设计。

2022-04-24 15:27:02 1958

1958 该联合解决方案基于新思科技的行业金牌PrimeTime签核技术和Ansys 的RedHawk-SC电源完整性签核技术,能够防止动态电压降引起的时序失效并尽可能减小时序悲观性。

2022-04-27 14:29:22 1502

1502 本文介绍了在低功耗系统中降低功耗同时保持测量和监控应用所需的精度的时序因素和解决方案。它解释了当所选ADC是逐次逼近寄存器(SAR)ADC时影响时序的因素。对于Σ-Δ(∑-Δ)架构,时序考虑因素有所不同(请参阅本系列文章的第1部分)。本文探讨了模拟前端时序、ADC时序和数字接口时序中的信号链考虑因素。

2022-12-13 11:20:18 2663

2663

。本来的含义是:ROM是Read Only Memory的意思,也就是说这种存储器只能读,不能写。而RAM是Random Access Memory的缩写。这个词的由来是因为早期的计算机曾经使用磁鼓作为内存,而磁鼓和磁带都是典型的顺序读写设备。RAM则可以随机读写。

2023-03-30 14:53:27 3867

3867 本文将介绍低功耗系统在降低功耗的同时保持精度所涉及的时序因素和解决方案,以满足测量和监控应用的要求。

2023-07-11 16:16:26 1367

1367

统计有效数据包的个数。 假设数据中存在pkt_id,pkt_id为0~63,则ram的深度为64。pkt_id用于作为读写地址。RAM读延时为3个时钟周期。

2023-11-17 17:36:16 1207

1207

电子发烧友网站提供《GD32F47x/F42x的设备限制及解决方案勘误手册.pdf》资料免费下载

2023-12-14 09:50:43 0

0 电子发烧友网站提供《GD32F30x的设备限制及解决方案介绍.pdf》资料免费下载

2023-12-14 09:44:12 1

1 电子发烧友网站提供《GD32F45x/F40x的设备限制及解决方案介绍.pdf》资料免费下载

2023-12-14 09:45:45 0

0 电子发烧友网站提供《GD32F3x0的设备限制及解决方案介绍.pdf》资料免费下载

2023-12-14 09:47:44 0

0 电子发烧友网站提供《GD32E50x系列器件的限制及解决方案勘误手册.pdf》资料免费下载

2023-12-14 09:49:18 0

0 ram也叫主存,是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外)且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。

2024-01-09 11:11:57 5576

5576

电子发烧友网站提供《GD32A503系列器件的限制及解决方案介绍.pdf》资料免费下载

2024-01-26 10:21:03 0

0 电子发烧友网站提供《GD32A513系列器件的限制及解决方案介绍.pdf》资料免费下载

2024-01-26 10:19:45 0

0 FPGA双口RAM的使用主要涉及配置和使用双端口RAM模块。双端口RAM的特点是有两组独立的端口,可以对同一存储块进行读写操作,从而实现并行访问。

2024-03-15 13:58:14 2074

2074 随着设计要求越来越复杂、产品种类越来越繁多,精密时序器件解决方案的应用需求也随之增加。时序器件是众多设计中不可或缺的一部分,客户因此需要可靠且长期的供货支持。

2024-04-16 10:31:21 661

661 在计算机系统中,存储器是不可或缺的组成部分,它负责存储程序和数据以供处理器使用。其中,只读存储器(ROM)和随机读写存储器(RAM)是两种常见的存储器类型,它们在计算机系统中各自扮演着重要的角色。本文将详细探讨ROM和RAM之间的区别,包括它们的工作原理、存储特性、数据读写特性以及用途等方面。

2024-05-12 17:04:00 8283

8283 可擦可编程只读存储器)是两种不同类型的存储器,它们各自具有独特的特点。 RAM的特点 随机访问能力 :RAM具有随机访问的能力,意味着它可以直接访问任何存储单元,而不需要按照顺序进行读写操作。这使得RAM的访问

2024-09-18 11:11:53 2652

2652 电子发烧友网站提供《双电源电压DSP的电源时序控制解决方案.pdf》资料免费下载

2024-10-11 11:33:41 1

1

电子发烧友App

电子发烧友App

评论