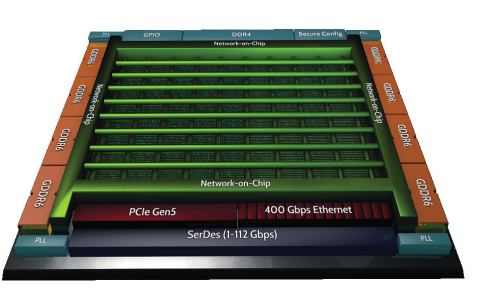

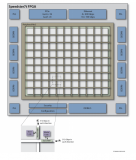

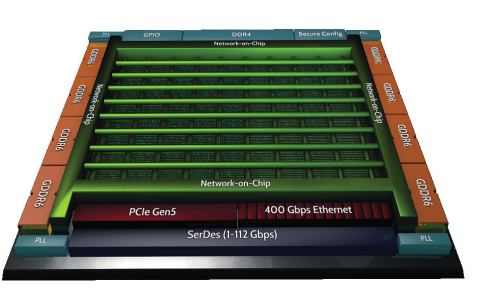

Achronix 最新基于台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器件包含了革命性的新型二维片上网络(2D NoC)。

2020-02-27 17:08:41 1774

1774 Achronix 在其最新基于台积电(TSMC)7nm FinFET工艺的Speedster7t FPGA器件中包含了革命性的创新型二维片上网络(2D NoC)。

2020-08-21 14:44:57 696

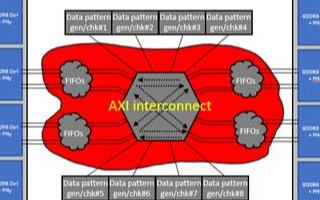

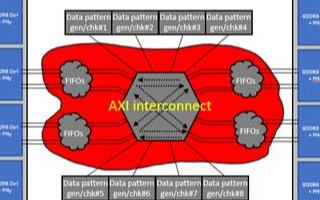

696 对于AXI interconnect模块,我们采用Github上开源的AXI4总线连接器来实现,这个AXI4总线连接器将4个AXI4总线主设备连接到8个AXI4总线从设备,源代码可以在参考文献

2020-09-03 12:39:38 797

797

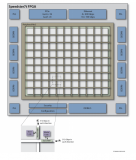

Speedster7t架构中的2D NoC提供了从逻辑阵列的可编程逻辑到位于I/O环中的高速接口子系统的高带宽连接,用于连接到片外资源。

2021-07-07 16:31:31 1863

1863

创新的二维片上网络(2D NoC)来处理这些高带宽数据流。Achronix的FPGA中特有的2D NoC实现是一种创新,它与用可编程逻辑资源来实现2D NoC的传统方法相比,有哪些创新和价值呢?本白皮书讨论了这两种实现2D NoC的方法,并提供了一个示例设计,以展示与软2D NoC实现相比,

2022-04-21 18:02:56 5750

5750

只有在脑海中建立了一个个逻辑模型,理解FPGA内部逻辑结构实现的基础,才能明白为什么写Verilog和写C整体思路是不一样的,才能理解顺序执行语言和并行执行语言的设计方法上的差异。在看到一段简单程序的时候应该想到是什么样的功能电路。

2022-08-25 11:12:00 739

739 2D NoC如同在FPGA可编程逻辑结构上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽。

2021-11-11 14:20:14 2760

2760

背光区域调节技术2D区域调光的优点2D区域调光面临的难题及机遇

2021-02-26 08:21:12

描述2D 执行器在 X/Y 2D 空间中移动微型机器人有区别:- 我正在使用另一个移动轨道配置- 控制是三相单极对四相双极- 我的机械手 (mBot) 使用 4 个磁铁并且不悬浮- 对于一维移动,我

2022-07-25 06:33:03

/DNN2016.srcs/sim_1/new/test1_tb.sv:37]警告:[VRFC 10-278]实际位长32与端口a的正式位长8不同[3]这是否意味着我不能将2D阵列作为模块I / O?这是SystemVerilog支持的功能,我认为Vivado支持SystemVerilog。

2020-05-22 07:00:12

FPGA 内部详细架构FPGA 芯片整体架构1.可编程输入输出单元(IOB)(Input Output Block)2.可配置逻辑块(CLB)(Configurable Logic Block)3.

2021-07-30 08:10:06

FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种特殊的集成电路,其内部结构由大量的可配置逻辑块和互连线组成。FPGA可以通过编程来实现各种数字系统功能

2024-01-26 10:03:55

用CPLD实现。 (2)数据密集型,需要大量的数据处理能力,但逻辑相对简单,对输入要求少,适合FPGA实现。7、配置不同 CPLD:采用EPROM,E2PROM工艺,直接写入,保密性好。 FPGA:采用SRAM工艺,故需外加ROM芯片,用于存储配置信息。其保密性较差。可实现动态重构。高端FPGA具备加密功能

2020-08-28 15:41:47

的相互连接。实际情况还真不是这么简单,FPGA/CPLD里面其实也找不着多少个与门、或门、非门。那么FPGA/CPLD器件内部到底以怎样的方式来实现我们需要的逻辑电路呢?下面我们就通过剖析MAX II

2015-01-27 11:43:10

。(特权同学版权所有)我们都知道,硬件有着与生俱来的并行特点,它不同于软件编程的顺序特性。在FPGA器件内部,所有的硬件逻辑都可以同时工作运行,正是这样,很多需要多条软件程序指令实现的功能,用硬件逻辑

2015-03-26 11:00:19

NoC是什么?NoC有哪些技术优势?NoC有哪些关键技术难点?

2021-06-04 06:34:33

NoC在高端FPGA的应用是什么?NoC给Speedster 7t FPGA带来的优势有哪些?

2021-06-17 11:12:26

fpga通过什么实现逻辑功能,以超级马里奥为例子讲述FPGA有些制作。1、FPGA游戏目标没有CPU,单纯用 FPGA 的verilog硬件语言来实现一个游戏,而这个游戏还得符合老师要求,由于没有

2021-07-22 07:07:25

在超高速数据采集方面,FPGA(现场可编程门阵列)有着单片机和DSP所无法比拟的优势。FPGA时钟频率高,内部时延小,目前器件的最高工作频率可达300MHz;硬件资源丰富,单片集成的可用门数达1000万门;全部控制逻辑由硬件资源完成,速度快,效率高;组成形式灵活,可以集成外围控制、译码和接口电路。

2019-08-02 06:51:33

Ansys Maxwell 3D 2D RMxprt v16.0 Win32-U\RMxprt 软件可提高旋转电机的设计和优化速度。用户通过软件可以很简单地利用电机参数及模板驱动型用户界面对电机建模

2014-06-13 17:09:22

用户根据需要生成特定的电路结构,完成一定的功能。由于 CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测的缺点。到90年代

2009-09-29 09:38:32

最新教程下载:本章教程为大家讲解LTDC应用中最基本的汉字显示和2D图形显示功能实现。 初学者重要提示 LCD相关的基础支持 LCD硬件设计 LCD驱动设计 LCD板级支持包(和) LCD的驱动移植

2021-12-13 07:29:15

第41章 STM32F429的LTDC应用之LCD汉字显示和2D图形显示本章教程为大家讲解LTDC应用中最基本的汉字显示和2D图形显示功能实现。目录第41章 STM32F429的LTDC应用之LCD

2021-08-10 07:24:07

PADS 2D网格这个怎么做急!!!

2016-10-06 20:03:34

第51章 STM32H7的LTDC应用之LCD汉字显示和2D图形显示本章教程为大家讲解LTDC应用中最基本的汉字显示和2D图形显示功能实现。51.1 初学者重要提示51.2 LCD相关的基础支持51.3 LCD硬件设计51.4 ...

2021-08-03 06:40:36

`上个月拿到了STM32+LT768的开发板+LCD显示屏,学会了用stm32驱动lt768实现2d图形加速和硬件图形加速,用来显示图形或者图片很方便,推荐给大家。下面放上LT768的一些特色功能

2018-04-02 00:09:17

或2 个)相同的Slice 和附加逻辑构成,每个CLB 模块不仅可以用于实现组合逻辑、时序逻辑,还可以配置为分布式RAM 和分布式ROM。3. 数字时钟管理模块(DCM)业内大多数 FPGA 均提供

2012-03-08 11:03:49

连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能

2019-08-11 04:30:00

各位大家好!我想知道两个1D数组是如何放入2D数组中的。我希望最后有一个数组有两列。我已经得到了9.0感谢你的帮助。 以上来自于谷歌翻译 以下为原文Hi everybody!i would

2019-03-13 15:59:52

AD17.1.5软件,3D与2D模型不能相互转换,按3可以进入3D模型,按2不可以进入2D模型,这个是怎么回事啊?

2019-09-20 05:35:16

互连 等。1)自由空间光互连技术通过在自由空间中传播的光束进行数据传输,适用于芯片之间或电路板之间这个层次上的连接,可以使互连密度接近光的衍射极限,不存在信道对带宽的限制,易于实现重构互连。该项技术

2016-01-29 09:17:10

器件中的重要创新之一,2D NoC 为 FPGA 设计提供了几项重要优势,包括:· 提高设计的性能,让 FPGA 内部的数据传输不再成为瓶颈。· 节省 FPGA 可编程逻辑资源,简化逻辑设计,由

2020-09-07 15:25:33

你好,我正在使用带有AD6676-EBZ高速adc的定制FPGA平台。该逻辑包含JESD24B IP。我想将VIO范围用于眼图。但我真的不明白它是如何运作的。我发现2D眼睛扫描逻辑提供了通过axi4

2020-07-30 10:24:35

基于FPGA的超高速FFT硬件实现介绍了频域抽取基二快速傅里叶运算的基本原理;讨论了基于FPGA达4 096点的大点数超高速FFT硬件系统设计与实现方法,当多组大点数进行FFT运算时,利用FPGA

2009-06-14 00:19:55

机载视频图形显示系统主要实现2D图形的绘制,构成各种飞行参数画面,同时叠加实时的外景视频。由于FPGA具有强大逻辑资源、丰富IP核等优点,基于FPGA的嵌入式系统架构是机载视频图形显示系统理想的架构

2019-06-24 06:07:53

vrfSubject:[vrf] Array2D二维数组问题:1。如何在声明后使用设置变量初始化它?.2。如何将2D数组馈送到记录?3。如何从Record和DataSet中提取相同的2D数组?提前谢谢

2019-10-29 12:41:09

逻辑结构之上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了大约高达27Tbps的超高带宽。作为Speedster7t FPGA器件中的重要创新之一,2D NoC为FPGA

2020-10-20 09:54:00

NoC为FPGA设计提供了哪些优势?NoC在FPGA内部逻辑互连中发挥的作用是什么?如何利用片上高速网络创新地实现FPGA内部超高带宽逻辑互连?

2021-06-17 11:35:28

前言FPGA 可以实现高速硬件电路,如各种时钟,PWM,高速接口,DSP计算等硬件功能。这是Cortex-M 处理器软件无法比拟的。要实现FPGA 的逻辑设计,对于嵌入式系统工程师又是比较复杂和具有

2021-12-21 06:13:49

如何同时获取2d图像序列和相应的3d点云?以上来自于谷歌翻译以下为原文How to obtain the sequence of 2d image and corresponding 3d point cloud at the same time?

2018-11-13 11:25:01

请问PCB 中2D 库中怎么导出3D

2019-09-11 22:17:15

如何在MA35D1上使用硬件 2D 加速功能?

2023-09-06 08:26:00

推动FPGA调试技术改变的原因是什么外部逻辑分析仪受到的限制是什么如何用内部逻辑分析仪调试FPGA

2021-04-30 06:44:08

本文档的主要内容详细介绍的是小米的2D激光雷达拆解图和讲解。

2023-09-22 08:07:45

ucgui中怎么跟新对话框里面2D图形的啊 我用2D图形画了一个温度计,怎么更新呢?

2019-08-21 03:18:09

嗨,我知道当我们将一个数组传递给函数时,只有数组的基本地址(指针左右)被传递,现在我的问题是如何传递一个2D数组并返回相同的值:例如,考虑这个代码片段:现在这个函数对4*4矩阵做了一些改变,并返回

2019-09-06 17:07:48

嗨,我知道当我们将一个数组传递给函数时,只有数组的基本地址(指针左右)被传递,现在我的问题是如何传递一个2D数组并返回相同的值:例如,考虑这个代码片段:现在这个函数对4*4矩阵做了一些改变,并返回

2019-10-09 14:17:30

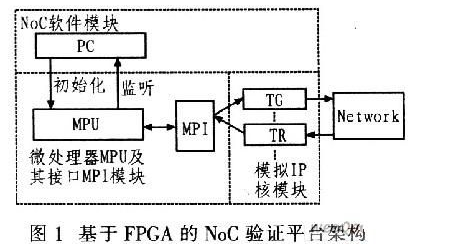

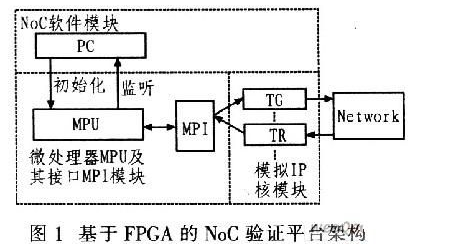

本文提出了一种基于FPGA的NoC验证平台。详细讨论了该验证平台中FPGA硬件平台和NoC软件的基本功能,并阐述了TG/R,MPU,MPI以及NoC软件的可重用性等特点。通过一个实例仿真验证的结果说明了该验证平台的基本功能和优越性。

2021-05-06 07:20:48

)或逻辑块、互连和 i/o 线。图2: 显示 FPGA 结构的图形图像CLB 可以称为 FPGA 的基本构建块。它基本上是一个逻辑单元,可以配置或编程来执行所需的功能。它们被连接到互连块。CLB 可以

2022-04-03 11:20:18

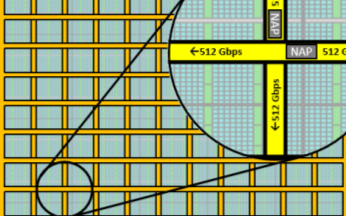

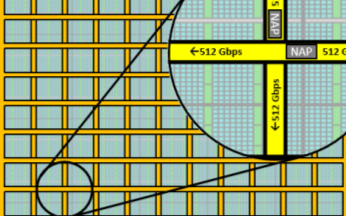

288bit的原始数据模式(Raw data mode)。 用户可以通过这288bit的信号进行逻辑直连或者自定义协议互连。图3利用2D NoC进行内部逻辑互连在NoC的每个交叉点上都有两个网络接入点

2020-05-12 08:00:00

的读写效率最后,我们测试一下7t1500上GDDR6控制器的读写效率,所有的测试结果基于仿真数据。因为7t1500包含了片上网络(NoC),并且NoC已经实现了仲裁,时钟域转换的逻辑,我们用三个用户逻辑

2021-12-22 08:00:00

请问这样的2D数组怎么创建代表什么意思

2019-09-02 15:51:55

,如果大家想在对话框上面绘制2D图形的话,可以将STemWin的2D绘制函数放在对话框回调函数中的WM_PAINT消息中实现。 这里跟大家讲一下如何利用uCGUIBulder4.0在对话框上面绘制简单的横线和竖线。60.1.1 第一步:建立如下界面

2016-10-18 11:33:49

在Speedster7t FPGA中增加NoC能带来哪些好处?

2021-06-17 10:50:10

各位大大,请问在rk3288板子上如何启动2D显示硬加速!

2022-07-07 11:36:28

请问怎么将AD中的3D封装库转换为2D的封装库

2019-06-05 00:35:07

调试FPGA时,TD软件是否支持内部逻辑分析(抓波形)功能?

2023-08-11 10:32:27

手势功能并与2D PCAP多点触摸设计实现无缝结合而言,GestIC技术可谓是一款复杂性极低的解决方案。利用这一方案,设计人员现在可以轻松地结合2D和3D用户界面技术来建立易用的创新应用。” 2D/3D触摸与手势开发工具包(DV102014)现已开始供应。

2018-11-07 10:45:56

《Fundamentals of Computer Graphics》翻译(三):隐式2D直线

2019-09-03 12:19:29

Xilinx®7系列FPGA由四个FPGA系列组成,可满足各种系统要求,从低成本、小尺寸、成本敏感的高容量应用到超高端连接带宽、逻辑容量和信号处理能力,以满足最苛刻的高性能应用

2022-08-30 17:04:09

介绍了频域抽取基二快速傅里叶运算的基本原理;讨论了基于FPGA达4 096点的大点数超高速FFT硬件系统设计与实现方法,当多组大点数进行FFT运算时,利用FPGA内部大容量存储资源,采

2009-04-26 18:33:08 26

26 技术相结合,可以实现2.5D和3D的复合测量。 CHT/CHS/CHX系列2d光学影像测量仪功能强大,可实现各种复杂零件的表面尺寸、轮廓、角

2022-09-08 11:27:18

Xilinx®7系列FPGA包括四个FPGA系列,可满足整个系统要求,包括低成本,小尺寸,成本敏感的大批量应用程序,可满足最苛刻的超高端连接带宽,逻辑容量和信号处理能力高性能的应用程序。7系列

2022-11-10 15:11:11

片上网络(Network-on-Chip, NoC)以网络互连结构代替传统总线结构,很好地解决了片上高性能计算资源之间的通信瓶颈问题。路由器是实现NoC 的重要基础部件,本文在分析国内外相关

2009-12-14 09:37:38 34

34 比较了多种DSP芯片的互连性能,给出了一种简单高性能DSP网络结构。针对构成DSP网络通讯接口的链路口,分析其基本特点,并且提出了在FPGA中实现的设计原理。最后给出了设计仿真图和

2010-07-27 16:46:46 22

22 随着FPGA设计复杂度的增加,传统测试方法受到限制。在高速集成FPGA测试中,其内部信号的实时获取和分析比较困难。介绍了Quartus II中SingalTap II嵌入式逻辑分析器的使用,并给出一个

2010-12-17 15:25:17 16

16 针对基于软件仿真片上网络NoC(Network on Chip)效率低的问题,提出基于FPGA的NoC验证平台构建方案。该平台集成可重用的流量产生器TG(Traffic Generation),流量接收器TR(Traffic Receiver)

2011-01-04 16:24:38 12

12 为了能够灵活地验证和实现自主设计的基于NoC的多核处理器,缩短NoC多核处理器的设计周期,提出了设计集成4片Virtex-6—550T FPGA的NoC多核处理器原型芯片设计/验证平台。分析和评估

2017-11-22 09:15:01 4137

4137 本文提出的基于FPGA的NoC验证平台在仿真速度方面是一般基于HDL的软件仿真的16 000倍,而基于PC机编写的NoC软件更增强了该平台的灵活性和实用性。

2019-04-13 11:33:47 2053

2053

了革命性的新型二维片上网络(2D NoC)。2D NoC如同在FPGA可编程逻辑结构上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽(~27Tbps

2020-03-04 15:59:39 1517

1517 Achronix 最新基于台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器件包含了革命性的新型二维片上网络(2D NoC)。

2020-05-28 10:27:12 527

527

可编程逻辑结构上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽。 2. 2D NoC给Speedster 7t FPGA带来的优势 日益增长的数据加速需求对硬件平台

2021-11-12 09:21:22 1777

1777

片上网络(2D NoC)来处理这些高带宽数据流。Achronix的FPGA中特有的2D NoC实现是一种创新,它与用可编程逻辑资源来实现2D NoC的传统方法相比,有哪些创新和价值呢?本白皮书讨论

2022-04-21 09:27:35 1044

1044 逻辑单元(Logic Element,LE)在FPGA器件内部,用于完成用户逻辑的最小单元。一个逻辑阵列包含16个逻辑单元以及一些其他资源, 在一个逻辑阵列内部的16个逻辑单元有更为紧密的联系,可以实现特有的功能。

2022-06-15 16:50:21 2604

2604 Achronix Speedster7t FPGA除了在外围Hard IP上都采用目前业内领先的大带宽高速率IP,在内部的可编程逻辑的架构中也做了大量的优化去进一步提高内部可编程逻辑的性能,从而适配

2022-07-05 15:37:41 924

924 成本、小尺寸、成本敏感的高容量应用到超高端连接带宽、逻辑容量和信号处理能力,以满足最苛刻的高性能应用,以及其它系列运用不同领域。

2022-11-03 14:39:54 1446

1446 的数据传输带宽以及 存储器 带宽。但是在FPGA内部,可编程逻辑部分随着工艺提升而不断进步的同时,内外部数据交换性能的提升并没有那么明显,所以FPGA内部数据的交换越来越成为数据传输的瓶颈。 为了解决这一问题,Achronix 在其 基于台积电(TSMC)7nm FinFET工艺

2023-04-18 11:30:06 300

300 在芯片设计中,SoC(System on Chip)和NoC(Network on Chip)是两个不同的架构,它们在内部通信方式、设计理念方面存在着很大的差异。 SoC以紧凑的结构和低功耗著称

2023-05-11 10:39:17 6898

6898

NoC是相对于SoC的新一代片上互连技术,从计算机发展的历史可以看到NoC 必将是SoC 之后的下一代主流技术,SoC 通常指在单一芯片上实现的数字计算机系统,总线结构是该系统的主要特征,由于其可以

2023-07-13 15:57:08 556

556

NoC是相对于SoC的新一代片上互连技术,从计算机发展的历史可以看到NoC 必将是SoC 之后的下一代主流技术

2023-07-13 15:56:43 635

635

可以商用的集成全域硬2D NoC的FPGA器件,以每通道512Gbps的速率和超过2Tbps的总带宽来与所有系统接口和FPGA逻辑阵列互连。

2023-11-24 16:19:45 185

185 的FPGA内部信号引到引脚,然后用外部的逻辑分析仪捕获数据。然而当设计的复杂程度增加时,这个方法就不再适合了,其中有几个原因。第一是由于FPGA的功能增加了,而器件的引脚数目却缓慢地增长。因此,可用逻辑对I/O的比率减小了,参见图1。此外,设计很复杂时

2023-12-20 13:35:01 147

147

电子发烧友App

电子发烧友App

评论