现代集成电路芯片中,随着设计规模的不断扩大。一个系统中往往含有数个时钟。多时钟带来的一个问题就是,如何设计异步时钟之间的接口电路。异步 FIFO(First In First Out)是解决这个问题的一种简便、快捷的解决方案。##异步FIFO的VHDL语言实现

2014-05-28 10:56:41 3405

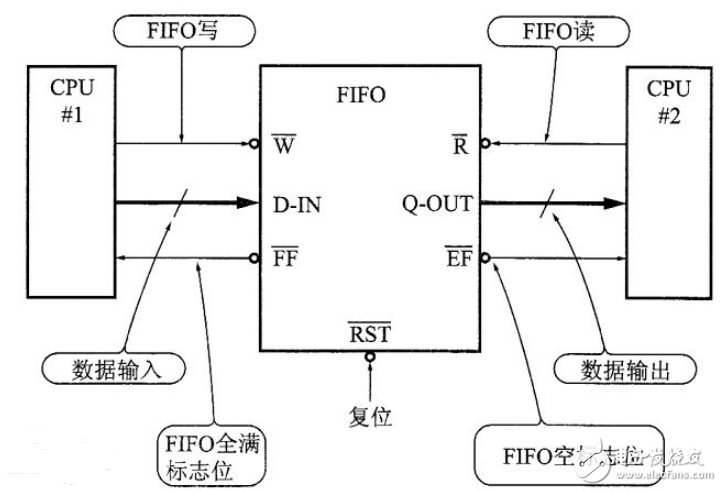

3405 存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。 用途1: 异步FIFO读写分别采用相互异步的不同时钟。在现代集

2018-06-21 11:15:25 6164

6164

是这个问题的一种简便、快捷的解决方案,使用异步 FIFO 可以在两个不同时钟系统之间快速而方便地传输实时数据。

2020-07-16 17:41:46 1050

1050

FIFO (先入先出, First In First Out )存储器,在 FPGA 和数字 IC 设计中非常常用。 根据接入的时钟信号,可以分为同步 FIFO 和异步 FIFO 。

2023-06-27 10:24:37 1199

1199

FIFO存储器是系统的缓冲环节,如果没有FIFO存储器,整个系统就不可能正常工作,它主要有几方面的功能:1)对连续的数据流进行缓存,防止在进机和存储操作时丢失数据;2)数据集中起来进行进栈和存储,可

2022-01-18 10:03:06

。音频处理器通常与软件或固件绑定,经设计执行某些回声消除或降噪功能。 FPGA器件使用基于栅级的架构,适用于并行模式下的信号处理。它还具有内部存储器、硬件乘法器和累加器,以及充足的I/O灵活性。某些

2016-12-07 16:05:03

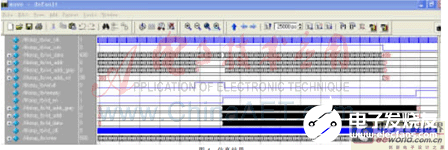

实例内部系统功能框图如图9.72所示。我们通过IP核例化一个异步FIFO,定时写入数据,然后再读出所有数据。通过QuartusII集成的在线逻辑分析仪SignalTap II,我们可以观察FPGA片内

2019-05-06 00:31:57

的所有内部数据的地址。简单的说,RAM是一种写地址,读数据的存储单元;CAM与RAM恰恰相反。 除了块RAM,Xilinx和Lattice的FPGA还可以灵活地将LUT配置成RAM、ROM、FIFO等

2016-08-23 10:33:54

的所有内部数据的地址。简单的说,RAM是一种写地址,读数据的存储单元;CAM与RAM恰恰相反。 除了块RAM,Xilinx和Lattice的FPGA还可以灵活地将LUT配置成RAM、ROM、FIFO等

2016-09-18 11:15:11

的所有内部数据的地址。简单的说,RAM是一种写地址,读数据的存储单元;CAM与RAM恰恰相反。 除了块RAM,Xilinx和Lattice的FPGA还可以灵活地将LUT配置成RAM、ROM、FIFO等

2016-10-08 14:43:50

应用,这种快乐试试你就会懂的。话不多说,上货。半导体存储器和可编程逻辑器件简介半导体存储器是一种能存储大量二值信息的半导体器件。在电子计算机以及其他一些数字系统的工作过程中,都需要对大量的数据进行存储

2023-02-23 15:24:55

涉及到温度采集,与微处理器通信,串口输出,控制数模转换芯片等多个组成部分。本文提出一种高效实用的FPGA 接口设计,它能够完成协调各个组成部分有序工作,准确、快速实现数据传输,严格控制信号时序等工作

2019-06-18 05:00:08

摘要:针对现有小型无人机导航系统的解算速度慢、多处理器核心臃肿可靠性差的缺点,实现了一种仅使用单一FPGA作为数据处理核心的小型高速导航解算系统。该系统对飞机运动方程组和导航方程组进行并行化分

2019-07-03 06:57:34

**第一至第三章**Q1. 若存储器的数据总线宽度为32位,存取周期为200ns,则存储器的带宽是多少?存储器的带宽指单位时间内从存储器进出信息的最大数量。存储器带宽 = 1/200ns ×32位

2021-07-28 06:23:01

ADSP-21160内部存储器block0和block1中必须分别存放程序和数据,还是说可以在某block中既放程序又放数据

2016-12-29 16:58:48

具体应用情况:5509A DSP 的CE1空间外接了一个异步存储器(FIFO),由DSP提供的异步读时钟 ARE 的频率是怎么控制的呢?是主频/(建立时间+选通时间+保持时间)吗?当然这三个时间可由

2015-01-13 20:33:46

取出、掉电丢失。在各类逻辑系统中运用非常广泛。在FPGA高级应用四的这个标题下,我们将会从内部存储器到外部存储器,介绍FIFO、ram、ddr几种常用的存储器设计。第一期我们介绍FIFOFIFO,全称是first in first out (先入先出存储队列) 。在程序中FIFO作为数据的队列通道,

2021-06-28 09:27:19

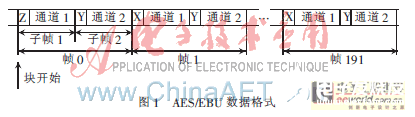

【作者】:赵宇红;曾雷;白皛;谢人超;阎利早;【来源】:《电声技术》2010年02期【摘要】:针对串行数字接口(SDI),提出了一种基于FPGA的音频数据IP模块解嵌方案。介绍了相关协议标准,重点

2010-04-22 11:54:44

概述该工程实例内部系统功能框图如图所示。我们通过IP核例化一个异步FIFO,这个FIFO的读写时钟频率不同,并且读写位宽也不同。定时对这个异步FIFO写入数据,然后再读出所有数据。通过ISE集成的在线

2016-03-07 11:32:16

一丶存储器的分类和层次半导体存储芯片:片选器:用来选取芯片有两种译码驱动方式:线选法:一维排列,结构简单,适合容量不大的存储芯片重合法:二维阵列,适合容量大为什么线选法不适合大的呢?我们以9组

2021-07-23 08:20:14

时序一 什么是FIFOFirst In First Out ,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其

2021-12-27 08:05:35

入的指令先完成并引退,跟着才执行第二条指令。 1.什么是FIFO? FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成

2022-02-16 06:55:41

FIFO是FPGA处理跨时钟和数据缓存的必要IP,可以这么说,只要是任意一个成熟的FPGA涉及,一定会涉及到FIFO。但是我在使用异步FIFO的时候,碰见几个大坑,这里总结如下,避免后来者入坑。

2021-02-04 06:23:41

内存储器可以在FPGA配置时自动初始化,相当于提供了一种非易失性的功能。片内存储器的最佳应用场合包括作为常见的缓存、点到点的缓存、查找表以及FIFO等。缓存,由于其具有低反应延时,片内存储器在微处理器中作为

2016-10-10 17:08:22

In First Out),即先入先出,这是一种典型的计算机数据或指令处理机制,和中国人所谓的“先来后到”理念有异曲同工之妙。而我们这里要说的FIFO存储器,和前面带有地址可直接定位操作的ROM或RAM存储器

2016-12-23 17:48:03

该工程实例内部系统功能框图如图9.72所示。我们通过IP核例化一个异步FIFO,定时写入数据,然后再读出所有数据。通过QuartusII集成的在线逻辑分析仪SignalTap II,我们可以观察

2018-08-28 09:39:16

强大的硬件支持。SOPC是Ahera公司提出的一种灵活、高效的片上系统(SOC)解决方案,它将处理器、存储器、I/O口等系统设计所需要的功能模块集成到一个可编程器件上,从而构成一个可编程的片上系统

2018-12-07 10:27:46

本文介绍一种基于虚拟存储器的USB下载线设计。

2021-05-27 06:07:33

作者:王烈洋 黄小虎 占连样 珠海欧比特控制工程股份有限公司随着电子技术的飞速发展, 存储器的种类日益繁多,每一种存储器都有其独有的操作时序,为了提高存储器芯片的测试效率,一种多功能存储器芯片

2019-07-26 06:53:39

如何利用Xilinx FPGA和存储器接口生成器简化存储器接口?

2021-05-06 07:23:59

本文介绍了一种0.13微米CMOS T艺下FPGA中嵌入式存储器模块的设计与实现。

2021-04-09 06:02:09

扩展存储器读写实验的目的是什么?怎样去设计一种扩展存储器读写的电路?扩展存储器读写实验的流程有哪些?

2021-07-14 07:04:49

通过对FPGA芯片内部EBRSRAM的深入研究,提出了一种利用格雷码对地址进行编码的异步FIFO设计方案。

2021-04-13 06:41:03

嗨, 我正在寻找具有内部存储器的CPLD。我想将程序存储在CPLD中,这样每次打开电源时,我都不必重新编程IC。有没有这样的CPLD?谢谢,阿文德古普塔。

2019-08-06 08:27:34

随着集成电路制造工艺水平的提高,半导体芯片上可以集成更多的功能,为了让产品有别于竞争对手的产品特性,在ASIC上集成存储器可以降低成本和功耗、改善性能、增加系统级芯片的可靠性。随着对嵌入式存储器需求的持续增长,其复杂性、密度和速度也日益增加,从而需要提出一种专用存储器设计方法。

2019-11-01 07:01:17

结合高速嵌入式数据采集系统,提出一种基于CvcloneⅢ FPGA实现的异步FIFO和锁相环(PLL)结构来实现高速缓存,该结构可成倍提高数据流通速率,增加数据采集系统的实时性。采用FPGA设计高速缓存,能针对外部硬件系统的改变,通过修改片内程序以应用于不同的硬件环境。

2021-04-30 06:19:52

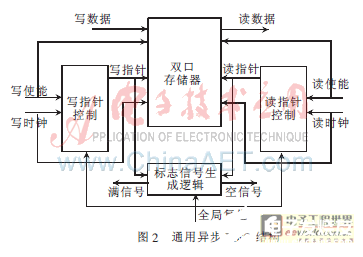

FIFO的基本结构和工作原理异步FIFO设计中的问题与解决办法FPGA内部软异步FIFO设计

2021-04-08 07:07:45

致性协议用于维护由于多个处理器共享数据引发的多处理器数据一致性问题。论述了一个适用于64位多核处理器的共享缓存设计,包括如何实现多处理器缓存一致性及其全定制后端实现。本文介绍了一种共享高速存储器模块

2021-02-23 07:12:38

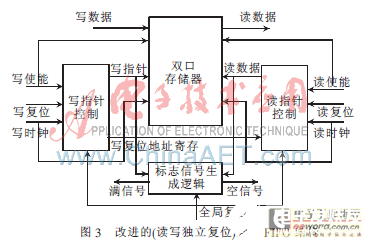

本32X8 FIFO的设计,采用了双体存储器的交替读写机制,使得在对其中一个存储器写操作的同时可以对另一个存储器进行读操作;对其中一个存储器读操作的同时可以对另一个存储器进行写操作。实现了高速数据缓冲,速度比单体存储器的FIFO提高了一倍。

2021-04-26 06:54:22

解码器需要一个恒速的传输流)。虽然存储器对同步的要求似乎很小,但当涉及到多个码流时它可能很显著。这种同步可以由一个异步FIFO实现。 2) 帧存储: 帧存储在这些地方需要:任何暂时的处理如帧率转换

2011-07-15 09:18:00

我有一个应用程序可能会更好用一个真正的,没有时钟的异步fifo,对于年轻人的说服力,这是一种想法,但不需要这个尺寸。http://www.ti.com/lit/ds/symlink

2019-04-23 13:44:46

你好,我当前正在运用ADI公司的AD9954芯片,我想用它自带的内部存储器来产生任意波形,可是搞了10天了还是没有任何的进展,在此希望能够得到ADI技术人员的帮助,或是给我们些有关内部存储器的程序

2018-11-26 10:07:00

打算用line-in或者mic-in录制一段10s音频,然后再播放,这10s音频临时存储在ddr存储器,需要怎么编程,不是很懂。

2019-06-17 06:08:10

怎么设计一种面向嵌入式存储器测试和修复的IIP?如何解决设计和制造过程各个阶段的良品率问题?嵌入式存储器测试和修复技术的未来趋势是什么?STAR存储器系统的功能是什么?

2021-04-15 06:05:51

为什么要设计一种异步FIFO?异步FIFO的设计原理是什么?怎样去设计一种异步FIFO?

2021-06-18 09:20:29

怎样去设计一种高效率音频功率放大器?如何对高效率音频功率放大器进行测试验证?

2021-06-02 06:11:23

检错与纠错的原理是什么?基于CPLD的容错存储器的设计实现

2021-05-07 06:02:42

网络存储器技术是如何产生的?怎样去设计一种网络存储器?

2021-05-26 07:00:22

座跨越沟壑的桥梁--一种非易失性的RAM。当一个电场被加到铁电晶体时,中心原子顺着电场的方向在晶体里移动。当原子移动时,它通过一个能量壁垒,从而引起电荷击穿。内部电路感应到电荷击穿并设置存储器。移去电场后

2011-11-19 11:53:09

座跨越沟壑的桥梁--一种非易失性的RAM。当一个电场被加到铁电晶体时,中心原子顺着电场的方向在晶体里移动。当原子移动时,它通过一个能量壁垒,从而引起电荷击穿。内部电路感应到电荷击穿并设置存储器。移去电场后

2011-11-21 10:49:57

首先介绍异步FIFO 的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法; 在传统设计的基础上提出一种新颖的电路结构并对其进行综合仿真和FPGA 实现。

2009-04-16 09:25:29 46

46 介绍了PCI 9054 接口芯片的性能及数据传输特点,提出了一种基于PCI 9054 外扩异步FIFO(先进先出)的FPGA(现场可编程门阵列)实现方法。由于PCI 9054 内部FIFO存储器主要用于数据

2010-01-06 15:20:10 44

44 本文主要研究了用FPGA 芯片内部的EBRSRAM 来实现异步FIFO 设计方案,重点阐述了异步FIFO 的标志信号——空/满状态的设计思路,并且用VHDL 语言实现,最后进行了仿真验证。

2010-01-13 17:11:58 40

40 介绍了异步FIFO在Camera Link接口中的应用,将Camera Link接口中的帧有效信号FVAL和行有效信号LVAL引入到异步FIFO的设计中。分析了FPGA中设计异步FIFO的难点,解决了异步FIFO设计中存在的两

2010-07-28 16:08:06 32

32 摘要:使用FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法,设计功能正确的FUFO会遇到很多问题,探讨了两种不同的异步FIFO的设计思路。两种思路

2006-03-24 12:58:33 680

680

摘要:首先介绍异步FIFO的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法;在传统设计的基础上提出一种新颖的电路结构并对其进行

2009-06-20 12:46:50 3667

3667

FPGA设计的高速FIFO电路技术

本文主要介绍高速FIFO电路在数据采集系统中的应用,相关电路主要有高速A/D转换器、FPGA、SDRAM存储器等。图1为本方案的结构框图。在大容量

2010-05-27 09:58:59 2226

2226

文中给出了异步FIFO的实现代码和FPGA与DSP的硬件连接电路。经验证,利用异步FIFO的方法,在FPGA与DSP通信中的应用,具有传输速度快、稳定可靠、实现方便的优点。

2011-12-12 14:28:22 51

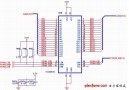

51 异步SRAM存储器接口电路设计(Altera FPGA开发板)如图所示:

2012-08-15 14:37:05 3862

3862

异步FIFO结构及FPGA设计,解决亚稳态的问题

2015-11-10 15:21:37 4

4 异步FIFO在FPGA与DSP通信中的运用

2016-05-19 11:17:11 0

0 基于异步FIFO在FPGA与DSP通信中的运用

2017-10-19 10:30:56 10

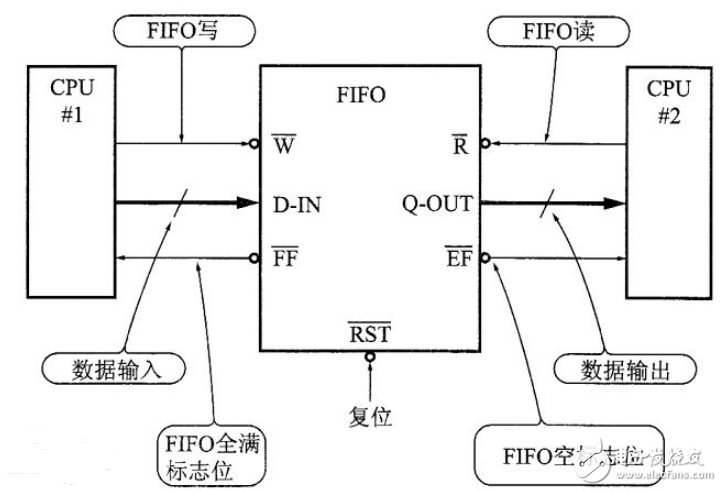

10 摘要 利用异步FIFO实现FPGA与DSP进行数据通信的方案。FPGA在写时钟的控制下将数据写入FIFO,再与DSP进行握手后,DSP通过EMIFA接口将数据读入。文中给出了异步FIFO的实现

2017-10-30 11:48:44 1

1 提出了一种基于FPGA实现的PCI-I2S音频系统方法。通过在FPGA中将PCI软核、FIFO以及设计的接口电路等相结合,在FPGA上实现了 PCI、I2C、I2S等多种总线,并且结合音频解码器实现

2017-11-17 08:17:52 2562

2562

在现代电路设计中,一个系统往往包含了多个时钟,如何在异步时钟间传递数据成为一个很重要的问题,而使用异步FIFO可以有效地解决这个问题。异步FIFO是一种在电子系统中得到广泛应用的器件,文中介绍了一种基于FPGA的异步FIFO设计方法。使用这种方法可以设计出高速、高可靠的异步FIFO。

2018-07-17 08:33:00 7873

7873

FIFO( First In First Out)简单说就是指先进先出。由于微电子技术的飞速发展,新一代FIFO芯片容量越来越大,体积越来越小,价格越来越便宜。作为一种新型大规模集成电路,FIFO芯片以其灵活、方便、高效的特性。

2017-12-06 14:29:31 10173

10173

问题一种简便、快捷的解决方案。使用异步FIFO可以在两个不同时钟系统之间快速而方便地传输实时数据。在网络接口、图像处理等方面,异步FIFO得到了广泛的应用。 异步FIFO是一种先进先出的电路,使用在需要产时数据接口的部分,用来存储、缓冲在两个异步时钟

2018-02-07 14:22:54 0

0 本文主要介绍了fifo存储器芯片型号有哪些?FIFO存储器是系统的缓冲环节,如果没有FIFO存储器,整个系统就不可能正常工作,它主要有几方面的功能:1)对连续的数据流进行缓存,防止在进机和存储操作

2018-04-08 16:11:32 23894

23894

异步FIFO(Fist-In-First-Out)是一种先入先出的数据缓冲器[1]。由于可以很好地解决跨时钟域问题和不同模块之间的速度匹配问题,而被广泛应用于全局异步局部同步[2](Globally

2018-06-19 15:34:00 2870

2870

介绍了TI公司TMS320C67系列DSP的EMIF(外部存储器接口)与异步FIFO(先进先出)存储器的硬件接口设计,着重描述了用EDMA(扩展的直接存储器访问)方式读取FIFO存储器数据的软件设计

2019-07-31 16:40:47 20

20 本文档的主要内容详细介绍的是FIFO存储器的尺寸图免费下载。

2019-08-15 08:00:00 2

2 问题的有效方法。异步FIFO是一种在电子系统中得到广泛应用的器件,多数情况下它都是以一个独立芯片的方式在系统中应用。本文介绍一种充分利用FPGA内部的RAM资源,在FPGA内部实现异步FIFO模块的设计方法。这种异步FIFO比外部 FIFO 芯片更能提高系统的稳定性。

2020-07-21 17:09:36 1326

1326

在FPGA开发板上都有几种不同的存储器,比如SDRAM,FLASH,EPCS,还有内部

2020-10-09 11:41:41 2921

2921 FIFO 是英文 First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加 1 完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

2020-12-22 13:11:00 1

1 提出了一种节能并可升级的异步FIFO的FPGA实现。此系统结构利用FPGA内自身的资源控制时钟的暂停与恢复,实现了高能效、高工作频率的数据传输。该系统在Xilinx的VC4VSX55芯片中实现,实际

2021-02-02 15:15:00 16

16 FIFO是FPGA处理跨时钟和数据缓存的必要IP,可以这么说,只要是任意一个成熟的FPGA涉及,一定会涉及到FIFO。但是我在使用异步FIFO的时候,碰见几个大坑,这里总结如下,避免后来者入坑。

2021-03-12 06:01:34 12

12 一:fifo是什么 FIFO的完整英文拼写为FirstIn First Out,即先进先出。FPGA或者ASIC中使用到的FIFO一般指的是对数据的存储具有先进先出特性的一个存储器,常被用于数据

2021-03-12 16:30:48 2796

2796

1.定义 FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序

2021-04-09 17:31:42 4697

4697

入的指令先完成并引退,跟着才执行第二条指令。 1.什么是FIFO? FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成

2021-12-17 18:29:31 10

10 异步fifo详解 一. 什么是异步FIFO FIFO即First in First out的英文简称,是一种先进先出的数据缓存器,与普通存储器的区别在于没有外部读写的地址线,缺点是只能顺序的读取

2022-12-12 14:17:41 2790

2790 FIFO(First In First Out )先入先出存储器,在FPG设计中常用于跨时钟域的处理,FIFO可简单分为同步FIFO和异步FIFO。

2023-04-25 15:55:28 2893

2893

FIFO是异步数据传输时常用的存储器,多bit数据异步传输时,无论是从快时钟域到慢时钟域,还是从慢时钟域到快时钟域,都可以使用FIFO处理。

2023-05-26 16:12:49 978

978

异步FIFO主要由五部分组成:写控制端、读控制端、FIFO Memory和两个时钟同步端

2023-05-26 16:17:20 911

911

异步FIFO包含"读"和"写“两个部分,写操作和读操作在不同的时钟域中执行,这意味着Write_Clk和Read_Clk的频率和相位可以完全独立。异步FIFO

2023-09-14 11:21:45 545

545

简单的一种,其特点是输入和输出都与时钟信号同步,当时钟到来时,数据总是处于稳定状态,因此容易实现数据的传输和存储。 而异步FIFO则是在波形的上升沿和下降沿上进行处理,在输入输出端口处分别增加输入和输出指针,用于管理数据的读写。异步FIFO的输入和输出可同时进行,中间可以

2023-10-18 15:23:58 790

790 请问异步FIFO的溢出操作时怎么样判断的? 异步FIFO是数据传输的一种常用方式,在一些储存器和计算机系统中,常常会用到异步FIFO。作为一种FIFO,异步FIFO经常面临两种情况:溢出

2023-10-18 15:28:41 299

299 1.1片上存储(on-chip ram) 在实际应用中任何场合都离不开数据,只要有数据的地方就有存储器,一般存储分为了2种,一种时可以读写,一种时只读

2023-11-17 14:00:02 179

179

电子发烧友App

电子发烧友App

评论