AnandTech报道称,Marvell刚刚发布了基于DSP(数字信号处理器)的112GSerDes解决方案。

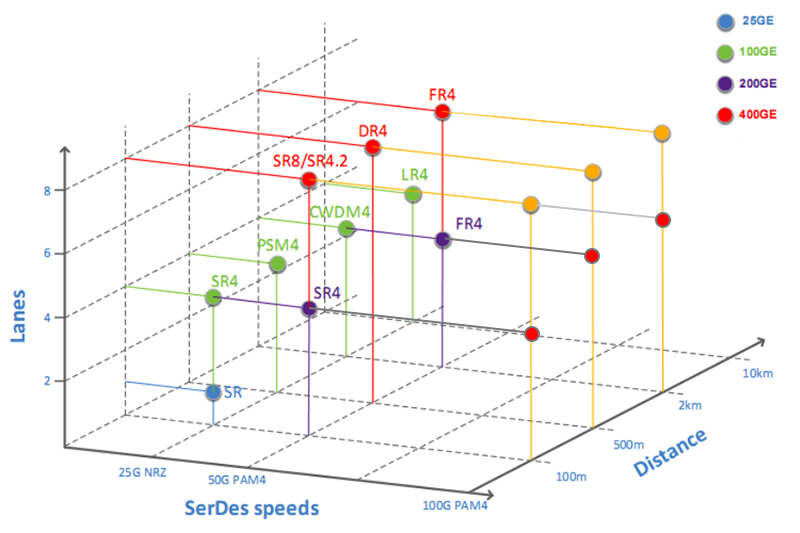

现代网络基础架构依赖于高速的SerDes连接,并且能够以各种速率和不同协议下工作(比如以太网、光纤、存储和连接结构)。

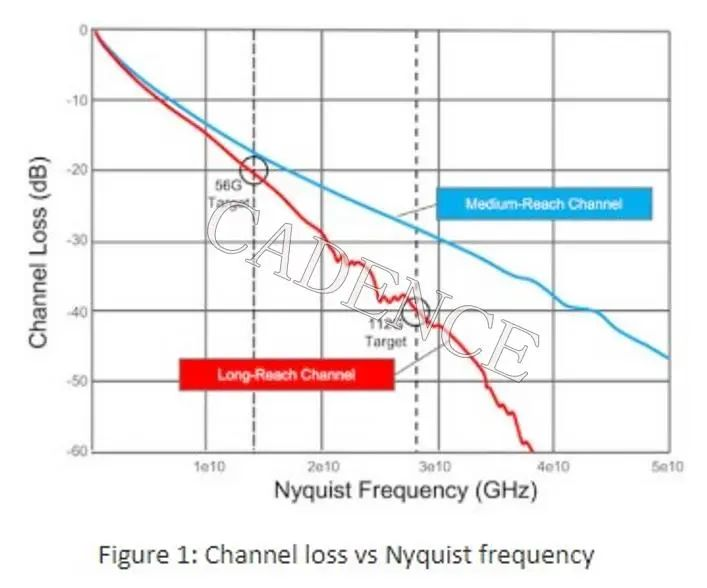

此前的产品已支持高达56G的连接,但最新IP已支持将它翻倍。尽管Marvell并不是第一家提供112G连接方案的厂商,但却是首个采用了5nm制程的企业。

与竞品相比,其不仅满足各种标准、还具有更低的能耗和错误率,对高速、高可靠性的基础架构应用有相当实际的意义。

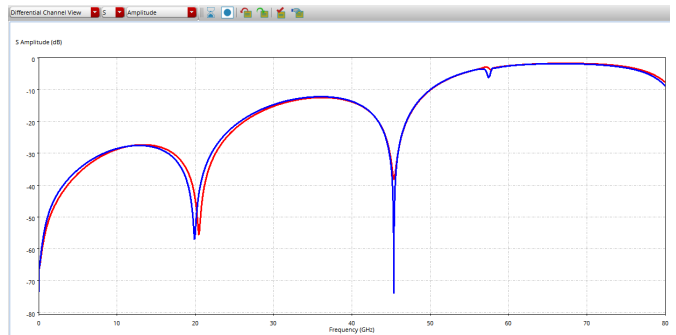

Marvell宣称,其新方案可显著降低每比特位传输的能耗,较基于台积电7nm工艺(N7)的竞品低了25%,并且具有严格的功率/热约束、以及大于40dB的插入损耗。

通常数据支持基于一系列0或1操作位的NRZ调制,但Marvell启用了2比特位的操作(00、01、10或11),又称PAM4脉冲幅度调制。这样可让带宽轻松翻倍,但也确实需要一些额外的电路。

作为一个面向未来的技术,一些人可能已经知道英伟达RTX3090就使用了基于7nm工艺的PAM4信号调制,可让美光GDDR6X闪存芯片提供超过1000GB/s的带宽。如有必要,还可以NRZ模式运行、以降低功耗。

Marvell表示,其已同多个市场的ASIC定制客户进行了部署112GSerDes方案的接洽,此外该公司还将支持一整套基于5nm的PHY、交换机、DPU、定制处理器、控制器、加速器等产品的方案。

责任编辑人:CC

-

dsp

+关注

关注

544文章

7682浏览量

344349 -

Marvell

+关注

关注

9文章

347浏览量

123081 -

SerDes

+关注

关注

6文章

178浏览量

34537

发布评论请先 登录

相关推荐

TE 112G 产品解决方案,助力“通关”高速互连挑战

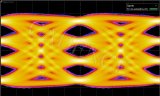

AMD硅芯片设计中112G PAM4串扰优化分析

Marvell推出两款新型OCTEON 10 DPU为网络设备带来服务器级别的性能

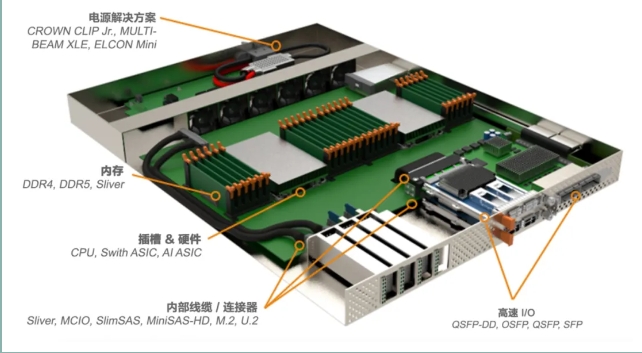

112G 高速I/O互连产品,为数字化转型加速

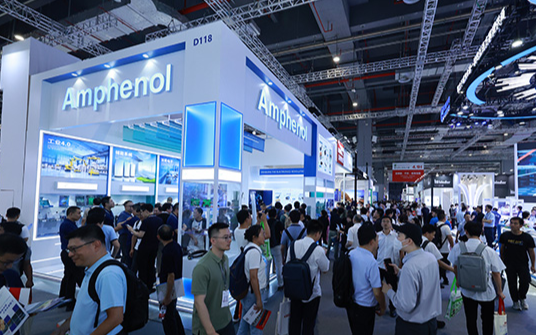

112G高速连接器又添重磅玩家 安费诺发布新品释放AI硬件算力效能

Amphenol安费诺焕新发布ExaMAX2® Gen2 解放AI硬件算力效能,引领112G风潮!

Cadence发布面向TSMC 3nm 工艺的 112G-ELR SerDes IP 展示

Marvell10g驱动程序缺少MODULE_INIT和MODULE_EXIT怎么解决?

Cadence 发布面向 TSMC 3nm 工艺的 112G-ELR SerDes IP 展示

Cadence发布面向TSMC 3nm工艺的112G-ELR SerDes IP展示

Marvell发布基于DSP的112G SerDes解决方案

Marvell发布基于DSP的112G SerDes解决方案

评论