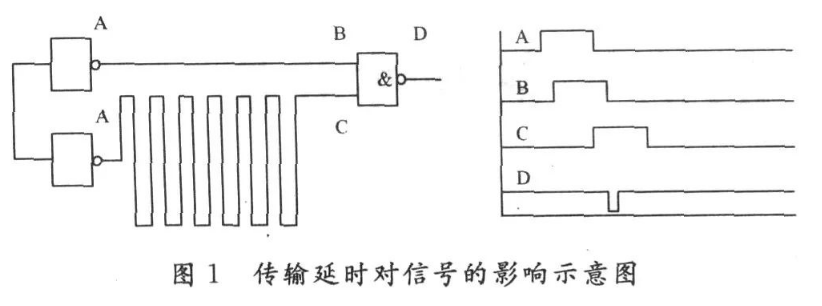

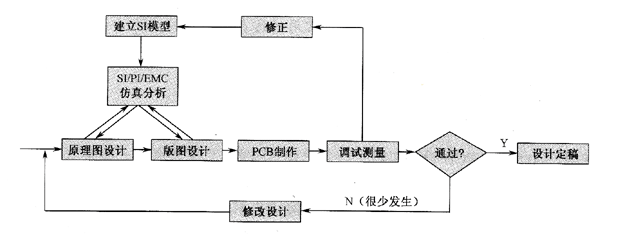

随着集成电路输出开关速度提高以及PCB板密度增加,信号完整性(Signal Integrity) 已经成为高速数字PCB设计必须关心的问题之一,元器件和PCB板的参数、元器件在PCB板上的布局、高速信号线的布线等因素,都会引起信号完整性的问题。

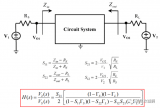

对于PCB布局来说,信号完整性需要提供不影响信号时序或电压的电路板布局,而对电路布线来说,信号完整性则要求提供端接元件、布局策略和布线信息。PCB上信号速度高、端接元件的布局不正确或高速信号的错误布线都会引起信号完整性问题,从而可能使系统输出不正确的数据、电路工作不正常甚至完全不工作。如何在PCB板的设计过程中充分考虑信号完整性的因素,并采取有效的控制措施,已经成为当今PCB设计业界中的一个热门话题。

信号完整性问题良好的信号完整性,是指信号在需要的时候能以正确的时序和电压电平数值做出响应。反之,当信号不能正常响应时,就出现了信号完整性问题。信号完整性问题能导致或直接带来信号失真、定时错误、不正确数据、地址和控制线以及系统误工作,甚至系统崩溃。PCB的信号完整性设计方法在PCB设计的实践过程中,人们不断积累了很多电路板的设计规则。在PCB设计时,认真参照这些设计规则,可以更好地达到PCB的信号完整性。

在设计PCB时,首先要了解整个电路板的设计信息,这主要包括:

1、器件数量、器件大小、器件封装,芯片的速率、PCB是否分为低速中速高速区、哪些是接口输入输出区;

2、整体布局的要求、器件布局位置、有无大功率器件、芯片器件散热的特殊要求;

3、信号线的种类速率及传送方向、信号线的阻抗控制要求、总线速率走向及驱动情况、关键信号及保护措施;

4、电源种类、地的种类、对电源和地的噪声容限要求、电源和地平面的设置及分割;

5、时钟线的种类和速率、时钟线的来源和去向、时钟延时要求、最长走线要求。

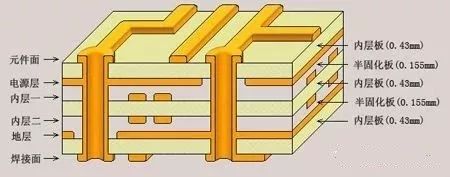

PCB的分层设计

了解电路板的基本信息后,要权衡电路板成本与信号完整性的设计要求,选择合理的布线层数。目前电路板已由单层、双层、四层板逐步向更多层电路板方向发展,多层PCB设计能提高信号走线的参考面,为信号提供回流路径,是达到良好信号完整性的主要措施。在进行PCB分层设计时,要遵循以下规则:

1、参考面应优选地平面。电源、地平面均能用作参考平面,且都具有一定的屏蔽作用。但相对而言,电源平面具有较高的特性阻抗,且与参考地电平之间存在较大的电位差,其屏蔽效果远低于地平面。

2、数字电路与模拟电路分层。在设计成本允许的情况下,最好把数字电路和模拟电路安排在不同的层上。如果必须要安排在同一个布线层上,则可以采用开沟、加接地线条、分割线等方法补救。模拟与数字的电源和地一定要分开,绝不能混用。

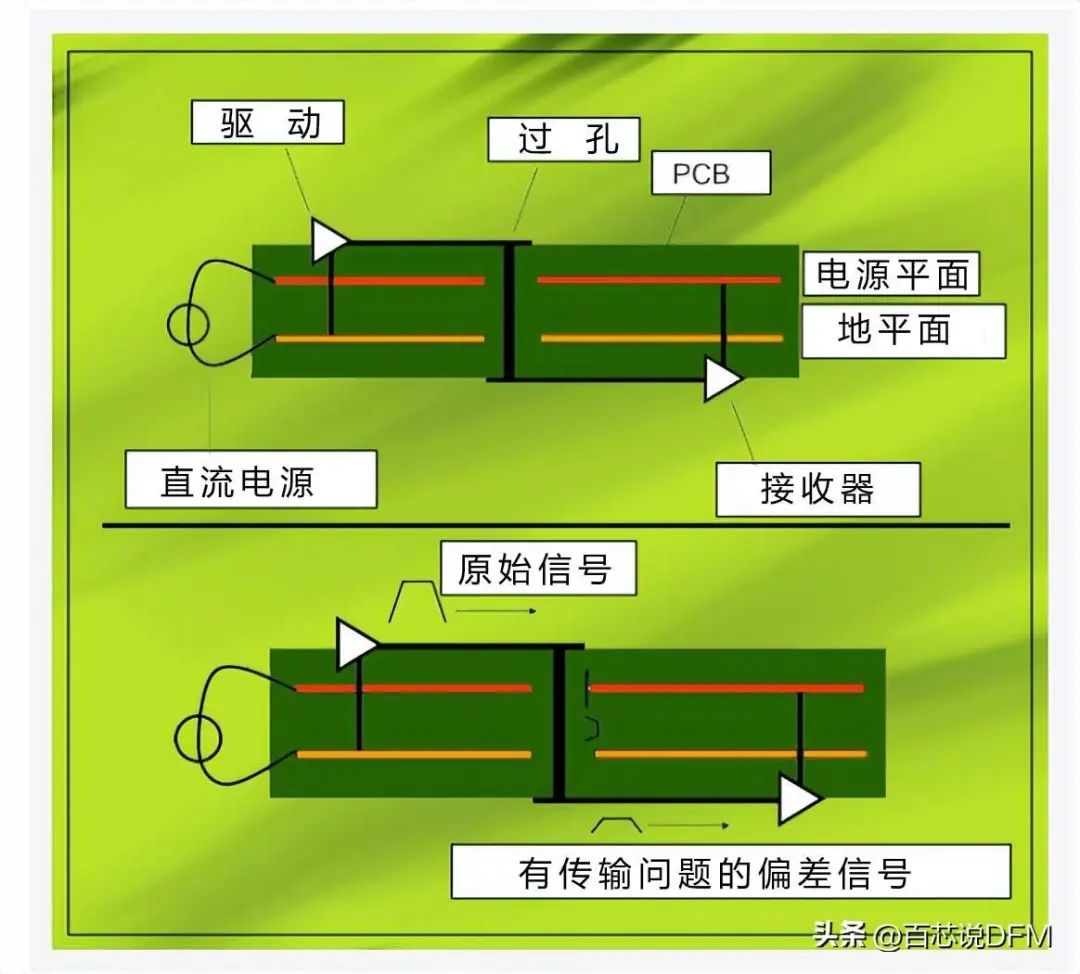

3、相邻层的关键信号走线不跨分割区。信号跨区将形成较大的信号环路产生很强的辐射。如果在地线分割的情况下,信号线必须要跨区,可以先在被分割的地之间进行单点连接,形成两个地之间的连接桥,然后通过该连接桥布线。

4、元件面下面要有相对完整的地平面。对多层板必须尽可能保持地平面的完整性,通常不允许有信号线在地平面内走线。

5、高频、高速、时钟等关键信号线都应有相邻的地平面。这样设计的信号线与地线间的距离仅为PCB层间的距离,因此实际的电流总在信号线正下方的地线流动,形成最小的信号环路面积,减小辐射。

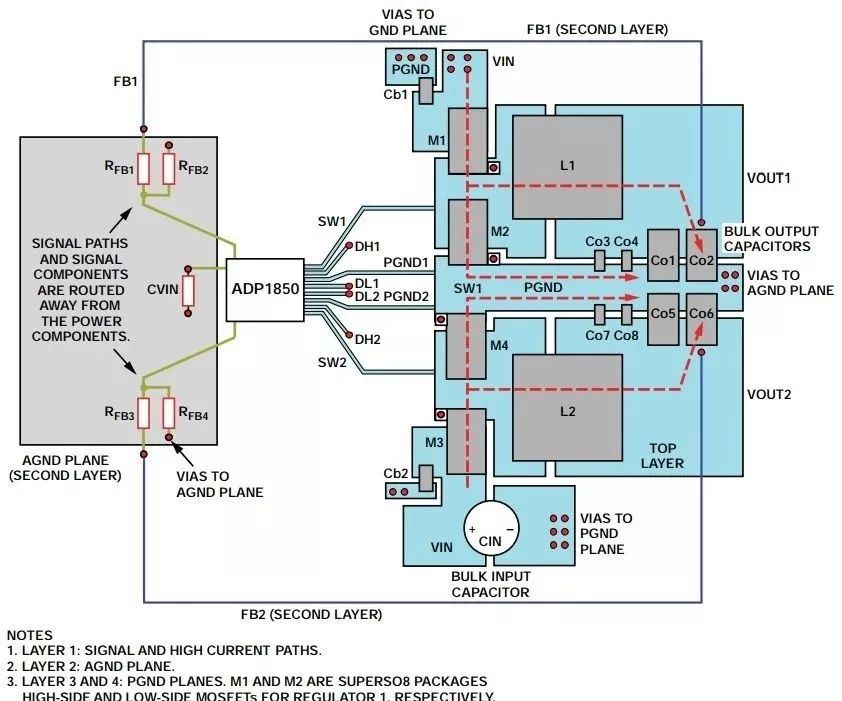

PCB的布局设计

印制板信号完整性设计的关键是布局和布线,其好坏直接关系到电路板的性能。在布局之前,必须确定尽量低的成本下满足功能的PCB大小。如果PCB尺寸过大,布局时器件分布分散,则传输线可能会很长,这样造成阻抗增加,抗噪声能力下降,成本也增加。如果器件集中放置,则散热不好,相邻的走线容易产生耦合串扰。所以必须根据电路功能单元进行布局,同时考虑到电磁兼容、散热和接口等因素。

在布局数字和模拟混合信号的PCB时,不能将数字和模拟信号混杂。如果模拟和数字信号必须混杂,要确保进行垂直走线以降低交互耦合的效应。电路板上的数字电路、模拟电路、以及易产生噪声的电路应予以分隔,并先对敏感线路进行布线,并消除电路间的耦合路径。尤其要考虑时钟、复位和中断线路,千万不要将这些线路与高电流开关线路平行,否则容易被电磁耦合信号破坏,引起非预期的复位或中断。进行整体布局时应遵循如下一些原则:

1、功能分区布局,PCB上模拟电路和数字电路应各自有不同的空间布局。

2、按照电路信号的流程来安排各功能电路单元,使信号流通保持方向一致。

3、以每个功能电路单元核心元件为中心,别的元件围绕它进行布局。

4、尽可能缩短高频元器件之间的连线,设法减小它们的分布参数。

5、易受干扰的元器件相互间不能太近,输入输出元件要远离。

PCB的布线设计

PCB布线时,要先对所有信号线进行分类。首先布时钟线,敏感信号线,再布高速信号线,在确保此类信号的过孔足够少,分布参数特性好以后,再布一般的不重要的信号线。

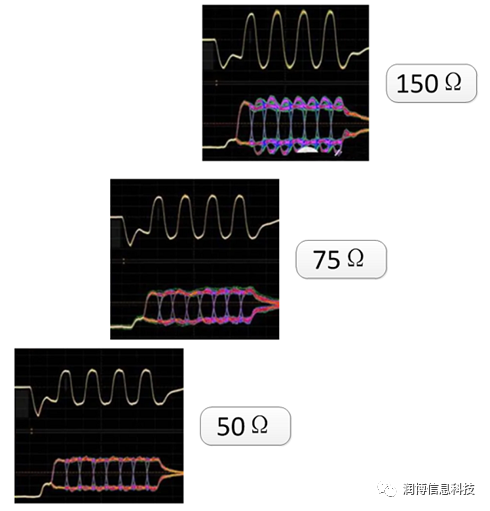

不相容的信号线应相互远离不要并行布线,如数字与模拟,高速与低速,大电流与小电流,高电压与低电压等。分布在不同层上的信号线应相互垂直地布线,这样可以减少线间的串扰。信号线的布置最好根据信号的流动方向顺序安排,一个电路的输出信号线不要再折回输入信号线区域。高速信号线要尽可能地短,以免干扰其他信号线。在双面板上,必要时可在高速信号线两侧加隔离地线。多层板上所有高速时钟线都应根据时钟线的长短,采用相应的屏蔽措施。

布线时应遵循的一般原则有:

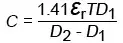

1、尽量选用低密度布线设计,并且信号走线尽量粗细一致,有利于阻抗匹配。对于射频电路,信号线的走向、宽度、线间距的不合理设计,可能造成信号传输线之间的交叉干扰。

2、尽量避免输入输出端的导线相邻以及长距离的并行布线。为了减少并行信号线的串扰,可增大信号线间的间距,或信号线间插入隔离带。

3、PCB上的走线宽度要均匀,不能发生线宽的突变。PCB走线拐弯处绝对不要采用90度的拐角,要采用圆弧或135度角,尽可能保持线路阻抗的连续性。

4、尽量减小电流环路的面积。载流电路对外的辐射强度与通过的电流、环路面积和信号频率的平方成正比,减小电流环路的面积可以减小PCB的电磁干扰。

5、尽量减少导线的长度,增加导线的宽度,有利于减少导线的阻抗。

6、对于开关控制信号,应尽量减少同时改变状态的信号PCB走线数量。

-

pcb

+关注

关注

4220文章

22472浏览量

385770

原文标题:PCB的信号完整性设计方法

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高速PCB设计,信号完整性问题你一定要清楚!

构建系统思维:信号完整性,看这一篇就够了!

要画好PCB,先学好信号完整性!

分析高速数字PCB设计信号完整性解决方法

什么是走线的拓扑架构?怎样调整走线的拓扑架构来提高信号的完整性?

信号完整性分析

pcb信号完整性详解

基于信号完整性分析的PCB设计方法

完整性设计PCB的信号该怎样做

完整性设计PCB的信号该怎样做

评论