资料介绍

描述

什么是仲裁员?

仲裁器是硬件设计中非常常用的块。

我想我可以在家里找到仲裁者的最好例子。当我的两个孩子十几岁时,我只有一辆车。在周五和周六晚上,通常会因为谁可以使用汽车而发生冲突。通常,由我来决定(仲裁者)谁得到了这辆车。这不是一件容易的事。(我仍然只有一辆车,正好我的孩子都不是十几岁了,赞美主,他们有自己的车)。

硬件板没有什么不同。至少在两种情况下,多个用户“需要”共享(且有价值且昂贵)的资源:

- 公共内存:在处理器和 FPGA 之间共享快速内存(即 DDR)的电路板是很常见的。显然,记忆不能同时回答两个高手。处理器和 FPGA 向仲裁器请求访问内存的权限。即使它以非常高的速度同时完成,对于我们的感知,实际上,FPGA 和处理器必须轮流拥有内存。注意:这只是一个简单的示例,因为还有许多其他应用程序甚至超过两个“智能”设备(处理器、DSP、GPU、FPGA、ASIC)轮流访问公共内存。

- 公共总线:很多时候多个主机(和从机)通过公共总线进行通信。从电气角度来说,总线非常简单。它只不过是一组铜连接或电线(有时带有总线驱动器)。但是总线所有权很重要,因为两个主机不可能同时拥有总线(多主机总线的示例:I2C、PCI)。如果两个主机试图同时“交谈”,就会发生冲突,总线上的数据就会被破坏。

仲裁者是硬件的一部分,它决定谁可以在任何给定时间使用公共的、有价值的资源。然而,与足球仲裁器不同的是,VHDL 仲裁器永远不会将其中一个设备从“游戏”中移除(好吧......几乎永远不会。在某些情况下,硬件仲裁器会决定一个设备表现不佳并决定将其从“游戏”中移除一个例子是可插拔卡访问公共总线,可以在关键时刻拔掉,如果仲裁器没有识别出故障,总线可能会卡在 - 现在丢失的 - 设备上)。

仲裁器从其客户端接收两种类型的信号:

- 请求:由想要拥有公共资源的每个设备声明。可以同时断言许多请求信号,就像许多设备请求拥有公共资源的许可一样。另一方面,可以只有一个,甚至没有断言的请求信号。后者是在特定时刻没有人需要共享资源的情况。

- Grant:由仲裁器断言,每个master有一个grant信号。通常,在任何给定时间都只会断言一个授权信号。

第一次实现 - 固定大小,固定优先级

我们将分析的第一个仲裁器具有三个请求输入和三个授权输出。它也有一个固定的主人优先权。master 编号越低,其优先级越高。该块也有忙信号。总线仲裁仅在其处于非活动状态时进行。如果总线已经被授权给代理,即使更高优先级的主机请求总线,当前事务也必须在仲裁器将总线授权给另一个主机之前完成。

生成授权信号的逻辑(在进程arbiter_pr上)非常简单。如果第一个主控(主控 0)断言请求,则它被授予授权。只有当主控 1 请求总线而主控 0 不请求总线时,它才会获得授权。只有当主控 2 请求总线并且主控 0 和主控 1 都没有请求总线时,它才会被授予授权。

gnt信号只有在总线不忙时才会改变。进程busy_pr和相关逻辑检测忙信号的下降沿。在 busy 变为低电平后,所有授权信号都被取消断言一个时钟,然后选择下一个总线主机的逻辑被激活。

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity arbiter is

port (

clk : in std_logic;

rst : in std_logic;

-- inputs

req : in std_logic_vector(2 downto 0);

busy : in std_logic;

-- outputs

gnt : out std_logic_vector(2 downto 0)

);

end arbiter;

architecture rtl of arbiter is

signal busy_d : std_logic := '0';

signal busy_fe : std_logic;

begin

busy_pr : process (clk)

begin

if (rising_edge(clk)) then

busy_d <= busy;

end if;

end process busy_pr;

-- Falling edge of busy signal

busy_fe <= '1' when busy = '0' and busy_d = '1' else '0';

arbiter_pr : process (clk, rst)

begin

if (rst = '1') then

gnt <= (others => '0');

elsif (rising_edge(clk)) then

if (busy_fe = '1') then

gnt <= (others => '0');

elsif (busy = '0') then

gnt(0) <= req(0);

gnt(1) <= req(1) and not req(0);

gnt(2) <= req(2) and not (req(0) or req(1));

end if;

end if;

end process arbiter_pr;

end rtl;

gnt信号只有在总线不忙时才会改变。进程busy_pr和相关逻辑检测忙信号的下降沿。在 busy 变为低电平后,所有授权信号都被取消断言一个时钟,然后选择下一个总线主机的逻辑被激活。

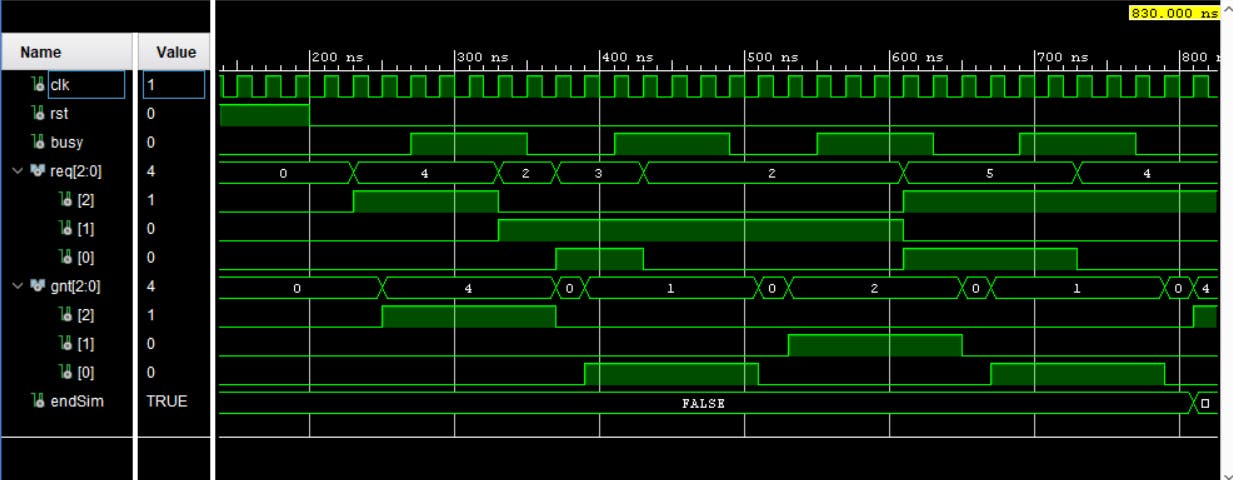

复位释放后,没有未完成的请求,因此仲裁器也不会断言任何授权信号。稍后在模拟中,多个主机请求仲裁器的许可(请求已断言)并根据其优先级获得授权。

在 300 到 400ns 之间,主机“1”断言其请求信号。两个时钟周期后,来自主机“0”的请求被置位。因此,即使 master '0' 稍后到达,当仲裁器可以自由分配总线时,它也会将其分配给 master '0'。

请注意,在gnt信号之间始终有一个“休息”时钟。每个主机使用总线四个时钟并放弃总线(这可以在忙信号的持续时间内看到)。

稍后,主机“2”和“0”都请求总线,正如预期的那样,总线被授予主机“0”。

GitHub 上提供了仲裁器“简单实现”、测试平台和 Modelsim 文件的 VHDL 源代码

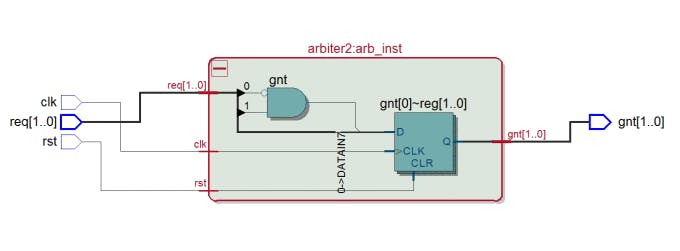

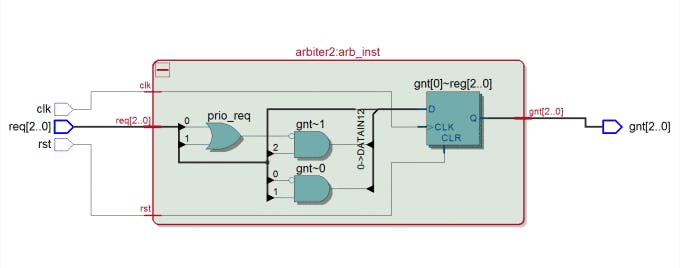

第二种实现——可变大小,固定优先级

上述仲裁器的逻辑是固定大小的。通过一些更改,并通过使用不受约束的端口(查看req和gnt端口),我们可以制作一个通用仲裁器,其大小可以在实现时决定。

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity arbiter_unc is

port (

clk : in std_logic;

rst : in std_logic;

-- inputs

req : in std_logic_vector;

busy : in std_logic;

-- outputs

gnt : out std_logic_vector

);

end arbiter_unc;

architecture rtl of arbiter_unc is

signal busy_d : std_logic;

signal busy_fe : std_logic;

begin

busy_pr : process (clk)

begin

if (rising_edge(clk)) then

busy_d <= busy;

end if;

end process busy_pr;

-- Falling edge of busy signal

busy_fe <= '1' when busy = '0' and busy_d = '1' else '0';

arbiter_pr : process (clk)

variable prio_req : std_logic;

begin

if (rising_edge(clk)) then

if (rst = '1') then

gnt <= (others => '0');

else

if (busy_fe = '1') then

gnt <= (others => '0');

elsif (busy = '0') then

gnt(0) <= req(0);

for I in 1 to req'left - 1 loop

prio_req := '0';

for J in 1 to I loop

prio_req := prio_req or req(J - 1);

end loop;

gnt(I) <= req(I) and not prio_req;

end loop;

end if;

end if;

end if;

end process arbiter_pr;

end rtl;

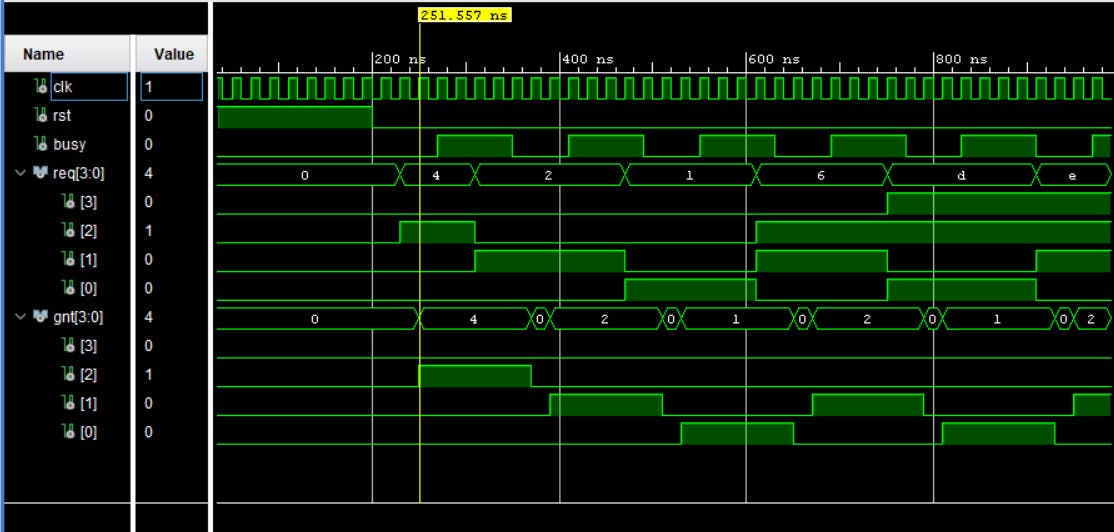

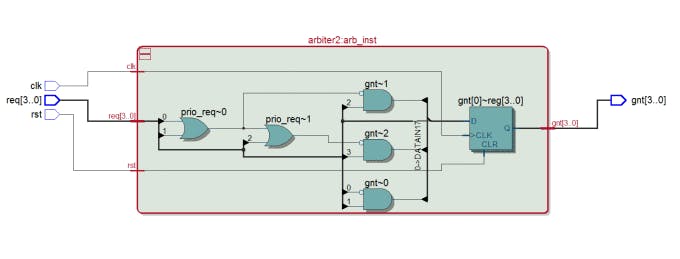

可变大小仲裁器的 Vivado 仿真,实例化为 size = 4

RTL 表示显示了处理越来越多的端口所需的组合复杂性不断增加,并且是使用 Quartus Prime 15.1 生成的。请注意,某些块(如输出 FF)不是单个而是堆叠的原始实例化。如前所述,如果多个主机请求总线,则编号最小的主机将获得gnt(回想一下,在任何给定时间只有一个主机应接收gnt)。这个仲裁器有一个固定的优先级。虽然在某些应用程序中可以使用这样的仲裁器,但最常见的仲裁器类型没有固定的优先级。我将在以后的文章中讨论更复杂的仲裁器(循环法)。

建议练习

- 如前所述,这个简单的仲裁器具有固定的优先级。如果多个主控断言它们的请求信号,则编号最小的主控器被赋予gnt。设计一个固定优先级的主机,其中编号最高的主机具有最高优先级。

- 在这个仲裁器中,只要一个主机请求总线,总线就被授予它。添加超时逻辑。如果一个主机断言req超过 10 个时钟周期,如果其他请求未完成,则取消断言对该主机的授权信号。

- 一些仲裁者具有公园功能。Park 的意思是,如果没有未完成的请求,gnt信号将发送给最后一个接收到它的主机。在另一个版本中,如果没有主机断言req,则gnt信号被分配给“默认主机”。为这两个选项中的每一个选项设计代码。

GitHub 上提供了仲裁器“无约束实现”、测试平台和 Modelsim 文件的 VHDL 源代码

- 开源VHDL验证方法 (OSVVM) 0次下载

- VHDL测试平台开源分享 1次下载

- 基于VHDL语言中数字钟的整点报时源代码下载 2次下载

- 基于SaaS的替代性纠纷在线仲裁系统 9次下载

- VHDL语言的详细讲解学习课件免费下载 16次下载

- VHDL最经典的参考指南资料免费下载 31次下载

- VHDL的参考手册免费下载 32次下载

- VHDL测试平台编写综述 19次下载

- 如何进行SOC总线仲裁算法的研究资料说明 5次下载

- 最全面的VHDL例程源码资料下载 113次下载

- PLD Programming Using VHDL 0次下载

- SOC总线仲裁算法的研究 37次下载

- VHDL数位电子钟 174次下载

- SOC总线仲裁算法的研究 14次下载

- PCI总线仲裁器的设计及实现 27次下载

- 例说Verilog HDL和VHDL区别 477次阅读

- 如何在VHDL中解决综合工具使用转化问题 2238次阅读

- 基于CPLD器件实现双主设备PCI总线仲裁器的设计 929次阅读

- Verilog HDL和VHDL的区别 1.2w次阅读

- CAN网络上的仲裁异常分析以及特性与测试建议 3375次阅读

- VHDL语言编程用什么编译软件_需要看哪方面的书籍 3.1w次阅读

- C到VHDL的编译器设计与实现详解 4158次阅读

- CAN总线仲裁示意图_CAN总线位仲裁技术及优缺点 1.5w次阅读

- vhdl和verilog的区别_vhdl和verilog哪个好? 12.1w次阅读

- VHDL语言设计四人抢答器(三种设计方案) 3.5w次阅读

- 基于VHDL的电子计时器的设计方法详解 2.2w次阅读

- vhdl按键控制数码管显示 1.7w次阅读

- 8位移位寄存器vhdl代码 1.6w次阅读

- 我对VHDL的延时理解 3820次阅读

- 基于VHDL的交通灯控制器设计 5753次阅读

下载排行

本周

- 1山景DSP芯片AP8248A2数据手册

- 1.06 MB | 532次下载 | 免费

- 2RK3399完整板原理图(支持平板,盒子VR)

- 3.28 MB | 339次下载 | 免费

- 3TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 4DFM软件使用教程

- 0.84 MB | 295次下载 | 免费

- 5元宇宙深度解析—未来的未来-风口还是泡沫

- 6.40 MB | 227次下载 | 免费

- 6迪文DGUS开发指南

- 31.67 MB | 194次下载 | 免费

- 7元宇宙底层硬件系列报告

- 13.42 MB | 182次下载 | 免费

- 8FP5207XR-G1中文应用手册

- 1.09 MB | 178次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33566次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21549次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6656次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537798次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420027次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191187次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183279次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论