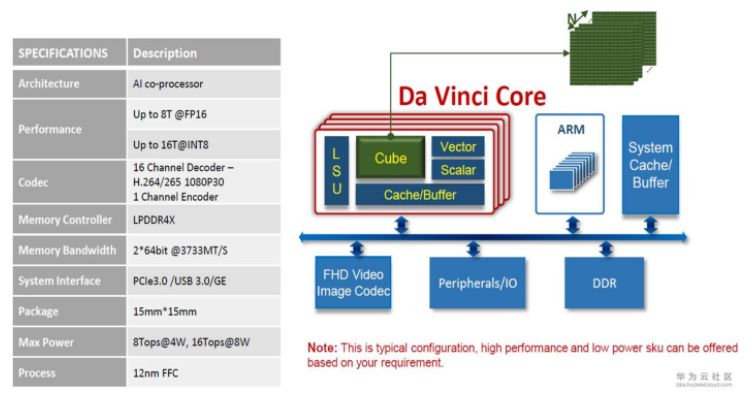

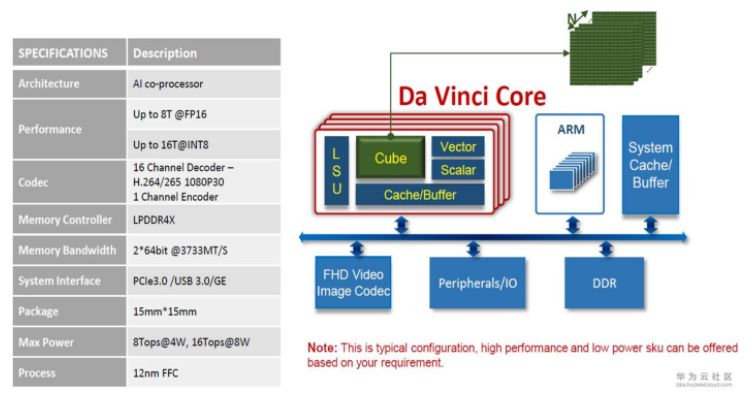

Ascend310 AI处理器逻辑架构昇腾AI处理器的主要架构组成:芯片系统控制CPU(Control CPU)AI计算引擎(包括AI Core和AI CPU)多层级的片上系统缓存(Cache

2023-06-05 14:09:27 5229

5229

人工智能大热,国内外芯片开发商竞相发布自己的AI处理器智能芯片。小编比较了目前主流“AI处理器”的技术和市场

2018-01-19 08:59:22 17858

17858 请问:

1、如果将L1D CACHE设置为32KB,L1P CACHE设置为32KB,L2 CACHE设置为0KB;

在core的LL2中定义了两个数组,out1占用32KB存储空间,out2占用

2018-06-21 13:28:12

作为通用处理器,CPU (Central Processing Unit) 是计算机中不可或缺的计算核心,结合指令集,完成日常工作中多种多样的计算和处理任务。然而近年来,CPU在计算平台领域一统天下的步伐走的并不顺利,可归因于两个方面,即自身约束和需求转移。

2019-08-09 07:42:46

AI芯片作为产业核心,也是技术要求和附加值最高的环节,在AI产业链中的产业价值和战略地位远远大于应用层创新。腾讯发布的《中美两国人工智能产业发展全面解读》报告显示,基础层的处理器/芯片企业数量来看,中国有14家,美国33家。本文将对这一领域产业生态做一个简单梳理。

2019-08-13 08:42:38

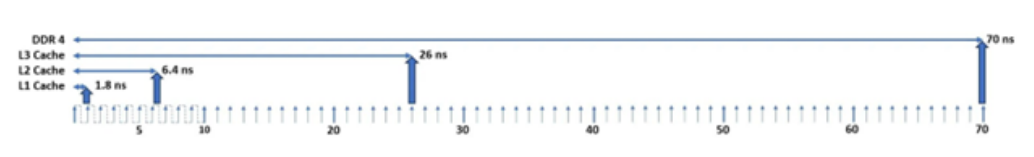

Cache即高速缓存,它的出现基于两种因素:一、CPU的速度和性能提高很快,而主存速度较低且价格高;二、程序执行的局部性特点。将速度较快而容量有限的SRAM构成Cache,可以尽可能发挥CPU

2019-10-12 06:01:10

Cache为什么还要分I-Cache,D-Cache,L2 Cache,作用是什么?

2023-10-25 06:38:45

再一次从cache中丢失。循环的每次迭代都会发生同样的事情,这导致我们的软件性能很差。因此,一般在处理器主要cache中不会使用直接映射cache。组相联cacheARM内核的主要cache一直使用组

2022-06-15 16:16:16

在Multisim的仿真分析中后处理器(postprocesser)应该如何使用?如何在以一个α量为参数运行参数扫描获得两个相关量(设为a,b)的图线后,获得a,b之间的图线?要获得上面的结果是否要使用后处理器?

2013-06-22 16:43:41

处理器中断处理的过程是怎样的?处理器在读内存的过程中,CPU核、cache、MMU如何协同工作?

2021-10-18 08:57:48

深入解析传感器网络中实时通信的研究

2021-05-26 06:00:09

上存在了很久的结构终于出现在ARM的处理器中。X86是复杂指令集,引入Mop Cache可以存储解码后的微指令,这样能够直接bypass fetch和decode的流水线,获得更大的dispatch

2022-09-19 15:02:17

ARM Cortex-M4处理器在C源文件里面调用汇编函数,参数传递机制是怎样的?比如C源文件里面调用汇编语言实现的函数uint8_t Code(uint8_t a,uint32_t b

2022-08-22 15:23:43

。build_mem_type_table()属于early_mm_init()自己的一部分,因此,从early_mm_init()入手,逐步解析CACHE的写机制。early_mm_init(mdesc)early_mm_init() 可以执行了当前Mkernel是否能够执行。原作者:linux-soc

2022-06-30 16:05:05

ARM处理器中引起异常的原因是什么?

2022-11-03 15:20:37

ARM处理器中的逻辑cache和物理cache是什么?有没有哪位大神可以帮忙解决一下这个问题

2022-11-03 15:25:40

早期的ARM处理器使用虚拟地址(virtual addresses)来提供cache index和cache tag。VIVT优点这样做的好处是处理器内核可以使用虚拟地址进行cache look

2022-06-20 15:22:23

的Thumb指令。在程序的执行过程中,微处理器可以随时在两种工作状态之间切换,并且,处理器工作状态的转变并不影响处理器的工作模式和相应寄存器中的内容。但ARM微处理器在开始执行代码时,应该处于ARM状态

2011-01-27 11:13:20

的Thumb指令。在程序的执行过程中,微处理器可以随时在两种工作状态之间切换,并且,处理器工作状态的转变并不影响处理器的工作模式和相应寄存器中的内容。但ARM微处理器在开始执行代码时,应该处于ARM状态

2011-01-27 14:19:05

。ARM复位后PC无条件的指向0x00000000处。MMU是ARM处理器的内存管理单元,CPU管理虚拟存储器、物理存储器的控制线路,同时负责虚拟地址映射为物理地址,以及提供硬件机制的内存访问授权;进行虚拟地址到物理地址的转换通过查找页表来完成,每次在访问内存时先查TLB,查不到再到内存中查整个页表。.

2021-12-21 07:16:24

时的实现工艺。容易实现高性能。RISC体系结构的简单性、有效性很容易设计出低成本、高性能的处理器。RISC技术的历史贡献在计算机设计技术的发展变化中,20世纪60年代初引入的虚拟存储器、Cache和流水线

2022-04-24 10:02:29

ARM处理器设计的机制是如何使得它的运行速度远快于51单片机的运行速度的?求解答

2022-08-04 14:22:11

的cache line为32 bytes。在cache方面,在一个cluster里面的至多4个A9处理器的L1 data cache可以通过SCU的MESI协议做一致性维护。大多数的A9多核系统会外接一

2022-12-14 16:17:15

存储在低地址字节单元中。3. ARM处理器工作状态从编程的角度来看,ARM微处理器的工作状态一般ARM和Thumb有两种,并可在两种状态之间切换。(1)ARM状态:此时处理器执行32位的字对齐ARM

2022-04-13 12:08:30

中断和异常的作用是什么?Cortex-M3处理器中的嵌套向量中断控制器的特性是什么?

2021-11-05 07:25:12

本帖最后由 eehome 于 2013-1-5 10:03 编辑

NAND闪存深入解析

2012-08-09 14:20:47

RK3188处理器有哪些特性呢?RK3168处理器具备哪几大特点呢?RK3126处理器是什么?有何作用?

2022-02-18 07:21:37

的Fujitsu Ten公司同样选择了浮点SHARC处理器ADSP-21364作为数字信号处理引擎,来增强其音频放大器的性能。为汽车驾驶室环境中的音响设备提供高性能输出、先进的声音均衡效果和出众的音质,在众多

2018-12-29 14:15:47

和小型人机界面 (HMI) 应用。TI 将于2022年6月21日至23日在德国纽伦堡的Embedded World展会(215号展位)上展出全新的AM62处理器,并演示适用于边缘AI和电动汽车充电HMI

2022-11-03 06:11:50

方案之一角。 产业界一直在期待英特尔的机器学习计划,这也是近几年半导体产业界最热门的技术领域之一;对此专长人工智能(AI)处理器设计的新创公司Graphcore共同创办人暨执行长Nigel Toon

2016-12-23 16:50:37

微处理器ELANSC520-100AI是如何工作的?这个处理器通电后是怎么工作的,外部给他提供一个FLASH里面是BOOT程序。起上电复位和开机自检作用。

2010-08-28 17:02:50

提供一个新的算法,这需要AI芯片。 在芯片研发的过程中,既有传统的老牌厂商,也有科技新贵,是否会出现像通用CPU那样独立存在的通用AI处理器呢? 事实上,各家技术路线大相径庭,在不同的技术路线

2018-06-14 11:44:13

呵呵,s3c2410...在vivi中的s3c2410.h文件中设置时钟时 有这么一段mrc p15,0,r1,c1,c0,0orr r1,r1,#0xc0000000;mcr p15,0,r1,c1,c0,0这段的每句 的意思是什么?为什么要用到些处理器指令?协处理器指令的作用是干什么?

2019-02-25 12:34:48

、RISC-V等开源社区,主要研究内容为Clang/LLVM、JVM等。

在深入阅读《Android Runtime源码解析》这本书之后,我对Android Runtime的内部机制有了更深入的理解。这本书不仅

2023-11-17 01:33:20

处理器涉及到的主存块内容。在需要读取数据是,处理器可能就会从Cache中读取需要的数据,而不是从主存中获取数据,这样就提高了系统的运行效率。二、ARM处理器的CacheARM处理器支持Cache机制,并将

2016-10-13 18:02:50

字节边界。1.2.2大小端ARM处理器可以将存储器中的字以下列格式存储: 大端格式(Big-endian):字数据的高字节存储在低地址中,而低字节存储在高地址中; 小端格式

2022-04-29 16:41:53

主流四核移动处理器解析

2012-08-20 13:01:36

了解ARM内核的微体系结构,包括寄存器文件的说明及其在处理器中的功能。在本文中,我们将定义什么是微体系结构。我们还将说明什么是ARM寄存器文件以及它在处理器的微体系结构中的位置。本文旨在为下一篇

2020-10-09 07:46:49

:1、如果cacheline 在 L1 cache中找到,则从 L1 cache中读取数据并返回给处理器。2、如果该cacheline 未在 L1 cache中找到,但存在于 L2 cache中,则从

2022-07-20 14:46:15

低功耗DRP-AI动态可配置处理器有哪些关键特性呢?

2021-11-08 09:16:49

CACHE_getMemRegionInfo (129, &pcx, &pfx); 读取pcx的值 仍然是1,所以没起作用。怀疑是当前模式是user mode,而修改MAR寄存器需要

2018-12-28 11:12:02

(postprocessor),帮助电视制造商显著提升液晶电视上高清运动图像的质量。恩智浦全新PNX5100视频后处理器中采用的这一技术结合了影像抖动消除(Movie Judder Cancellation)、运动

2018-08-27 16:14:13

多任务在多核上运行。这样的机制使一份RTOS在系统存储器中拷贝了多份,浪费了一定的存储空间;同时由于对应用程序不透明,需要设计多任务在多核处理器上的调度和运行,增加了应用程序的复杂度,同时需要更多

2019-06-29 08:30:00

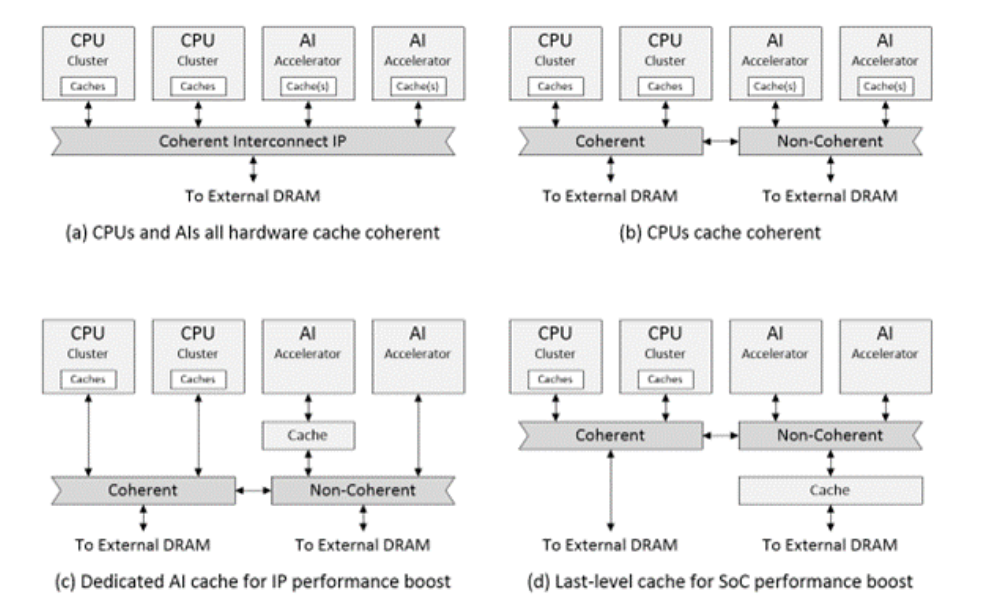

你好我想提出我的两个问题希望我们可以讨论它吗?1.双处理器设计与双核设计之间的差异是什么?2. Xilinx双微填充设计中如何缓存高速缓存一致性。在xilinx WP 262中,声明

2019-03-04 13:41:13

图像处理器在汽车影音系统中的应用是什么?

2021-05-17 06:03:50

看出,信箱寄存器机制需要处理器轮询,所以通信效率不高,在休眠/唤醒这类不频繁的操作中还可以,如果是比较频繁的核间通信就不适用了,要采取中断机制。以上是多核处理器启动的基本原理,至于具体实现,不同的厂商有

2022-06-07 16:41:29

处理器。通过在两个执行内核之间划分任务,多核处理器可在特定的时钟周期内执行更多任务。 多核技术能够使服务器并行处理任务,多核系统更易于扩充,并且能够在更纤巧的外形中融入更强大的处理性能,这种外形所用

2019-06-20 06:47:01

机)节点集成到同一芯片内,各个处理器并行执行不同的线程或进程。在基于SMP结构的单芯片多处理机中,处理器之间通过片外Cache或者是片外的共享存储器来进行通信。而基于DSM结构的单芯片多处理器中,处理器间

2011-04-13 09:48:17

处理器涉及到的主存块内容。在需要读取数据是,处理器可能就会从Cache中读取需要的数据,而不是从主存中获取数据,这样就提高了系统的运行效率。更多嵌入式学习 2848988085二、ARM处理器

2016-08-31 16:30:26

针对汽车数字信号处理应用的各种处理器类型,有什么优缺点?如何选择汽车电子系统中的处理器?

2021-05-14 06:59:41

。5.协处理器寄存器传送除了以上情况,在ARM和协处理器寄存器之间传送数据有时是有用的。再以使用浮点协处理器为例,FIX指令从协处理器寄存器取得浮点数据,将它转换为整数,并将整数传送到ARM寄存器中

2022-04-24 09:36:47

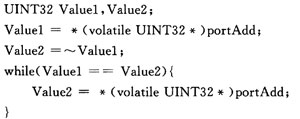

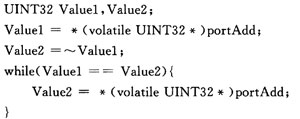

直接运行ELF文件,情况也是一样,拷贝完代码后一定要刷新Cache,以免不测。 还有,对硬件的操作要小心。很多寄存器值都是被硬件改变的,读写时,要保证确实访问到它的地址。首先,在C语言代码中声明

2017-08-19 22:42:08

随着嵌入式计算机应用的发展,嵌入式CPU的主频不断提高,这就造成了慢速系统存储器不能匹配高速CPU处理能力的情况。为了解决这个问题,许多高性能的嵌入式处理器内部集成了高速缓存Cache。其中,三星公司的S3C44B0X内部就集成了8KB空间统一的指令和数据Cache。

2019-09-05 07:00:20

嵌入式处理器动态分支预测机制研究与设计针对嵌入式处理器的特定应用环境,通过对传统神经网络算法的改进,结合定制的分支目标缓冲,提出一种复合式动态分支预测机制。该机制基于全局索引方式,对BTB结构进行

2009-10-06 09:53:06

如何选择汽车电子系统中的处理器?针对汽车应用的信号处理器有哪些?

2021-05-19 07:14:49

应用处理器也将使用该公司的 Neutron IP。“我们制定了针对可能使用相同 2-TOPS 更具体垂直市场器件的计划,但即使在该变体中,我们提供的内部缓冲区数量或我们提供的内部接口也可能有

2023-02-16 11:20:03

`` 为什么发起AI芯片设计众筹 ?1、传统指令驱动的处理器(CPU和GPU)已经无法支持数据驱动的AI技术,专用AI芯片已成为市场真实的强劲的需求,拥有AI芯片开发能力和经验的工程师将会受到产业

2019-07-19 11:54:01

,探讨一下其在AI领域的应用前景。这个分析会分为几个章节,首先介绍下vector的历史。Vector这个概念是相对于Scalar提出的。最初的通用处理器都是标量处理器(Scalar Processor

2022-09-19 15:18:24

本文设计了一种在多处理器系统中的Nios II软核处理器的启动方案,这个方案在外部处理器向Nios II的程序存储器和数据存储器加载数据时,可以控制Nios II处理器的启动。

2021-04-27 06:52:42

时决定替换掉哪一个way的cacheline;写策略cache收到处理器内核的写请求时,相应的cache行为,例如是否先写到cache中,等到实在有必要时再写入到主存中。分配策略当处理器内核

2022-06-15 16:24:48

看出,信箱寄存器机制需要处理器轮询,所以通信效率不高,在休眠/唤醒这类不频繁的操作中还可以,如果是比较频繁的核间通信就不适用了,要采取中断机制。以上是多核处理器启动的基本原理,至于具体实现,不同的厂商有

2022-07-19 15:00:47

视频后处理器PNX5100有什么作用?

2021-06-02 06:32:46

的系统控制和配置”、“MMC 控制和管理”、“cache 控制和管理”和“系统性能监控”功能。 在 ARM 的汇编代码中,凡是看到“mrc”和“mcr”指令,就表明接下来有一小段代码用来控制协处理器

2019-07-29 15:36:26

这个问题用PSoC Creator 3.3(3.3.0.410)进行。你好社区我问你关于一个问题的帮助(Bug?)在PSoC Creator。我想要的是:在编译环境中定义一个带有处理器值的预处理器

2019-02-22 06:25:24

,指令cache和数据cache是同一个,在优化后的哈弗架构中使用独立的指令cache(I-cache)和数据cache(D-cache),即可以同时访问指令和数据。在ARMv8处理器中,L1

2022-06-15 16:30:39

摘要:在SoC系统中,片上缓存(Cache)的采用是解决片上处理器和片外存储器之间速度差异的重要方法,Cache中用来存储标记位并判断Cache是否命中的Tag电路的设计将会影响到整个Cache的

2010-05-08 09:26:24 11

11 嵌入式编程需注意的Cache机制及其原理

1 Cache的原理 Cache即高速缓存,它的出现基于两种因素:一、CPU的速度和性能提高很快,而主

2010-05-26 16:40:03 1153

1153

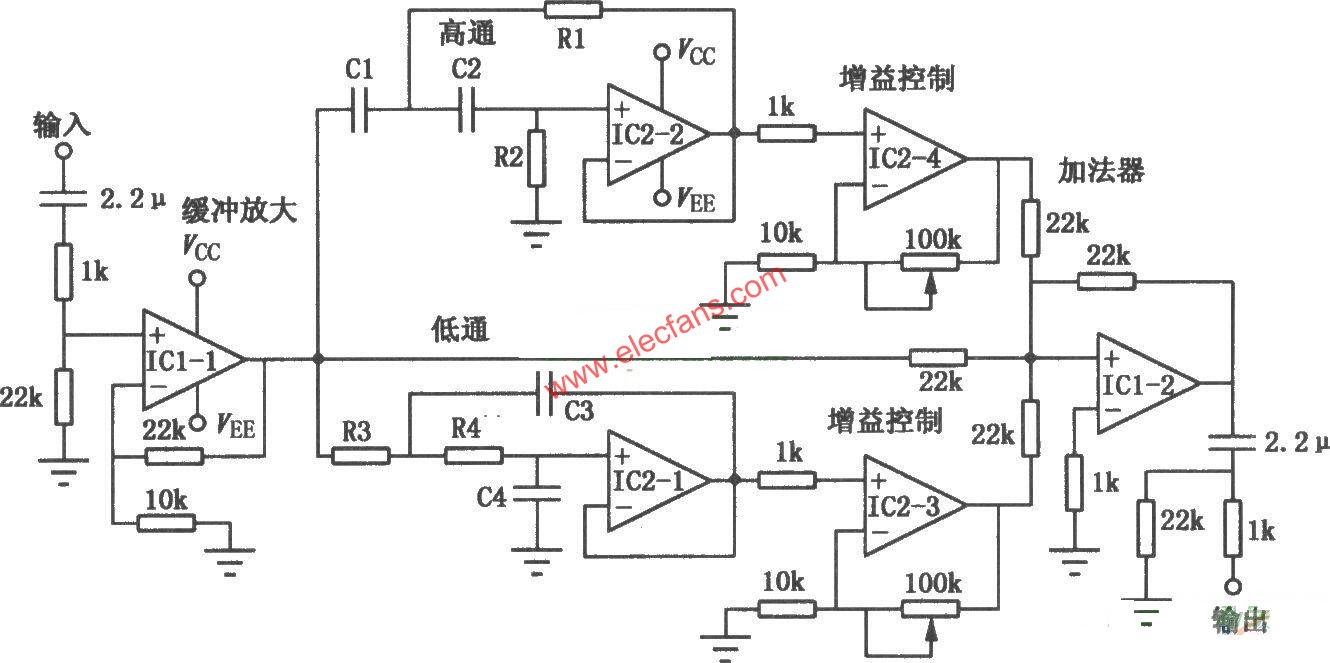

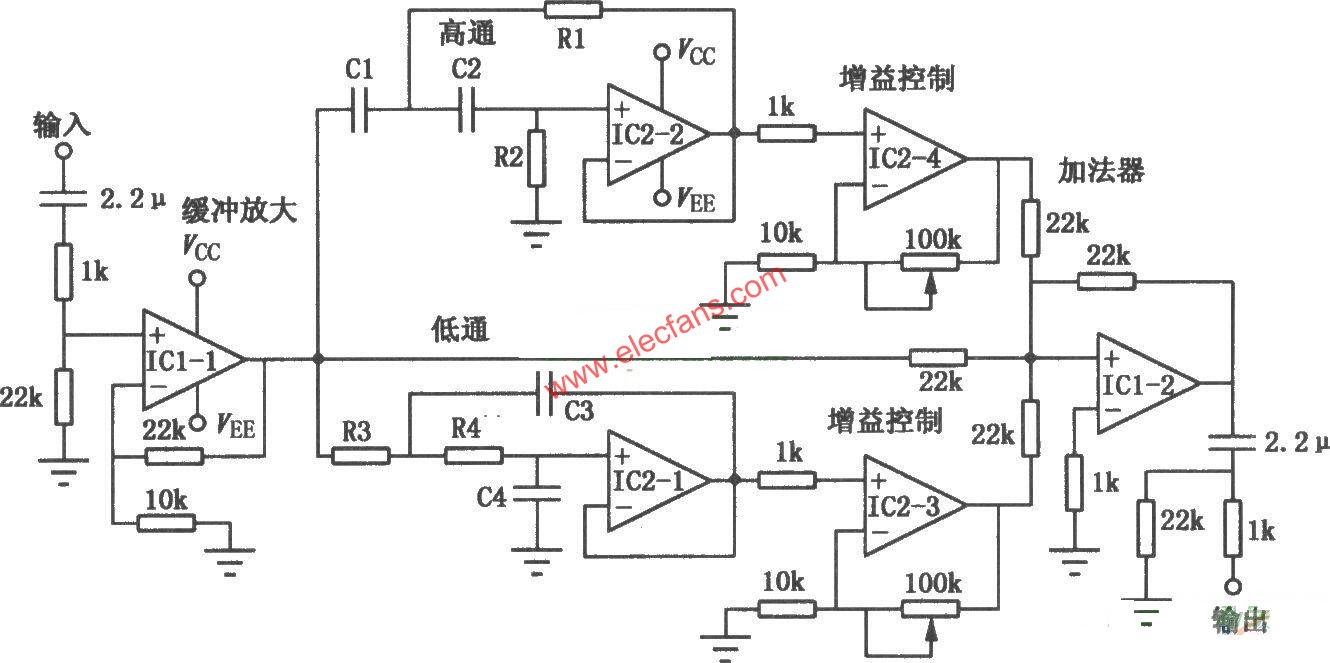

BBE高解析力声音处理器的原理是将信号源的高、中、低频信号分别经高通滤波器、带通滤波器、低通滤波器输出,然后分别控

2010-11-26 12:07:08 2570

2570

:本文给出了一种 处理器 系统接口部件的具体设计方案。该接口部件通过使用Split读和片外Cache来提高处理器的性能。测试结果表明,Split读和片外Cache能够以比较低的代价使处理器性能得

2011-06-29 15:59:52 10

10 现代高速处理器的设计中对于cache技术的研究已经成为了提高处理器性能的关键技术,本文针对在流水线结构中采用非阻塞cache技术进行分析研究,提高cache的命中率,降低缺少代价,提高处理器的性能,并介绍了“龙腾”R2处理器的流水线结构的非阻塞cache 的设计。

2015-12-28 09:54:57 8

8 多核密码处理器数据缓存机制研究_陈晓钢

2017-01-07 18:39:17 0

0 深入剖析Android消息机制

2017-01-22 21:11:02 11

11 STM32的USB库深入解析

2017-10-15 09:21:33 87

87 基于高通Adreno图形处理器全解析

2017-10-30 16:15:18 11

11 全彩LED显示屏为何非得要用视频处理器这个问题,一点不夸张的说视频处理器的优劣直接决定了全彩LED显示屏的一个显示效果。下面就来介绍下LED视频处理器的主要作用。

2018-01-18 13:53:08 10289

10289 AI已经深入到社会经济的很多领域,尤其进来在手机行业掀起了一股AI的狂潮。很多智能手机搭载了AI处理器,经具备了AI的功能和应用。当前小米、vivo、OPPO等众多OEM厂商的旗下智能手机诸多新品

2018-06-28 06:32:00 809

809 日前,高通宣布推出骁龙632处理器、439处理器和429处理器。这三款处理器可以支持广泛的终端侧AI用例,在AI能力、性能、图形处理等方面都有所增强。可以进一步提升中端和入门级智能手机市场性能

2018-07-10 11:20:00 942

942 本文主要阐述了音频处理器的作用及音频处理器和效果器的区别。

2020-04-09 10:41:49 28772

28772 处理器的作用是什么?跟着我一起了解下。

2020-06-10 09:40:11 17097

17097 数据 Cache的实时动态迁移机制,采用四级全互连和迁移互连,以数据访问频率为依据对远程数据进行动态调度,有效降低了远程访存的延迟。并基于阵列处理器分布式¢ache结构,通过运动补偿等典型算法的并行实现,对所提出的实时

2021-04-07 15:09:11 20

20 Linux内核文件Cache机制(开关电源技术与设计 第二版)-Linux内核文件Cache机制

2021-08-31 16:34:54 4

4 可以随便到网上查一查,各大互联网公司笔试面试特别喜欢考一道算法题,即 LRU缓存机制,又顺手查了一下LRU缓存机制最近有哪些企业喜欢考察,超级大热门! 今天给大家分享一篇关于 Cache 的硬核

2021-09-01 14:55:26 3800

3800

作者:Spongecaptain https://spongecaptain.cool/SimpleClearFileIO/ 1. Page Cache 1.1 Page Cache

2021-10-20 14:12:41 5329

5329

L1 Cache和L2 Cache通常和处理器是在一块实现的。在SoC中,主存和处理器之间通过总线SYSBUS连接起来。

2023-01-08 10:56:03 569

569 按照数据关系划分:Inclusive/exclusive Cache: 下级Cache包含上级的数据叫inclusive Cache。不包含叫exclusive Cache。举个例子,L3 Cache里有L2 Cache的数据,则L2 Cache叫exclusive Cache。

2023-05-30 16:02:34 422

422

ARP学习和老化机制在Linux网络通信中起着至关重要的作用。ARP(Address Resolution Protocol)地址解析协议是将IP地址解析为MAC地址的一种机制。

2023-08-04 16:55:27 850

850

电子发烧友App

电子发烧友App

评论