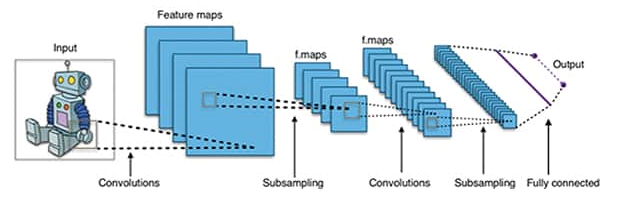

使用 C 语言的OpenCL 2a并行编程扩展来补充基于 FPGA 的 CNN 加速应用程序的开发。适用于卷积神经网络的 FPGA 器件的一个示例是英特尔可编程解决方案集团 (PSG)的Arria 10系列器件,其正式名称为Altera。

2022-08-02 15:13:16 2607

2607

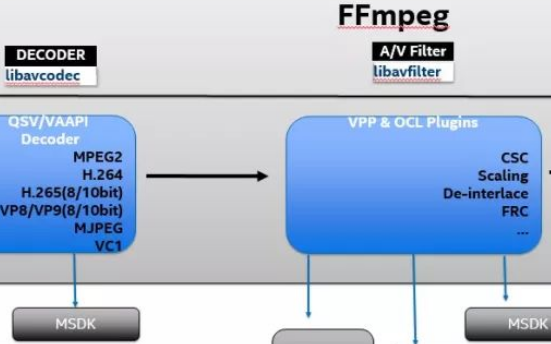

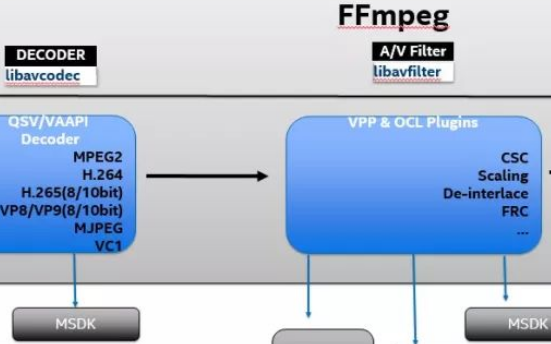

被称为“多媒体技术领域的瑞士军刀”,FFmpeg拥有广泛的应用基础。不过,当(实时)处理海量视频时,需要借助各种方法提升效率。本文将纵览FFmpeg的硬件加速方案,涉及各主流硬件方案和操作系统。

2018-05-18 09:03:30 8487

8487

大小调整,另一种使用Xilinx xfopencv library实现了在FPGA上硬件加速的图像大小调整。 初始化 1. 首先在SD卡内配置Pynq-Z2最新镜像PYNQ image v2.5并烧录

2020-11-19 15:29:43 3044

3044 作者:雪湖科技 梅碧峰 在这篇文章里你可以了解到广告推荐算法Wide and deep模型的相关知识和搭建方法,还能了解到模型优化和评估的方式。我还为你准备了将模型部署到赛灵思 FPGA上做硬件加速

2020-11-27 10:46:44 2669

2669

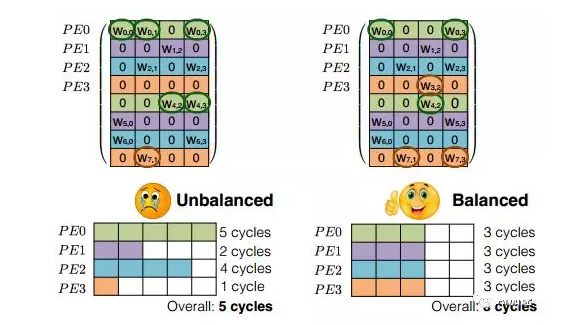

的应用于语音识别、机器翻译、手写识别等。LSTM涉及到大量的矩阵乘法和向量乘法运算,会消耗大量的FPGA计算资源和带宽。为了实现硬件加速,提出了稀疏LSTM。核心是通过剪枝算法去除影响较小的权重,不断迭代训练以达到目标函数收敛。参与实际运算的权重数量大大缩减,这可以有效降低FPGA计算资源

2020-11-29 11:24:19 2746

2746 利用硬件模块来替代软件算法以充分利用硬件所固有的快速特性(硬件加速通常比软件算法的效率要高),从而达到性能提升、成本优化目的,当前主要是如下两大加速方式:FPGA 现场可编程门阵列,可针对某个具体的软件

2017-12-29 11:25:28

FPGA 管脚分配需要考虑的因素FPGA 管脚分配需要考虑的因素 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好

2012-08-11 10:27:54

考虑如何解决计算需求的增长,而FPGA作为一种可编程的加速硬件彼时进入了大家的视野。有了解决计算需求的想法后,需要通过实践验证FPGA实际的能力。腾讯的QQ、微信业务,用户每天产生的图片数量都是数亿级别

2017-04-15 16:17:41

FPGA电源排序考虑因素

2018-09-10 10:54:14

时候就更需要考虑各方面的因素。

综合起来主要考虑以下的几个方面:1、 FPGA所承载逻辑的信号流向。IC 验证中所选用的 FPGA一般逻辑容量都非常大,外部的管脚数量也相当的丰富,这个时候就必须考虑

2024-01-10 22:40:14

FPGA管脚分配需要考虑的因素 FPGA 管脚分配需要考虑的因素 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好

2012-08-11 11:34:24

依赖人,而非工具,这个时候就更需要考虑各方面的因素。 综合起来主要考虑以下的几个方面: 1、 FPGA所承载逻辑的信号流向。 IC 验证中所选用的 FPGA一般逻辑容量都非常大,外部的管脚数量也相当

2017-03-25 18:46:25

FPGA管脚分配需要考虑的因素.pdf

2012-08-20 19:23:04

适用于Firefly-RK3288的板子* rockchip kernel 4.4 (VPU, GPU, DRM RGA and WIFI设备驱动)* rockchip debian stretch (xserver已加入GPU加速,带硬件加速的gstreamer )

2017-08-19 15:10:30

算法的软件实现方式非常低效,所以业界对GNN的硬件加速有着非常迫切的需求。我们知道传统的CNN(卷积神经网络网络)硬件加速方案已经有非常多的解决方案;但是,GNN的硬件加速尚未得到充分的讨论和研究,在

2021-07-07 08:00:00

H.264解码器中CABAC硬件加速器怎么实现?

2021-06-07 06:48:58

差距,如果仅需要SDP或FPU进行运算加速,又不想选用高单价SOC,这时整合DSP或FPU硬件加速单元的 MCU产品、不仅可以更好的提供运行效能,同时又能在成本控制上表现更加优异。MCU整合芯片封装

2016-10-14 17:17:54

基于Xilinx XCKU115的半高PCIe x8 硬件加速卡一、概述 本板卡系我公司自主研发,采用Xilinx公司的XCKU115-3-FLVF1924-E芯片作为主处理器,主要用于FPGA

2019-10-25 16:00:50

目前我使用NI的机箱采集数据,labview做软件平台生成一个系统。想要达到实时性效果。能否给NI或labview采用硬件加速,提高处理速的呢?如何做呢?有什么资料可以参考?

2018-09-29 09:34:24

项目名称:图像目标识别FPGA硬件加速试用计划:申请理由 本人供职于一家AI公司,现在在使用FPGA硬件加速相关目标检测算法的端侧实现(鉴黄/司机行为识别),公司已经有非常成熟的软件算法以及GPU

2019-01-09 14:51:09

FPGA上进行编译和部署。

由于文本到视频生成模型Sora的复杂性,FPGA加速的具体实现将取决于模型的细节、FPGA的硬件资源以及可用的高级综合工具。通常,这需要一个专业的团队,包括硬件工程师、深度学习

2024-02-22 09:49:01

项目名称:基于ZYNQ的人脸识别系统试用计划:申请理由本人为某学校博士生,从事计算机视觉,深度学习,及其硬件加速的研究。有一定FPGA编程经验(VHDL),和嵌入式ARM,Arduino版的开发经验

2019-10-30 17:03:42

我想进入硬件加速。什么板对此有好处,为什么?

2019-10-10 07:00:38

扩频振荡器在汽车电子设计中的优势是什么?汽车电子产品的设计考虑因素有哪些?为时钟源加入抖动之前需要考虑哪些因素?

2021-05-17 06:41:57

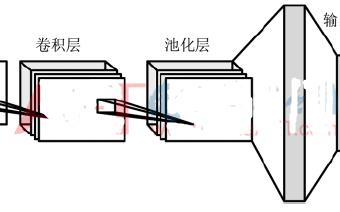

流水线结构和很强 的并行处理能力,还拥有低功耗、配置方便灵活的特性,可以根据应用需要来编程定制硬 件,已成为研究实现 CNN 硬件加速的热门平台。

综上所述,使用功耗低、并行度高的 FPGA 平台加速

2023-06-20 19:45:12

基于Xilinx XCKU115的半高PCIe x8 硬件加速卡一、概述本板卡系我公司自主研发,采用Xilinx公司的XCKU115-3-FLVF1924-E芯片作为主处理器,主要用于FPGA

2018-07-27 16:49:30

,主要用于FPGA硬件加速。板卡设计满足工业级要求。如下图所示: 图 1:硬件加速卡实物图 二、技术指标图 2:硬件加速卡结构框图 标准PCIe半高、半长卡,符合PCI Express 3.0 规范

2018-08-22 17:31:55

面,可能会导致误判。尝试改正后,生成的密钥是正常的,但速度比OpenSSL纯软件慢。正常使用RSA硬件加速能多快生成2048bit的密钥?这个补丁有优化版吗?

2023-05-06 08:05:44

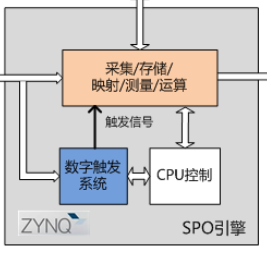

上的片内FIR和IIR硬件加速器也分别称为FIRA和IIRA,我们可以利用这些硬件加速器来分担FIR和IIR处理任务,让内核去执行其他处理任务。在本文中,我们将借助不同的使用模型以及实时测试示例来探讨如何在实践中利用这些加速器。

2020-12-28 06:26:54

训练一个神经网络并移植到Lattice FPGA上,通常需要开发人员既要懂软件又要懂数字电路设计,是个不容易的事。好在FPGA厂商为我们提供了许多工具和IP,我们可以在这些工具和IP的基础上做

2020-11-26 07:46:03

opencv编译和运行时,使用的是安装的GStreamer视频IO,那么如何让opencv使用官方的GStreamer-rockchip实现硬件加速呢?

2022-04-08 15:25:33

。随着电机的加速,它具有各种谐振速度/频率,基于其独特的结构和机械设计。在使用VFD时必须考虑这些因素,特别是您想要操作的速度范围。 逆变器负载线 绕组必须绝缘,适合变频器负载(或VFD操作

2021-01-19 15:12:20

--高级--疑难解答中的硬件加速是否完全开启。 3、如果是游戏不能玩了。显示属性--设置--高级--适配器--列出所有模式,将该项的数据设置的比平时稍低一些。也就是降低刷新率及分辨率。 3d硬件加速

2019-08-21 09:04:31

嗨!我已经创建了一个硬件加速器(在vhdl中)并且合成成功完成。但是,当我使用创建和导入外围设备向导时,它向我显示我的包在库中不可用,尽管它是。我能做什么 ???L'enfer,c'est l

2019-02-27 14:15:31

,其算法的软件实现方式非常低效,所以业界对GNN的硬件加速有着非常迫切的需求。我们知道传统的CNN(卷积神经网络网络)硬件加速方案已经有非常多的解决方案;但是,GNN的硬件加速尚未得到充分的讨论和研究

2020-10-20 09:48:39

,详细介绍相关片内硬件模块在GUI系统中的角色及实现方式;(由于GPU模块硬件的源码的开源程度不高,不在本文的分析范围内)分析现有GUI框架下,在硬件加速方面,我们能做的事情,并以非常简单的图像处理为

2019-04-02 21:42:10

半高PCIe x8硬件加速卡有哪些技术指标?半高PCIe x8硬件加速卡的物理特性是什么?半高PCIe x8硬件加速卡的接口测试软件有哪些?

2021-06-25 07:16:05

什么是虚拟仪器?设计虚拟仪器的硬件部分时需要考虑哪些因素?

2021-05-07 06:32:21

、F4、F7 等子目录,但没有 H7。H7 的子目录仅存在于 Fw_Crypto 下。在 en.patchx_cryptolib_3-1-3.zip 中有 G0、G4、L5、WB 和 H7A3 的子目录。我想,所有这些都只是软件?哪个包包含 H753 的硬件加速库 (AccHw_Crypto)?

2023-01-17 06:22:46

ASIC、FPGA和DSP的应用领域呈现相互覆盖的趋势,使设计人员必须在软件无线电结构设计中重新考虑器件选择策略问题。从可编程性、集成度、开发周期、性能和功率五个方面探究,你会发现软件无线电设计中选择ASIC、FPGA和DSP时需要考虑哪些因素?

2019-08-16 07:51:25

问下ARM3的硬件加速器只能用verilog写吗?

2022-09-30 10:45:39

卸载,相对于QAT并不具有加速作用。方案三是FPGA卡方案,相对来说开发成本较高,且相关资源匮乏。综上评估,选择方案一对Gzip进行卸载及加速。Tengine Gzip 硬件加速方案实践左边的图是软件

2018-06-04 17:07:55

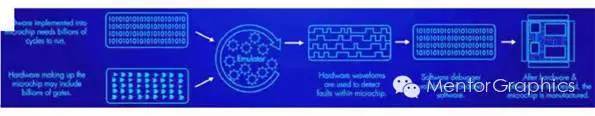

摘要:在芯片规模指数式上升和要求面市时间快速缩短的双重压力下,验证已成为数字集成电路设计的瓶颈。利用硬件加速验证技术能很好地解决这一问题。该文论述了硬件加速验

2010-04-26 10:20:15 16

16 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约

2010-06-24 17:43:35 29

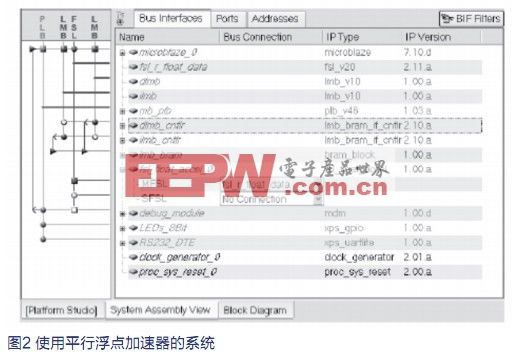

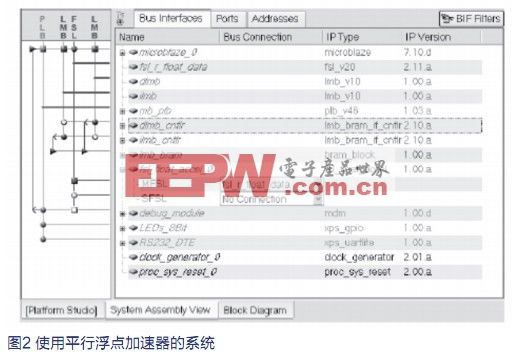

29 采用硬件加速发挥MicroBlaze处理能力

MicroBlaze处理器是赛灵思(Xilinx)在嵌入式开发套件 (EDK) 中提供的两款32位内核之一,是实现硬件加速的灵活工具。图1是MicroBlaze的

2010-03-10 10:24:16 1132

1132

简述了爱普生S1D13A05芯片的架构特征,并且介绍了其中的2D硬件加速引擎的工作模式和相关的寄存器设置,最后以VxWorks操作系统作为开发环境,基于风河公司WindML图形开发包,对S1D13A0

2011-09-01 14:07:47 960

960

针对复杂算法中矩阵运算量大, 计算复杂, 耗时多, 制约算法在线计算性能的问题, 从硬件实现角度, 研究基于FPGA/Nios-Ⅱ的矩阵运算硬件加速器设计, 实现矩阵并行计算。首先根据矩阵运算

2011-12-06 17:30:41 89

89 电子发烧友网核心提示: 获奖的Nios II 嵌入式处理器C语言至硬件(C2H)加速编译器将对时间要求较高的ANSI C函数转换为FPGA中的硬件加速器,从而提高了性能。 特性: (1)ANSI/ISO C 代码按键

2012-10-17 14:29:34 1901

1901

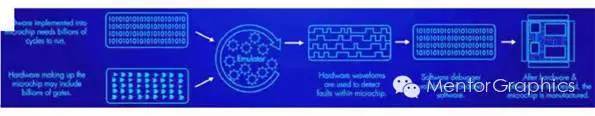

俄勒冈州威尔逊维尔,2016 年 4 月 20 日 — Mentor Graphics公司(纳斯达克代码:MENT)今日宣布,Mentor® 硬件加速仿真服务采用具有专业服务和 IP 的 Veloce® 硬件加速仿真平台 ,借此加速仿真验证并降低与片上系统 (SoC) 设计相关的风险。

2016-04-20 11:22:08 2307

2307 本文主要介绍了在FPGA开发过程中管脚分配时需要考虑的一些实际因素,减少后续开发过程中发生一些细节性的错误。

2016-05-25 10:01:13 18

18 基于硬件加速的实时仿真平台构建技术_孔璐

2017-01-03 17:41:58 1

1 在CAPI规范问世之前,使用FPGA来做硬件加速的过程很费劲。它是把FPGA做到一块PCIe板卡里,FPGA通过CPU的PCIe控制器访问主机内存空间。因为所有的CPU线程看到的都是单一虚拟地址空间

2017-02-08 14:13:11 202

202

这是必然趋势,肯定有人会通过云访问 FPGA 硬件加速功能。 Bitfusion 既开发软件,又设计硬件,并且与 Rackspace 协作共同创建专用于加速云计算的数据中心。这一理念与 FPGA

2017-02-08 19:48:30 238

238 。 本文所聚焦的技术手段是让一个已有的UVM验证平台通过改变需求去执行硬件加速。如果这些点在UVM环境开发过程中被考虑到,那么之后将环境迁移到硬件加速器作为一个性能选项将是一件较容易的事情。本文所提议的建议将会使你的UVM验证

2017-09-15 17:08:11 14

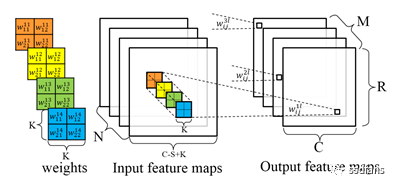

14 基于FPGA的通用CNN加速器整体框架如下,通过Caffe/Tensorflow/Mxnet等框架训练出来的CNN模型,通过编译器的一系列优化生成模型对应的指令;同时,图片数据和模型权重数据按照优化规则进行预处理以及压缩后通过PCIe下发到FPGA加速器中

2017-10-27 14:09:58 9882

9882

基于混合架构的硬件加速是计算机领域中很重要的研究方向之一。它是指将一些特定的任务从通用CPU移植到硬件处理模块上并进行相应的算法优化。由于硬件设备的专用结构,这些硬件处理模块往往比在基于顺序指令集

2017-11-03 16:29:44 13

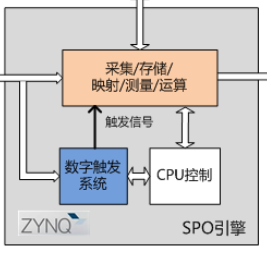

13 Xilinx Zynq-7000 全可编程 SoC (AP SoC) 系列集成 ARM处理器的软件可编程性与 FPGA 的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上高度集成 CPU、DSP、ASSP 以及混合信号功能。

2017-11-07 14:37:52 7144

7144

电路实现,根据硬件电路工作频率高和数据位宽自定义,可以解决延时长和数据宽度受限的缺点。实验结果表明,边缘检测硬件加速方法不仅使延时和数据带宽都得到了改善,而且也缩短了边缘检测的开发周期。

2017-11-15 18:02:01 1874

1874

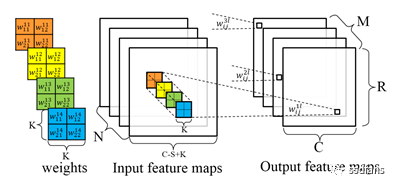

刚好在知乎上看到这个问题 如何用FPGA加速卷积神经网络CNN,恰巧我的硕士毕业设计做的就是在FPGA上实现CNN的架构,在此和大家分享。 先说一下背景,这个项目的目标硬件是Xilinx的PYNQ

2018-06-29 07:55:00 4538

4538

处理器内部集成的硬件加速器可以实现三种广泛使用的信号处理操作:FIR(有限冲激响应)、IIR(无限冲激响应)和FFT(快速傅里叶变换)。硬件加速器减轻了核处理器的负担,能潜在的提升处理器的计算吞吐

2017-12-04 15:22:36 1036

1036 针对MD5软件实现方法存在占用资源大、安全性差等缺点,提出了基于NetMagic平台的MD5硬件加速模型设计方案,并基于ModelSim和NetMagic平台对提出的非流水线与流水线硬件加速模型进行

2018-01-12 16:45:07 0

0 很多人认为硬件加速器无非是一种速度更快的仿真器而已。毫无疑问,由于硬件加速器使用物理硬件进行仿真,使用硬件加速器验证复杂的集成电路和大型片上系统(SoC)能比软件仿真器快若干数量级。与仿真用通用计算机相比,仿真用单一功能计算机能提供更高容量、更高效的系统。

2018-03-28 14:50:00 3160

3160

正确利用硬件加速器对逻辑仿真进行加速是非常有效的。如果知道某项设计在仿真中的运行速度(用每秒仿真了多少设计时钟来衡量),你就能很容易地估计出该设计的原始性能。举个例子,我们假设仿真器以每秒1000

2018-03-05 10:13:13 3

3 在近日举行的2018上海世界移动大会期间,中国电信、英特尔、联想与赛特斯联合发布了基于FPGA的一系列vBRAS解决方案,包括vBRAS IPv6方案、vBRAS P4方案、vBRAS FPGA硬件加速解决方案。

2018-08-14 16:20:36 1007

1007 Vivado HLS是Xilinx公司推出的加速数字系统设计开发工具,直接使用C、C++或SystemC开发的高层描述来综合数字硬件,替代用VHDL或Verilog实现FPGA硬件设计[6],实现设计的功能和硬件分离,不需要关心低层次具体细节,具有很强的灵活性,有效降低数字系统设计开发周期。

2018-10-04 10:41:00 7096

7096

本教程讨论基于Xilinx FPGA的Memcached硬件加速器的技术细节,该硬件加速器可为10G以太网端口提供线速Memcached服务。

2018-11-27 06:41:00 3433

3433 和网络加速应用而设计的,并基于Speedster22i FPGA系列相同的高性能架构,采用Speedcore作为硬件加速器的方案被广泛应用到数据中心和通信基础设施等领域。据了解,eFPGA IP授权业务

2018-12-23 16:29:40 4151

4151 摩尔定律从2003年开始放缓。为了延续性能倍增、功耗减半,Intel CPU采用多核来实现。然而,到2015年以后,多核也达不到了。内核数每增加一倍,运算性能并不能成倍增长。因此,业界需要寻找新的方法来实现延续,比如针对应用进行硬件加速。

2019-01-14 13:58:08 1278

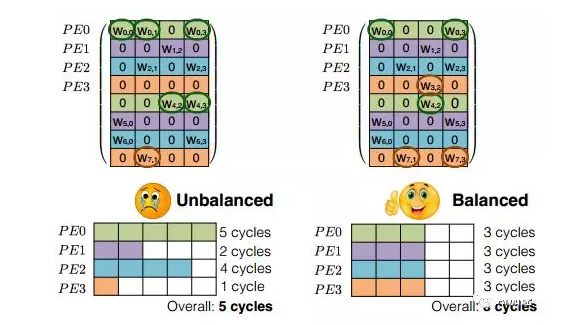

1278 网上对于FPGACNN加速的研究已经很多了,神经网络的硬件加速似乎已经满大街都是了,这里我们暂且不讨论谁做的好谁做的不好,我们只是根据许许多多的经验来总结一下实现硬件加速,需要哪些知识,考虑哪些因素。

2019-02-14 14:25:46 1222

1222 硬件加速仿真可以实现寄存器传输级(RTL)和现代SoC设计门级的最佳功耗分析。只有硬件加速仿真才有处理大量逻辑以及产生针对所有元素的切换活动的独有能力。

2019-10-11 17:54:29 4550

4550

硬件加速是指在计算机中通过把计算量非常大的工作分配给专门的硬件来处理以减轻中央处理器的工作量之技术。尤其是在图像处理中这个技术经常被使用。

2019-08-15 15:29:35 6839

6839

Long-short term memory,简称LSTM,被广泛的应用于语音识别、机器翻译、手写识别等。LSTM涉及到大量的矩阵乘法和向量乘法运算,会消耗大量的FPGA计算资源和带宽。为了实现硬件加速,提出了稀疏LSTM。

2019-08-24 10:32:35 2798

2798

FPGA加速卡采用CAPI接口设计,通过CAPI接口与P&P服务器紧密集成;应用于大数据分析、密码解算、图像图片处理等领域,实现百倍的加速比;

2020-07-07 16:16:12 16

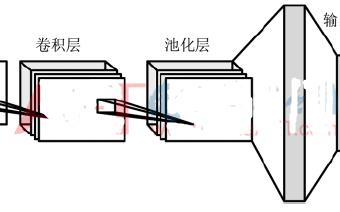

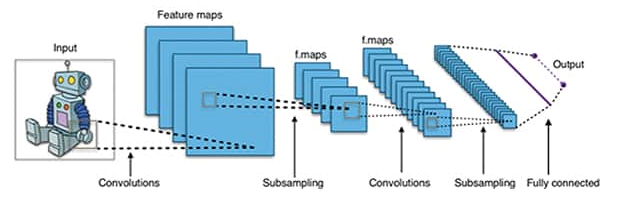

16 随着近些年深度学习的迅速发展和广泛的应用,卷积神经网络(CNN)已经成为检测和识别领域最好的方法,它可以自动地从数据集中学习提取特征,而且网络层数越多,提取的特征越有全局性。通过局部连接和权值共享

2020-07-15 21:00:05 2445

2445

OpenHarmony 分论坛-华秋电子新硬件加速器 今天的华为开发者大会2021上,OpenHarmony分论坛上展示了华秋电子新硬件加速器 。 HDC分论坛-OpenHarmony 分论坛推荐链接:http://t.elecfans.com/live/1708.html 责任编辑:haq

2021-10-23 16:53:48 1500

1500

电子学报第七期《一种可配置的CNN协加速器的FPGA实现方法》

2021-11-18 16:31:06 15

15 本项目采用Cortex-M3软核做控制部分,大规模专用硬件加速器做滤波跟踪计算和智能目标检测部分,视频输入输出通过HDMI直接进入硬件加速器,绕过软核实现更快的数据处理速度。

2022-05-16 10:04:26 959

959 自 2021 年 10 月起,NVIDIA 和 Open Robotics 开始合作并推出了两项重要的改动,现已发布在Humble ROS 2版本中,以提高提供硬件加速器的计算平台的性能。

2022-07-07 09:45:07 2471

2471 在开发一个加速程序的之前,有一个很重要的步骤:正确设计程序架构。开发人员需要明确软件应用程序中哪一部分是需要硬件加速的,并且它多少的并行量,以保证硬件加速器件(FPGA)能完美发挥其作用。本文将分为5个步骤来介绍

2022-08-02 10:33:07 386

386

当 AI 设计人员将硬件加速器整合到用于训练和推理应用的定制芯片中时,应考虑以下四个因素

2022-08-19 11:35:55 1267

1267

该项目基于AMD Xilinx Varium C1100 FPGA加速卡,为 Filecoin 区块链应用中的Poseidon哈希算法提供了一套完整的硬件加速方案。

2022-08-19 10:25:02 2367

2367 借助硬件加速器开发您的设计

2023-01-03 09:45:15 594

594 本文重点解释如何使用硬件转换卷积神经网络(CNN),并特别介绍使用带CNN硬件加速器的人工智能(AI)微控制器在物联网(IoT)边缘实现人工智能应用所带来的好处。 AI应用通常需要消耗大量能源,并以

2023-05-16 01:05:03 467

467 因为CNN的特有计算模式,通用处理器对于CNN实现效率并不高,不能满足性能要求。 因此,近来已经提出了基于FPGA,GPU甚至ASIC设计的各种加速器来提高CNN设计的性能。

2023-06-14 16:03:43 1453

1453

电子发烧友网站提供《硬件加速人体姿态估计开源分享.zip》资料免费下载

2023-06-25 10:27:00 0

0 只有充分考虑这些因素,才能设计出一款适合户外活动需要的储能电源。从而为户外活动提供更加可靠、安全、便捷的能源支持

2023-07-21 15:17:56 437

437

电子发烧友网站提供《硬件加速自然语言理解解决方案.pdf》资料免费下载

2023-09-13 10:45:12 0

0 电子发烧友网站提供《Hyperon—大数据应用的硬件加速解决方案.pdf》资料免费下载

2023-09-13 10:12:43 0

0 电子发烧友网站提供《Alveo卡的区块链硬件加速器解决方案.pdf》资料免费下载

2023-09-15 14:42:57 0

0 电子发烧友网站提供《嵌入式多媒体系统中硬件加速技术的应用.pdf》资料免费下载

2023-10-26 09:33:35 0

0 思想是利用专门的硬件资源,如GPU或专用的解码芯片,来分担原本由CPU承担的解码任务。这种方式不仅可以大幅提高解码速度,还能降低CPU的负载,从而实现更流畅的播放效果。 硬件加速的优势 高效性能 :硬件解码器通常具有更高的解码速度

2024-02-21 14:40:48 192

192

电子发烧友App

电子发烧友App

评论