概述

此项目解释了如何在FPGA上使用resizer IP来调整图像的大小。其中对比了两种图像大小调整的解决方案的运算速度,其中之一为使用Python Image Library通过软件算法实现图像大小调整,另一种使用Xilinx xfopencv library实现了在FPGA上硬件加速的图像大小调整。

初始化

1. 首先在SD卡内配置Pynq-Z2最新镜像PYNQ image v2.5并烧录在其中

2. 根据pynq.io上的官方指南配置环境

(https://pynq.readthedocs.io/en/latest/getting_started/pynq_z2_setup.html)

根据数字编号依次连接并点亮板卡,最后在板卡出现BTN0~BTN3同时点亮闪烁一次后为开机完成状态。

3. 在笔记本电脑上配置网络,使得无线网卡的上网功能与Pynq-Z2连接的以太网网口共享,以做到Pynq-Z2同时能够上网。

4. 借用Xshell或者开源软件PuTTY对于Pynq-Z2端口进行SSH获得其新ip口,此时其一般会被重定向至192.168.137.X。此时在浏览器内登录此ip即可通过Jupyter Notebook与Pynq-Z2板卡通信。

5. 在Jupyter Notebook中新建terminal并ping 182.61.200.6验证与百度的连接是否正常上述验证完成后即为Pynq-Z2板卡与网络的基础通信功能与配置完成。

快速开始

在Jupyter Notebook的Terminal中输入以下指令:

sudo pip3 install --upgrade git+

https://github.com/xilinx/pynq-helloworld.git

更新在Pynq-Z2内所有Packages并从github下载本次项目的代码。

(更新需要耐心等待一定时间。)

(项目Github文件及其详细代码请点击查看原文)

案例测试

1. 最终会在Files文件夹下生成名为helloworld/的文件夹,点开此文件夹可以看到两个Jupyter Notebook文件(.ipynb)。

2. 其中resizer_PS.ipynb的软件方案采用了Python内建的Python Imaging Library通过软件上的算法实现完成对于一张640*360的sample图像压缩为原图像的四分之一大小(320*180)。此软件方案通过PIL库加载与重置图像的大小,用numpy库存储图像的像素矩阵,用IPython.display在Jupyter notebook中显示图像。

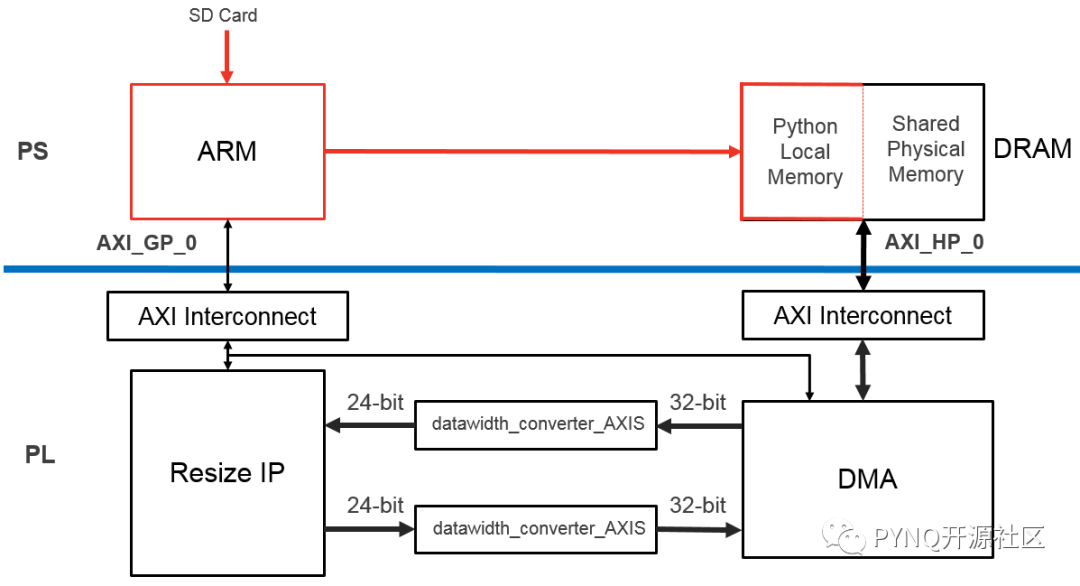

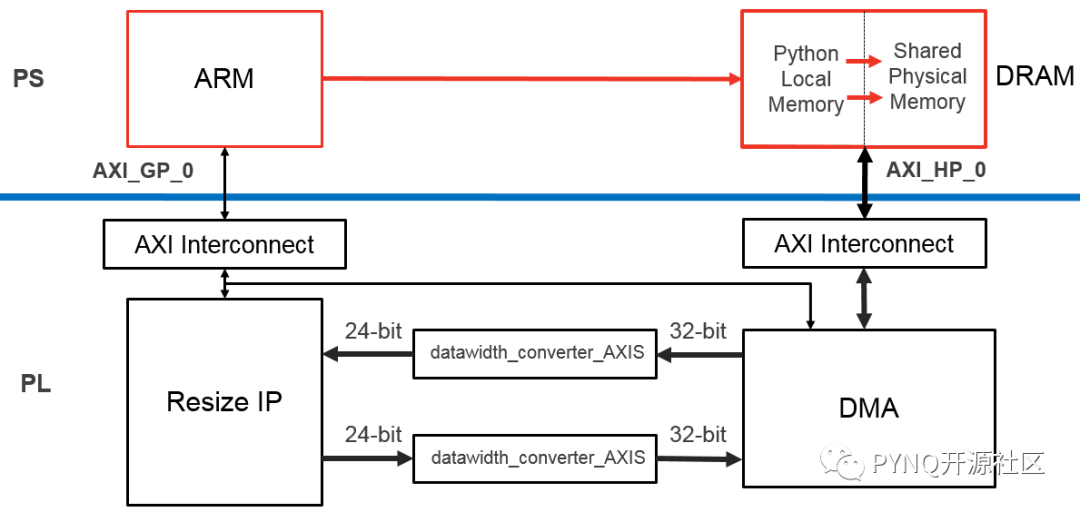

3. 而resizer_PL.ipynb的FPGA硬件方案并没有直接在ARM核中单纯采用算法借用Python本地的内存进行运算后直接返回。而是先将图片数据通过ARM核从SD卡中读入,再以数据流的形式通过Python的本地内存的DRAM形式传入共享的物理内存中。

最后,在缩小图片的演示最后我们可以看到PS方案得到的最快单次图像处理为24.1ms,而在PL方案中最快单次图像处理仅仅为8.95ms,在此实际图像案例上处理图像的时间效率上缩小了接近2.7倍。如果放至更多张更高像素的图片,相信此图像处理方案会有着较大优势。

-

FPGA

+关注

关注

1664文章

22537浏览量

640181 -

图像处理

+关注

关注

29文章

1352浏览量

59749 -

Xilinx

+关注

关注

73文章

2208浏览量

132086 -

python

+关注

关注

59文章

4891浏览量

90371

发布评论请先 登录

基于米尔安路飞龙派 MYD-YM90X开发板多功能智能车系统开发

新思科技2026 HAV硬件加速验证技术开放日深圳站圆满落幕

综合图像处理硬件平台设计资料:2-基于6U VPX的双TMS320C6678+Xilinx FPGA K7 XC7K420T的图像信号处理板

FPGA硬件加速卡设计原理图:1-基于Xilinx XCKU115的半高PCIe x8 硬件加速卡 PCIe半高 XCKU115-3-FLVF1924-E芯片

FPGA和GPU加速的视觉SLAM系统中特征检测器研究

常用硬件加速的方法

硬件加速模块的时钟设计

睿擎SDK V1.5.0重磅升级:EtherCAT低抖动,AMP虚拟网卡,LVGL硬件加速,多核调试等性能大幅提升|产品动态

如何验证硬件加速是否真正提升了通信协议的安全性?

有哪些方法可以确保硬件加速与通信协议的兼容性?

如何利用硬件加速提升通信协议的安全性?

【米尔MYC-YM90X安路飞龙DR1开发板】HMI人机界面开发

推动硬件辅助验证平台增长的关键因素

FPGA硬件加速的图像大小调整案例分析

FPGA硬件加速的图像大小调整案例分析

评论